目录

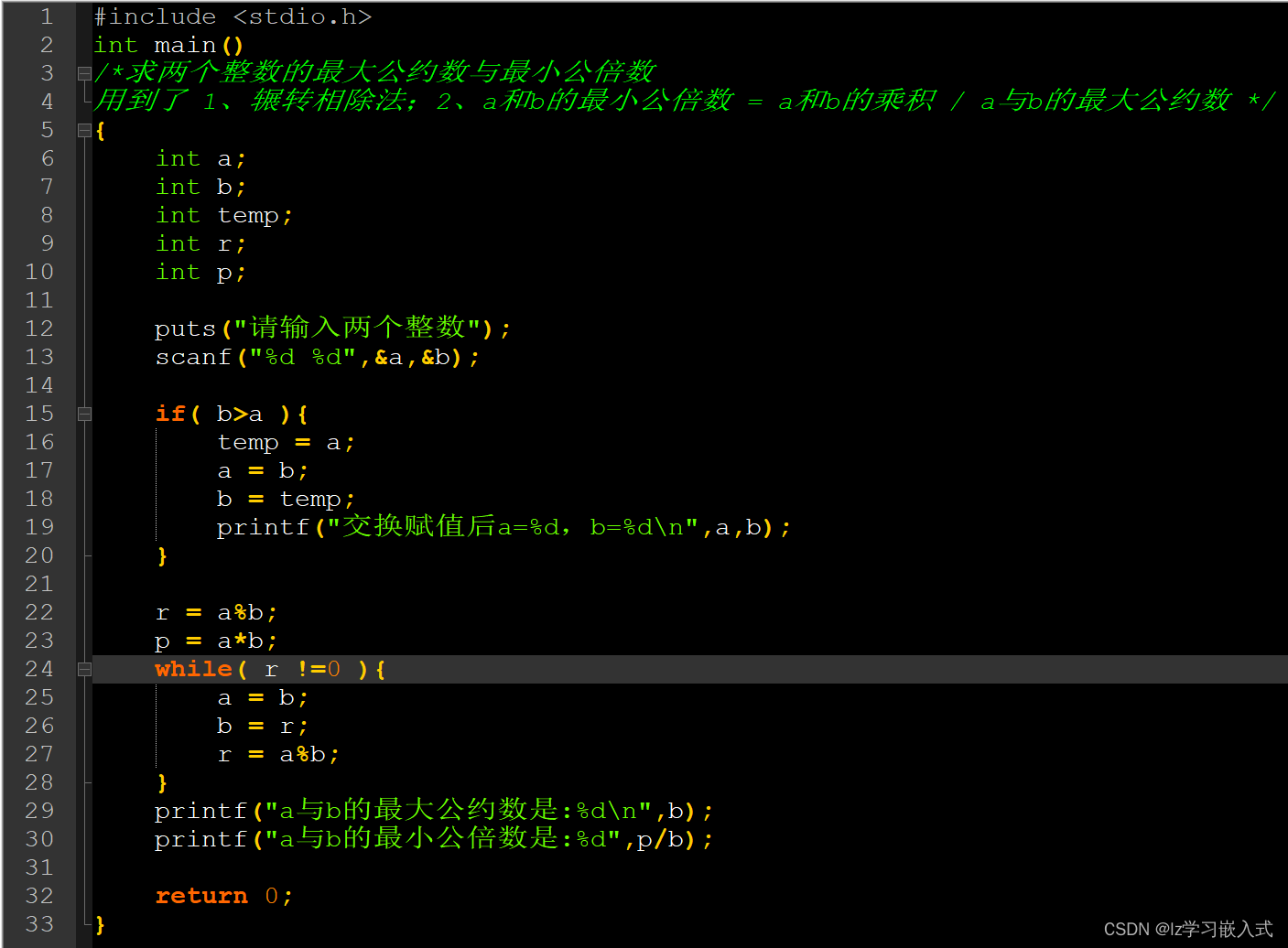

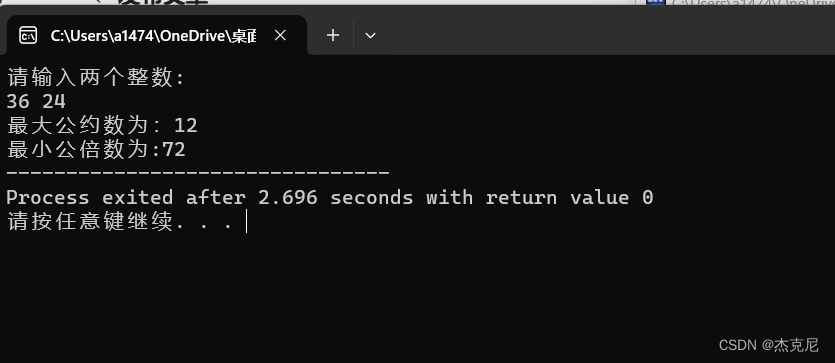

当前,FPGA设计在很多场合得到了广泛的应用,如集成电路设计、SoC开发等领域。常规的设计方法采用硬件描述语言或高级综合的方式对功能进行描述,优点是设计周期较短,便于调试,然而难以满足对性能要求较高的场合。因此,笔者尝试采用纯硬件电路的方式,针对基本的数学运算进行设计。本文为采用硬件电路实现最大公约数的求取算法。

一、设计需求

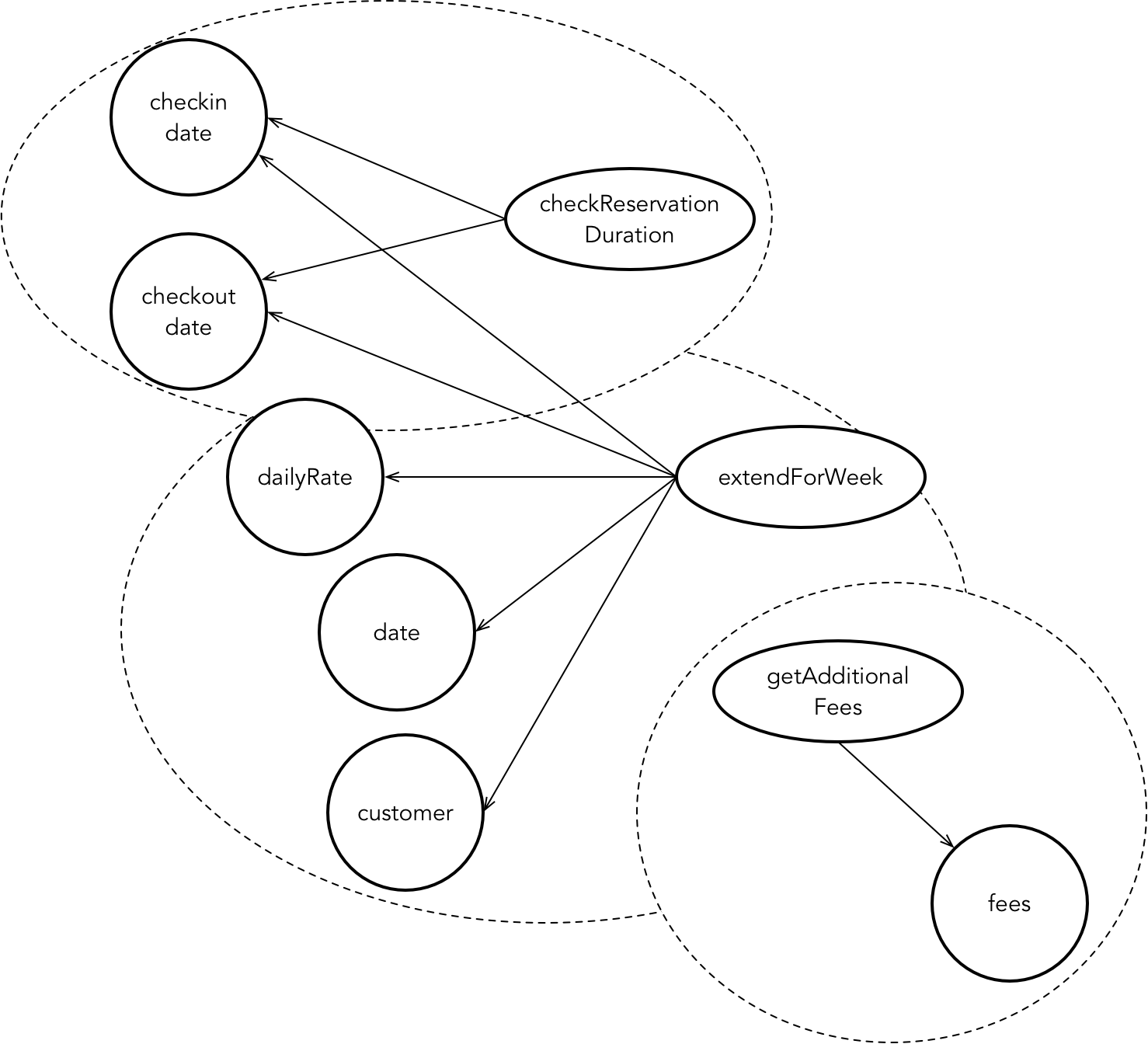

已知最大公约数的求取算法如下:A,B为非零正整数,A-B=C,C也是非零正整数,则A,B的最大公约数等于B,C的最大公约数。按照全定制FPGA的设计思路,不使用硬件描述语言或高级综合,直接设计实现该算法的硬件电路。(字长:32_bit)

二、设计工具及版本

Quartus II 8.1

![【sgCreateTableColumn】自定义小工具:敏捷开发→自动化生成表格列html代码(表格列生成工具)[基于el-table-column]](https://img-blog.csdnimg.cn/direct/1ce75f457fb24b5ba540809aedce0013.gif)

![[经验] 天猫盒子怎么投屏手机照片 #经验分享#其他#经验分享](https://img-home.csdnimg.cn/images/20230724024159.png?origin_url=https%3A%2F%2Fwww.hao123rr.com%2Fzb_users%2Fcache%2Fly_autoimg%2F%25E5%25A4%25A9%25E7%258C%25AB%25E7%259B%2592%25E5%25AD%2590%25E6%2580%258E%25E4%25B9%2588%25E6%258A%2595%25E5%25B1%258F%25E6%2589%258B%25E6%259C%25BA%25E7%2585%25A7%25E7%2589%2587.jpg&pos_id=A4SDL2Lz)