实验目的

- 掌握使用Vivado软件进行设计、综合、仿真、布线的方法。

- 掌握FPGA程序的下载方法。

- 掌握使用Verilog HDL设计加法器的方法。

实验要求

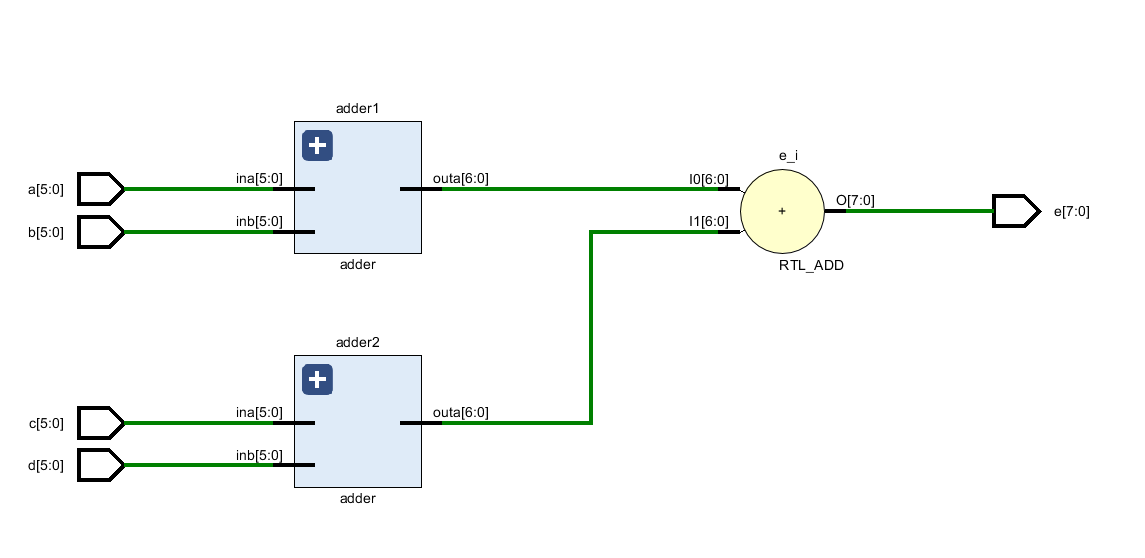

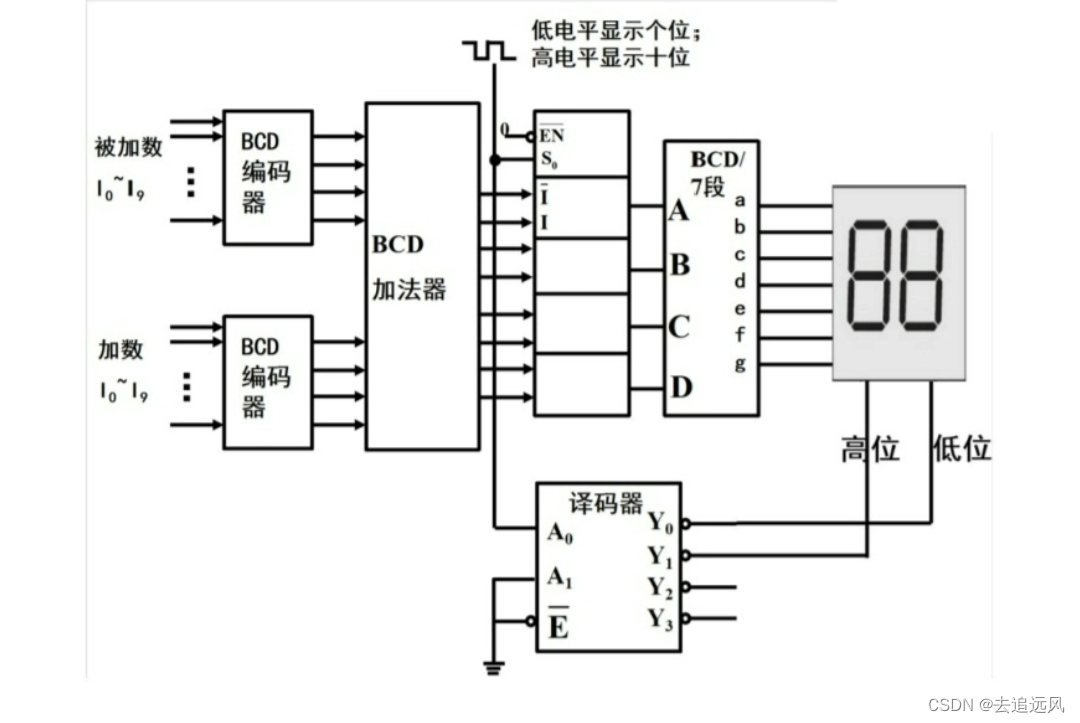

采用Verilog HDL语言设计加法器,实现两个4位数的相加运算,并将结果通过LED灯或数码管显示出来。对设计进行综合、仿真、布线、下载和测试。

实验过程

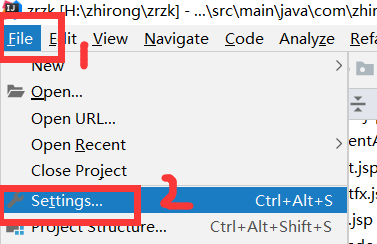

- 打开Vivado软件,新建一个工程。

- 新建设计文件,使用Verilog HDL语言设计程序,实现加法器。

代码如下:

so easy 的一个代码

module adder(

input wire[3:0] a,

input wire[3:0] b,

output reg[4:0]ans

);

always@(*)begin

ans=a+b;

end

endmodule

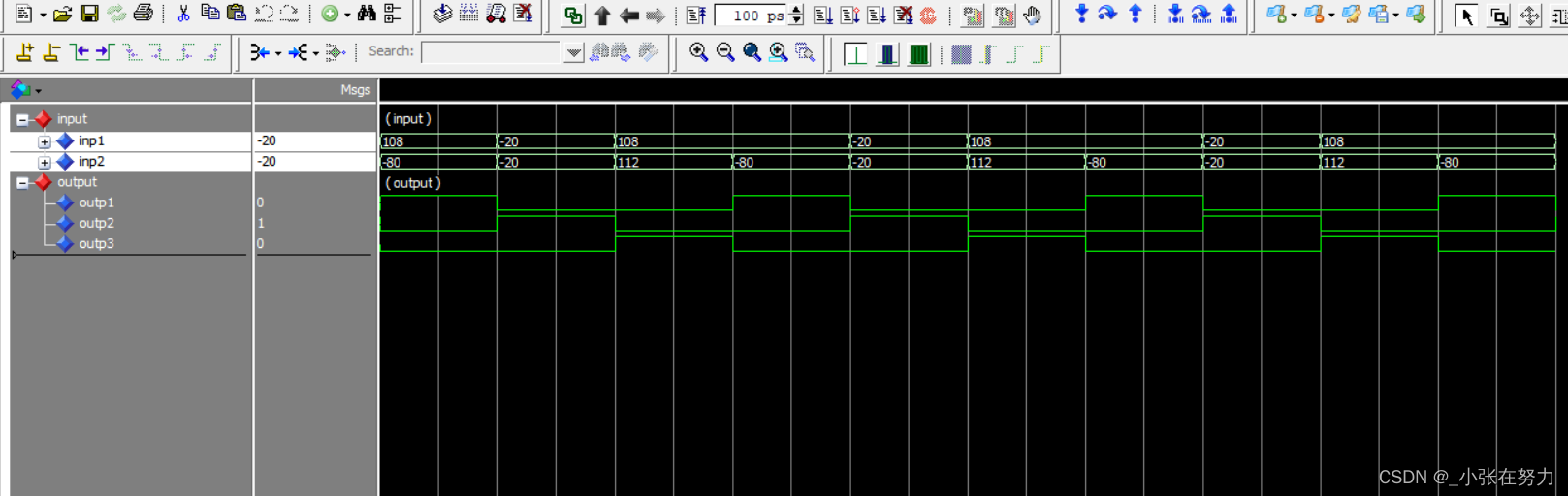

仿真代码:

`timescale 1ns / 1ps

module adder_tb;

reg [3:0] a;

reg [3:0] b;

wire [4:0]ans;

initial

begin

a=1;

b=2;

#10 a=5;

#20 b=6;

#50 a=7;

end

adder addt(

.a(a),

.b(b),

.ans(ans)

);

endmodule

实验结果

通过八位拨动开关实现a,b的承载,结果用led显示,注意的是led灯是低电平有效,当时没搞清楚导致找不到原因

引脚绑定看我的实验一

总结

无

![[Verilog] <span style='color:red;'>加法器</span><span style='color:red;'>实现</span>](https://img-blog.csdnimg.cn/direct/5a6e645cba2e49e8a0cdcf1883984cb1.png)

![[C++]TinyWebServer](https://i-blog.csdnimg.cn/direct/64132595aa8544d7a33ce90667c11bc0.png)