实验目的及要求

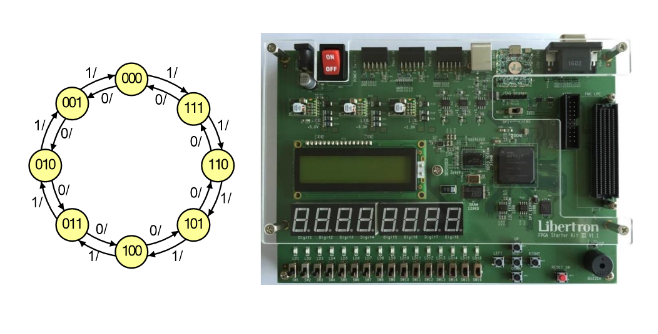

- 掌握时钟信号、进程和BUFFER端口的运用;

- 了解计数器的设计、仿真和硬件测试,进一步熟悉VHDL语句、语法及应用等。

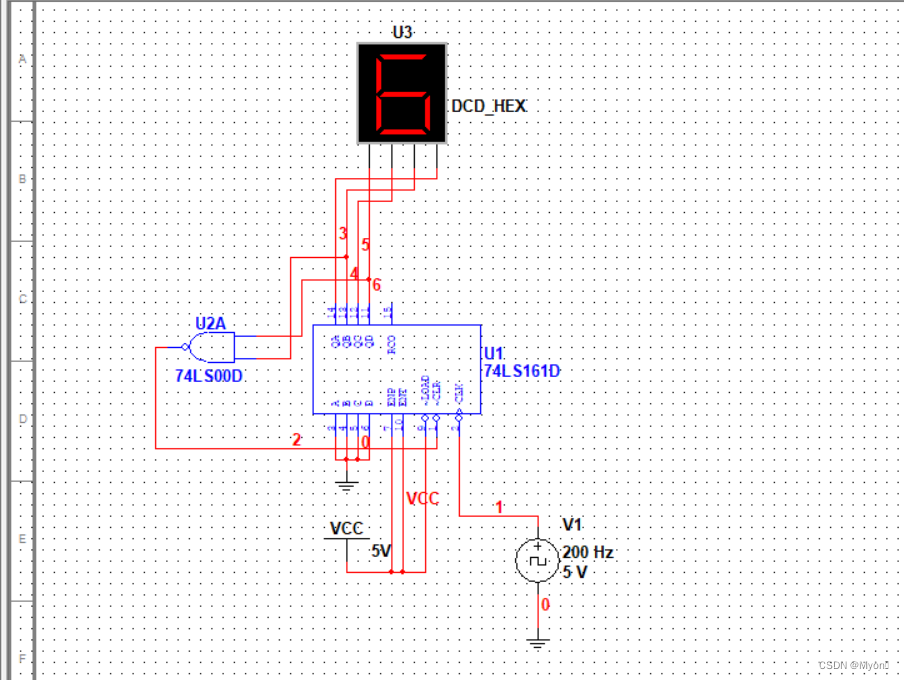

实验原理

运用Quartus II 集成环境下的VHDL文本设计方法设计4位加法计数器,进行波形仿真和分析、引脚分配并下载到实验设备上进行功能测试。

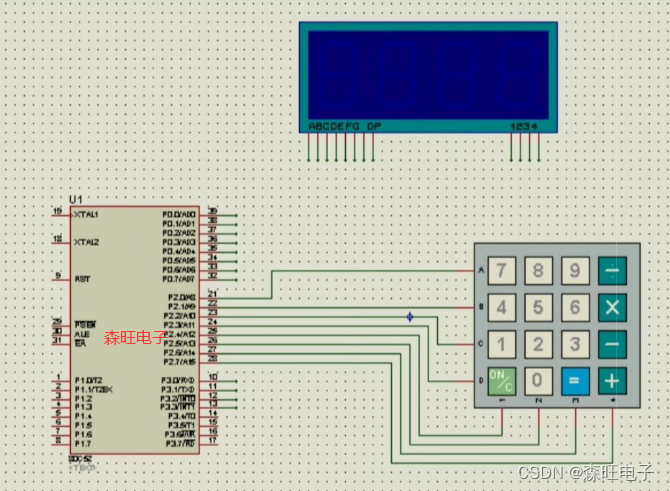

实验内容和步骤

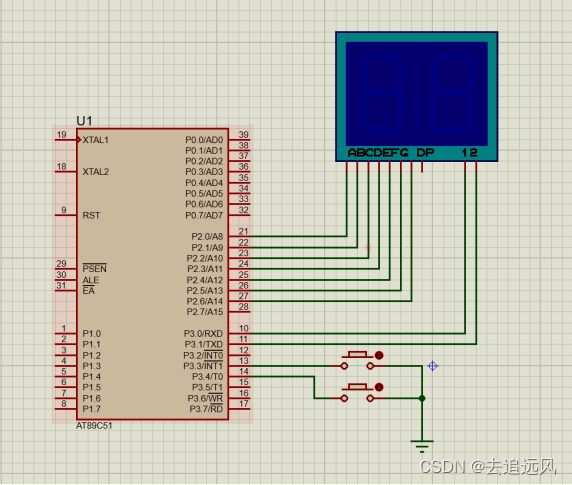

实验步骤和方法参考实验一,引脚分配可参考下表。

引脚名称 |

引脚编号 |

连接网络 |

引脚名称 |

引脚编号 |

连接网络 |

clk |

PIN_T10 |

KEY1 |

q[2] |

PIN_N15 |

LED2 |

q[0] |

PIN_R11 |

LED4 |

q[3] |

PIN_R10 |

LED1 |

q[1] |

PIN_U11 |

LED3 |

实验代码

![设计模式学习[2]---策略模式+简单工厂回顾](https://i-blog.csdnimg.cn/direct/9fc1741c1038448ebeda1f2001335763.jpeg)