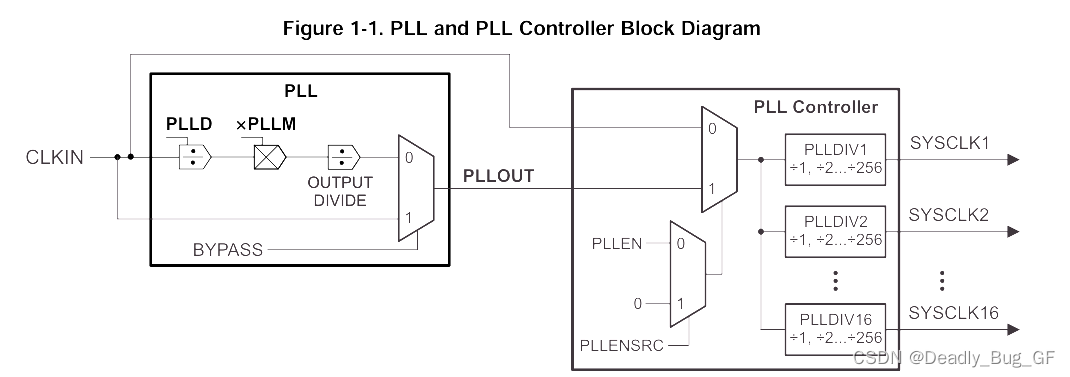

(1)PLL IP核的简介:

Phase Locked Loop,即锁相环,是最常用的IP核之一,其性能强大,可以对输入到FPGA的时钟信号进行任意分频、倍频、相位调整、占空比调整,从而输出一个期望时钟。锁相环分为两种锁相环:模拟锁相环、数字锁相环。模拟锁相环相比较数字锁相环性能更优,但温度过高,容易失锁。

FD:鉴频 PD:鉴相

LF:环路滤波器(滤除高频噪声) VCO:压控振荡器(电压越高,生成的信号频率越高)

DIV:分频器

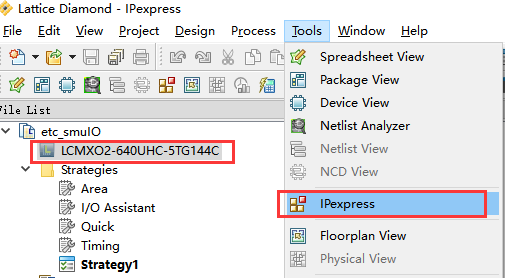

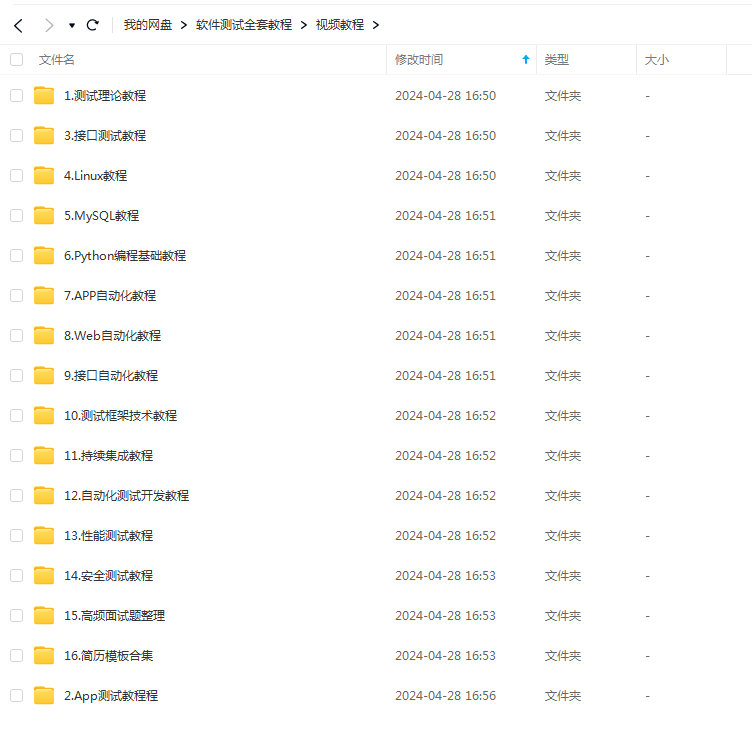

(2)PLL在Vivado软件中的配置过程:

CMT:时钟管理器 A7中有24个时钟管理器,MMCM包含PLL所有功能,还能实现一些额外的功能,可以输出差分信号,可以实现精确相位信号的输出。

查找IP核:

输入信号的配置:

板卡晶振为50MHz

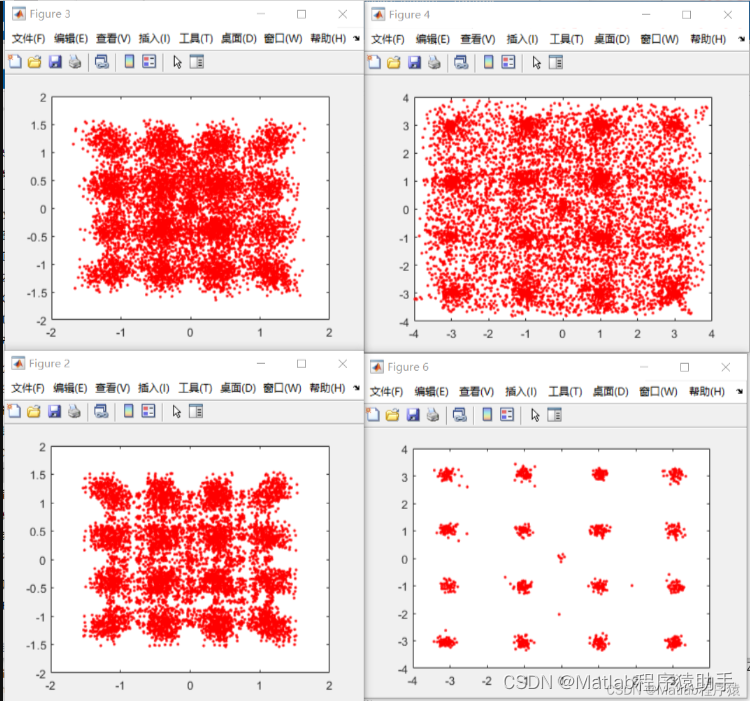

输出信号的设置:

第一路信号为100MHz,相位与占空比与输入信号保持一致。

第二路信号为25MHz,相位与占空比与输入信号保持一致。

第三路信号为100MHz,但相位相比较输入信号偏移90°。

第四路信号为100MHz,但占空比降低为20%。

复位信号可以取消:

点击ok之后,跳转到生成IP界面:

veo文件中有可以例化的模板:

(3)PLL在Vivado软件中的调用:

(4)PLL仿真代码:

`timescale 1ns / 1ps

module pll_tb;

reg clk ;

wire clk_100M ;

wire clk_25M ;

wire clk_s_90 ;

wire clk_d_20 ;

wire locked ;

pll pll_inst(

.clk (clk ),

.clk_100M (clk_100M ),

.clk_25M (clk_25M ),

.clk_s_90 (clk_s_90 ),

.clk_d_20 (clk_d_20 ),

.locked (locked )

);

initial clk = 1'd1;

always #10 clk = ~clk;

endmodule(5)仿真波形: