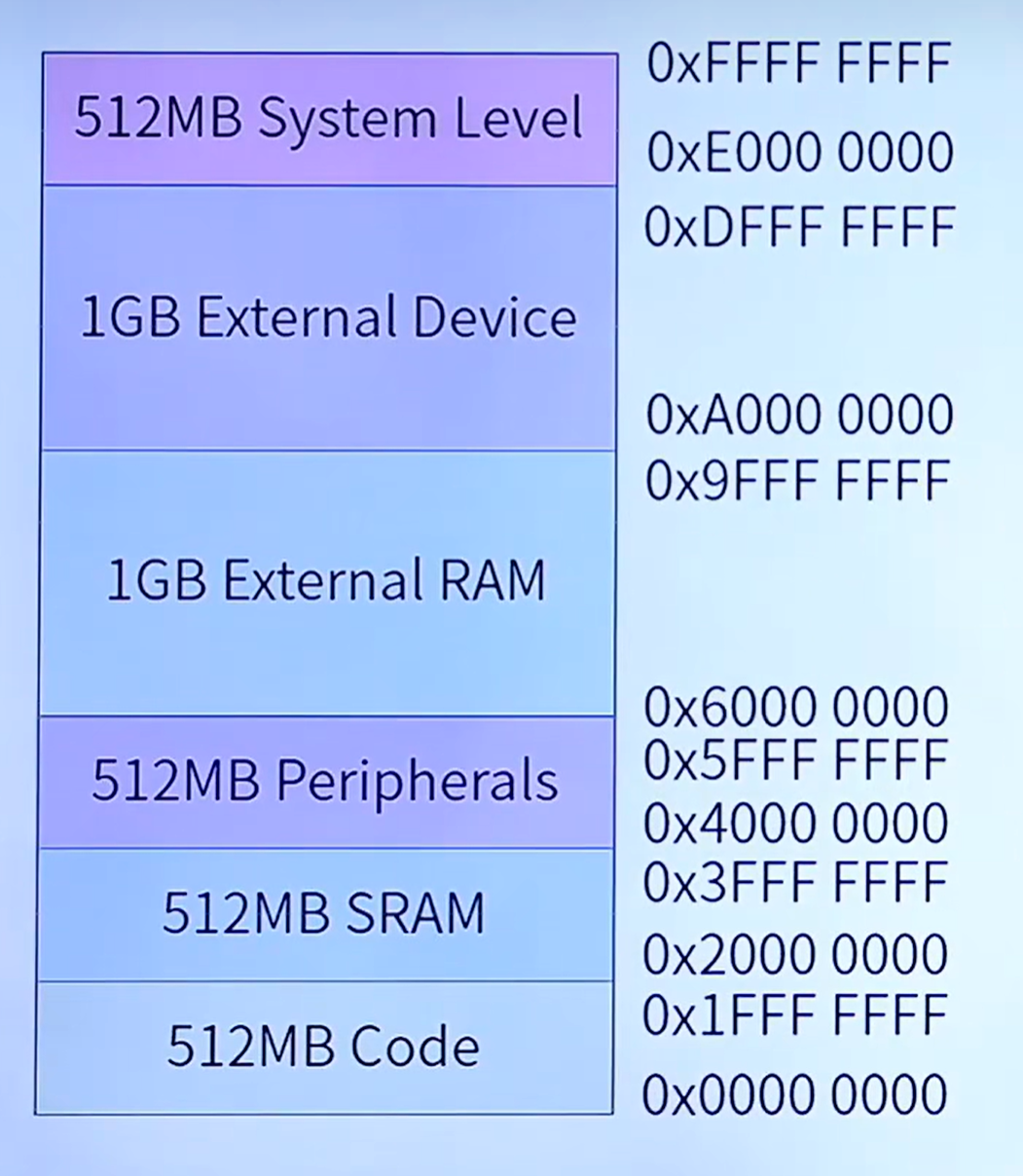

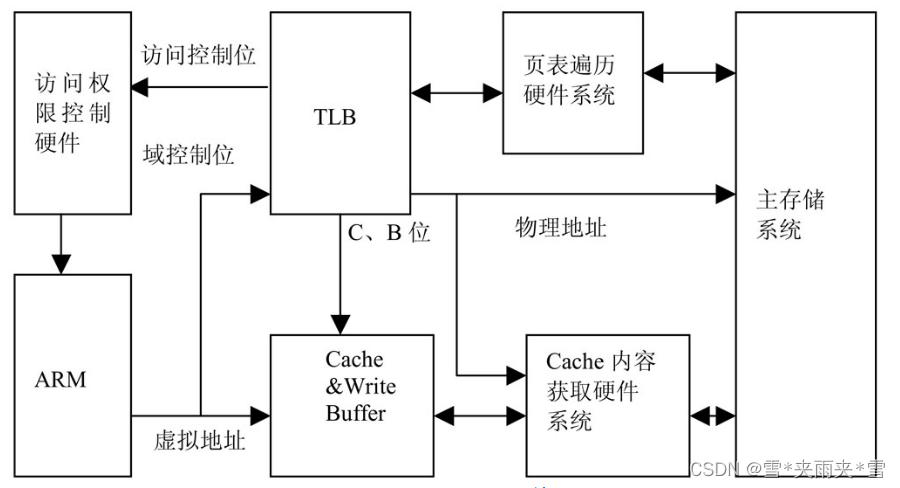

在ARM系统中,存储器管理单元MMU主要完成以下工作:

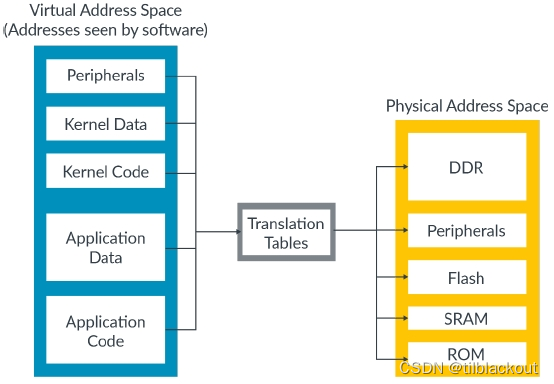

● 虚拟存储空间到物理存储空间的映射。在ARM中采用了页式虚拟存储管理。它把虚拟地址空间分成一个个固定大小的块,每一块称为一页,把物理内存的地址空间也分成同样大小的页。页的大小可以分为粗粒度和细粒度两种。MMU就要实现从虚拟地址到物理地址的转换。

● 存储器访问权限的控制。

● 设置虚拟存储空间的缓冲的特性。

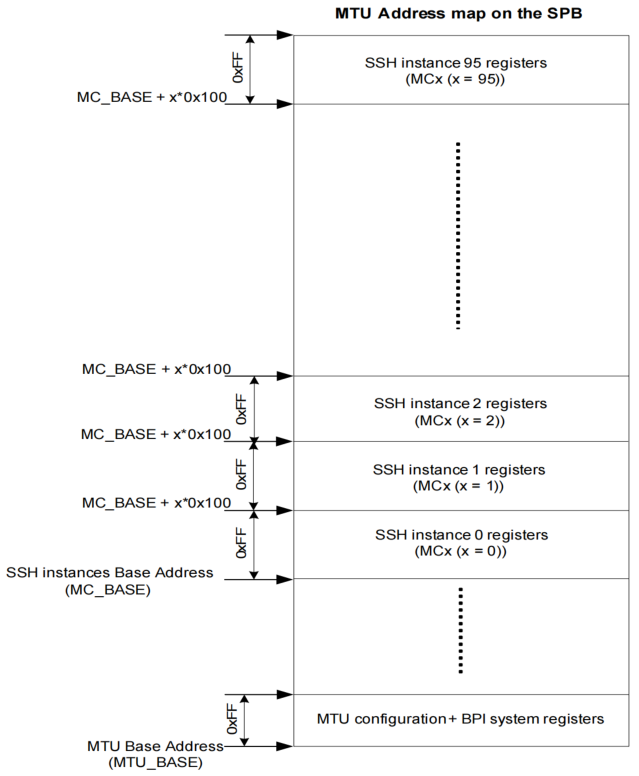

页表(Translate Table)是实现上述这些功能的重要手段,它是一个位于内存中的表。表的每一行对应于虚拟存储空间的一个页,该行包含了该虚拟内存页(称为虚页)对应的物理内存页(称为实页)的地址、该页的访问权限和该页的缓冲特性等。这里将页表中这样的一行称为一个地址变换条目(Entry)。

页表存放在内存中,系统通常用一个寄存器来保存页表的基地址。在ARM中,系统控制协处理器CP15的寄存器C2用来保存页表的基地址。

从虚拟地址到物理地址的变换过程其实就是查询页表的过程,由于页表存放在内存中,这个查询过程通常代价很大。而程序在执行过程中具有局部性,因此,对页表中各存储器的访问并不是完全随机的。也就是说,在一段时间内,对页表的访问只是局限在少数几个单元中。根据这一特点,采用一个容量更小(通常为8~16个字)、访问速度和CPU中通用寄存器相当的存储器件来存放当前访问需要的地址变换条目。这个小容量的页表称为快表。快表在英文资料中被称为TLB(Translation Lookaside Buffer)。

当CPU需要访问内存时,先在TLB中查找需要的地址变换条目。如果该条目不存在,CPU从位于内存中的页表中查询,并把相应的结果添加到TLB中。这样,当CPU下一次又需要该地址变换条目时,就可以从TLB中直接得到了,从而使地址变换的速度大大加快。

当内存中的页表内容改变,或者通过修改系统控制协处理器CP15的寄存器C2使用新的页表时,TLB中的内容需要全部清除。MMU提供了相关的硬件支持这种操作。系统控制协处理器CP15的寄存器C8用来控制清除TLB内容的相关操作。

MMU可以将某些地址变换条目锁定(Locked Down)在TLB中,从而使得进行与该地址变换条目相关的地址变换速度保持很快。在MMU中,寄存器C10用于控制TBL内容的锁定。

MMU可以将整个存储空间分为最多16个域(Domain)。每个域对应一定的内存区域,该区域具有相同的访问控制属性。MMU中,寄存器C3用于控制与域相关的属性的配置。

当存储访问失效时,MMU提供了相应的机制用于处理这种情况。在MMU中,寄存器C5和寄存器C6用于支持这些机制。

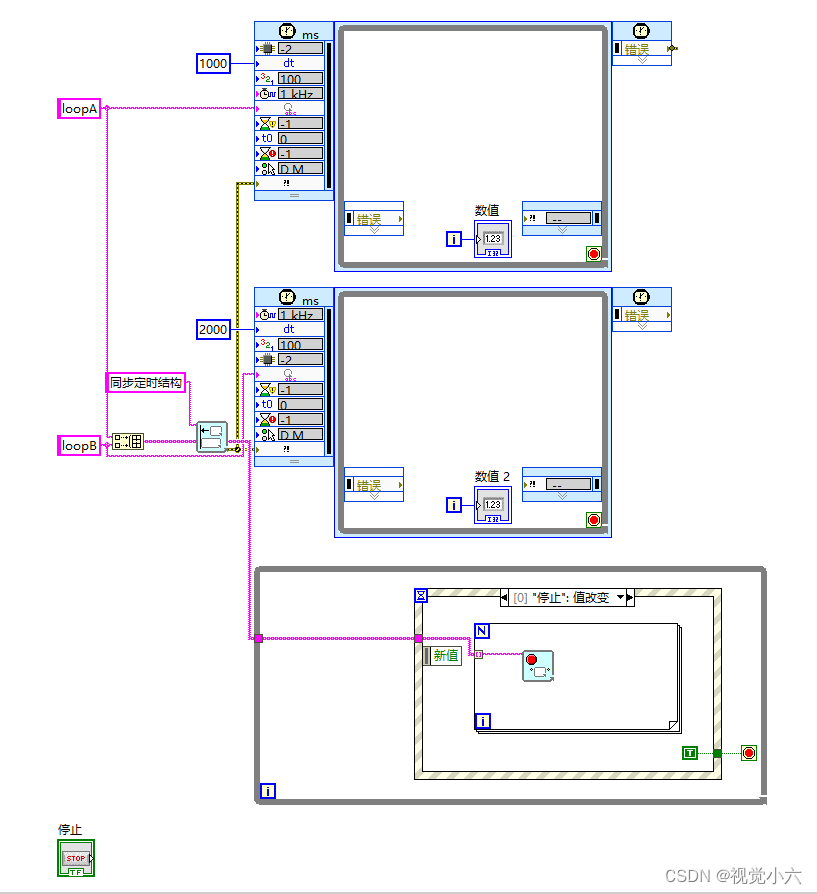

使能MMU时存储访问过程

当ARM处理器请求存储访问时,首先在TLB中查找虚拟地址。如果系统中数据TLB和指令TLB是分开的,在取指令时,从指令TLB查找相应的虚拟地址,对于其他的内存访问操作,从数据TLB中查找相应的虚拟地址。

如果该虚拟地址对应的地址变换条目不在TLB中,CPU从位于内存中的页表中查询对应于该虚拟地址的地址变换条目,并把相应的结果添加到TLB中。如果TLB已经满了,还需要根据一定的淘汰算法进行替换。这样,当CPU下一次又需要该地址变换条目时,可以从TLB中直接得到,从而使地址变换的速度大大增加。

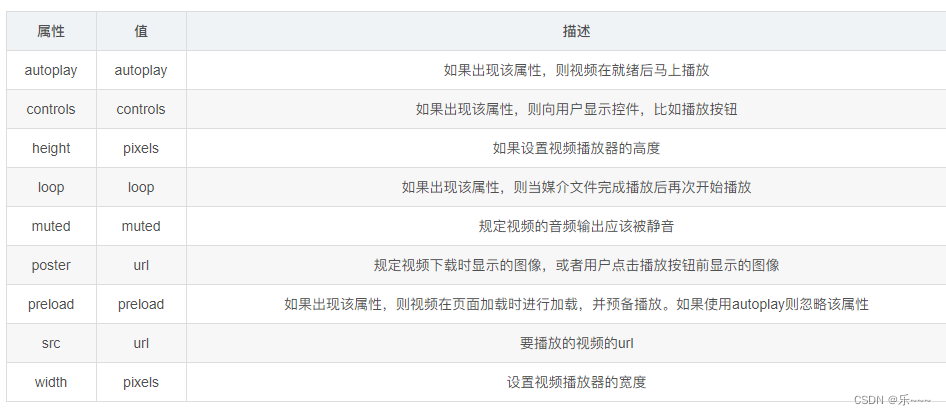

当得到了需要的地址变换条目后,将进行以下的操作。

(1)得到该虚拟地址对应的物理地址。

(2)根据条目中的C(Cacheable)控制位和B(Bufferable)控制位决定是否缓存该内存访问的结果。

(3)根据存取权限控制位和域访问控制位确定该内存访问是否被允许。如果该内存访问不被允许,CP15向ARM处理器报告存储访问中止。

(4)对于不允许缓存(Uncached)的存储访问,使用步骤(1)中得到的物理地址访问内存。对于允许缓存(Cached)的存储访问,如果Cache命中,则忽略物理地址;如果Cache没有命中,则使用步骤(1)中得到的物理地址访问内存,并把该块数据读取到Cache中。

允许缓存(Cached)的MMU存储访问示意图:

![[<span style='color:red;'>MMU</span>]现代计算机内存<span style='color:red;'>管理</span>](https://img-blog.csdnimg.cn/img_convert/10b5eeadfceb3aae1eb2a6ad1f373689.png)