文章目录

- 一、按键中断实验

- 二、按键中断实验分析

-

- (一)查看所有外设的总线以及寄存器基地址

- (二)RCC章节

- (三)GPIO章节

- (四)EXTI:扩展中断控制器

- (五)GIC:全局中断控制器

-

- 1. GICD_CTLR : GICD control register

- 2. GICD_ISENABLERx : GICD interrupt set-enable register x

- 3. GICD_IPRIORITYRx :GICD interrupt priority register x

- 4. GICD_ITARGETSRx :GICD interrupt processor target register x

- 5. GICD_ICPENDRx :GICD interrupt clear-pending register x

- -------------------------------------------------------------

- 1. GICC_CTLR :GICC control register

- 2. GICC_PMR : GICC input priority mask register

- 3. GICC_IAR :GICC interrupt acknowledge register

- 4. GICC_EOIR :GICC end of interrupt register

- 三、

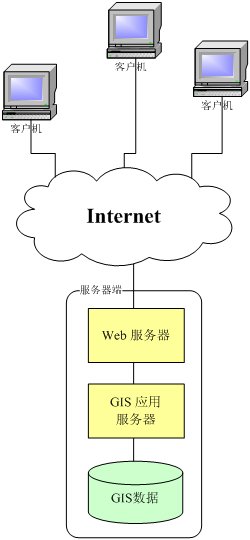

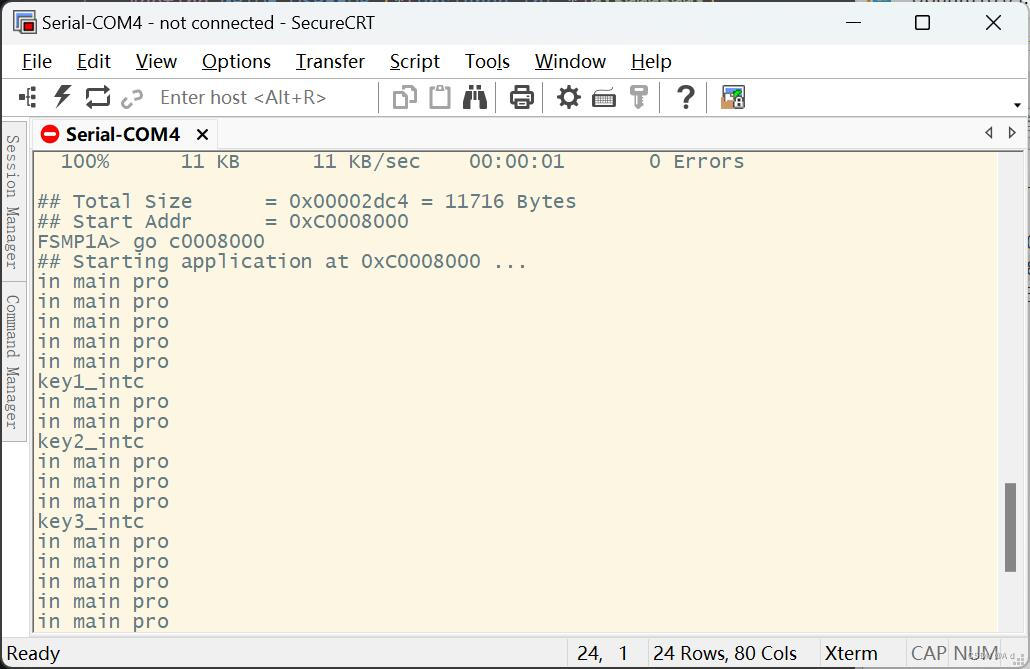

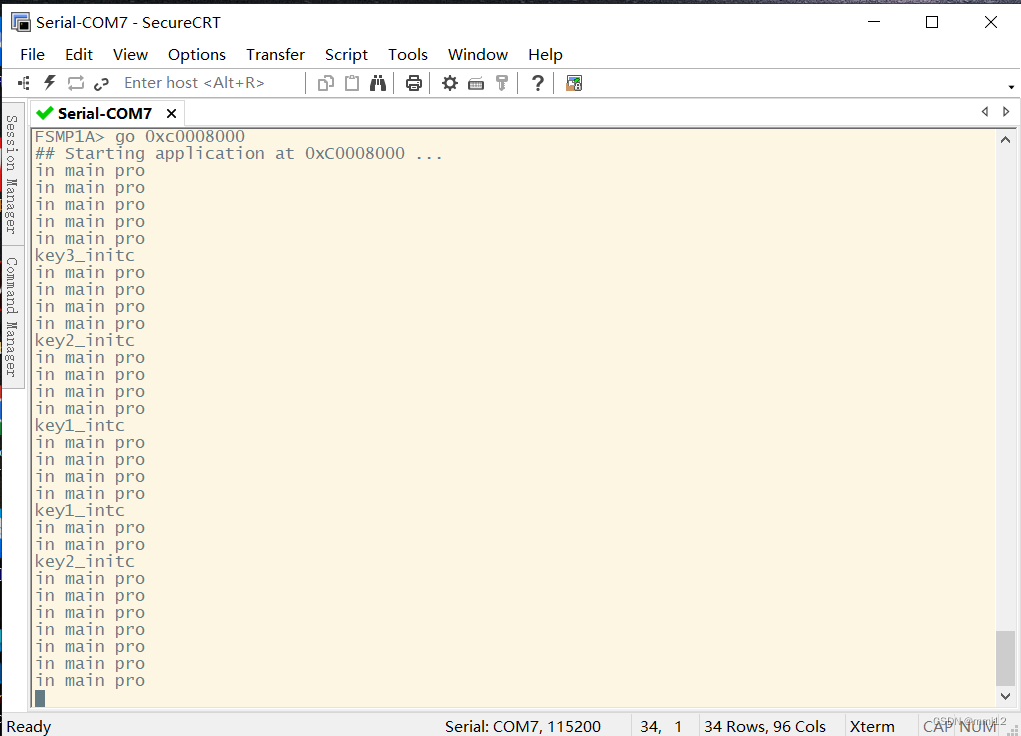

一、按键中断实验

(一)分析按键电路图

(二)芯片手册

二、按键中断实验分析

- 注:NVIC----Cortx-M核

- GIC----Cortx-A核

(一)查看所有外设的总线以及寄存器基地址

- 注:GIC的总线是A7核的内部总线,也就是说,它是由ARM公司完成的

- 注:EXTI的时钟源无需手动使能,它一直是使能状态

(二)RCC章节

只需要使能GPIOF的时钟源即可

(三)GPIO章节

将PF9设置为输入模式

(四)EXTI:扩展中断控制器

扩展中断和事件控制器(EXTI)通过可配置和直接的事件输入来管理单个CPU和系统唤醒。它为电源控制提供唤醒请求,并向CPU的NVIC生成中断请求以及向CPU的事件输入生成事件。对于每个CPU,需要一个额外的事件生成块(EVG)来生成CPU事件信号。

EXTI唤醒请求允许系统从STOP模式唤醒,并且允许CPU从CSTOP和CSTANDBY模式唤醒。

中断请求和事件请求生成也可以在RUN模式下使用。

EXTI还包括EXTI多路复用I/O端口选择。

EXTI由通过AHB接口访问的寄存器块、事件输入触发块、屏蔽块和EXTI多路复用器组成。

寄存器块包含所有EXTI寄存器。

事件输入触发块提供事件输入边沿触发逻辑。

屏蔽块提供事件输入到不同唤醒、中断和事件输出的分配,以及这些输出的屏蔽功能。

EXTI多路复用器为EXTI事件信号提供I/O端口选择。

其中,CPU1代表MPU(主处理器单元),而CPU2代表MCU(微控制器单元)。

1. EXTI多路复用IO端口选择

1. EXTI_FTSR1寄存器

注:EXTI最多支持76个输入的事件,EXTI_FTSR寄存器的每1个bit位配置1个输入的事件,一个寄存器最多配置32个,因此至少需要三个EXTI_FTSR寄存器。

注:KEY1 --> PF9 --> EXTI9 --> EXTI9对应的输入事件的编号,

查看21.3章节的表118,查看EXTI9对应的输入事件的编号

2. EXTI_FPR1寄存器

读:判读下降沿中断是否发生

读0 : 表示没有下降沿触发中断请求发生

读1 : 表示有下降沿触发中断请求发生

写:清除中断挂载标志位(需要程序员手动清除)

写0:没有意思

写1:清除下降沿挂载标志位

3. EXIT_EXTI3寄存器

4. EXTI_C1IMR1寄存器

(五)GIC:全局中断控制器

1. GICD_CTLR : GICD control register

GICD层全局控制使能寄存器

2. GICD_ISENABLERx : GICD interrupt set-enable register x

GICD层中断设置使能寄存器

每个寄存器管理32个事件,每一位对应一个事件

使用事件号/32=商...余数,商就是寄存器编号,余数就是位数

- 注:无需加1,因为寄存器编号就是从0开始的

中断号:

3. GICD_IPRIORITYRx :GICD interrupt priority register x

GICD层中断优先级寄存器,设置中断的优先级,编号越小中断优先级越高

GICD_IPRIORITYRx寄存器每5个bit位管理一个中断号。而GIC支持16个SGIs, 16个PPIs,

256个SPIs,共计288个中断号。GICD_IPRIORITYRx寄存器每一个寄存器最多管理4个中断号,

要想管理288个中断号,最少需要72(288 / 4 = 72)个寄存器

问题2:KEY1 --> PF9 --> EXTI9 --> 中断号99号

99号中断对应GICD_IPRIORITYRx寄存器的哪1个,哪5位?

中断号 / 4 = 商 ...... 余数

| |---> (余数 * 8 + 3)对应寄存器5位中的最低位

|---> 寄存器的编号

99 / 4 = 24 ...... 3

GICD_IPRIORITYR24[31:27]位 配置99号中断的优先级,

优先级的范围:0-31

优先级的编号越小中断的优先级越高。

4. GICD_ITARGETSRx :GICD interrupt processor target register x

GICD层中断处理器目标分配寄存器,将中断信号转发给哪个CPU接口

GICD_ITARGETSRx寄存器每2个bit位管理一个中断号。而GIC支持16个SGIs, 16个PPIs,

256个SPIs,共计288个中断号。GICD_ITARGETSRx寄存器每一个寄存器最多管理4个中断号,

要想管理288个中断号,最少需要72(288 / 4 = 72)个寄存器

问题2:KEY1 --> PF9 --> EXTI9 --> 中断号99号

99号中断对应GICD_ITARGETSRx寄存器的哪1个,哪2位?

中断号 / 4 = 商 ...... 余数

| |---> (余数 * 8)对应寄存器5位中的最低位

|---> 寄存器的编号

99 / 4 = 24 ...... 3

GICD_ITARGETSR24[25:24]位 配置99号中断的目标处理,

0b01 : 分配中断给CPU0接口

0b10 : 分配中断给CPU1接口

5. GICD_ICPENDRx :GICD interrupt clear-pending register x

GICD层中断清除挂起寄存器,判读中断是否发生,清除中断挂起标志位

每一个bit位管理一个中断号,GIC支持16个SGIs,和256个SPIs,共计288个中断号。每个寄存器最多管理32个中断号,因此最少需要9个寄存器。

问题2:KEY1 --> PF9 --> EXTI9 --> 中断号99号

99号中断对应GICD_ICPENDRx寄存器的哪1个,哪1位?

中断号 / 32 = 商 ...... 余数

| |---> 寄存器对应的位

|---> 寄存器的编号

99 / 32 = 3 ...... 3

GICD_ICPENDR3[3]位 配置99号中断,

读0:zho

写1:使能中断

写0:没有影响

-------------------------------------------------------------

1. GICC_CTLR :GICC control register

GICC层全局中断控制使能寄存器

2. GICC_PMR : GICC input priority mask register

GICC输入中断优先级屏蔽寄存器。根据中断的优先级对中断进行屏蔽

3. GICC_IAR :GICC interrupt acknowledge register

GICC层中断应答寄存器,获取当前应答的中断的中断号,每个中断都有一个唯一的中断号。

4. GICC_EOIR :GICC end of interrupt register

GICC层中断结束寄存器,清除中断号

三、

![[经验] 驰这个汉字的拼音是什么 #学习方法#其他#媒体](https://img-home.csdnimg.cn/images/20230724024159.png?origin_url=https%3A%2F%2Fwww.hao123rr.com%2Fzb_users%2Fcache%2Fly_autoimg%2Fn%2FNzc1MzA.jpg&pos_id=f8V9JvdT)