随着电子技术的快速发展,现场可编程门阵列(FPGA)已成为现代电子系统设计中不可或缺的一部分。FPGA的灵活性、可重构性和高性能使得它成为处理复杂算法、加速数据处理和实现特定功能的理想选择。然而,随着系统复杂性的增加,FPGA设计也面临着诸多挑战,如设计复杂性、可维护性和可重用性等。因此,采用模块化设计方法成为提高FPGA设计效率和质量的关键。

一、FPGA模块化设计的概念

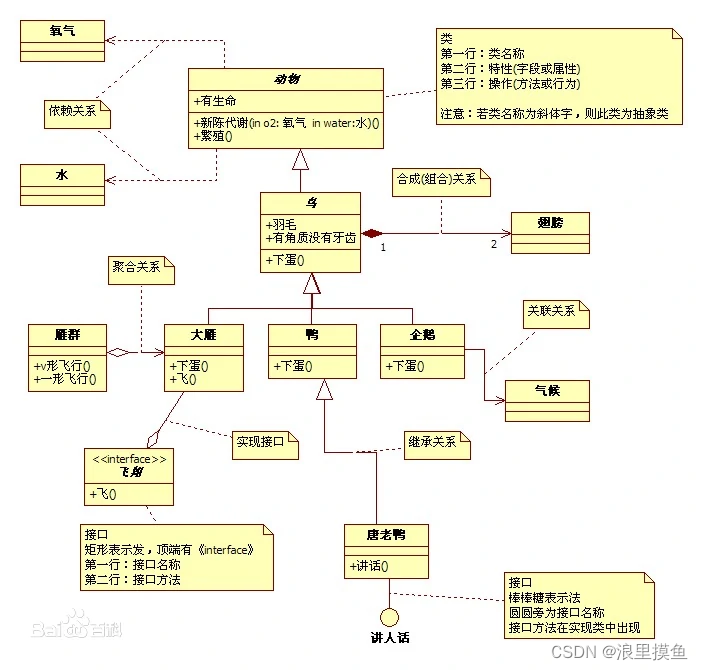

FPGA模块化设计是一种将复杂的FPGA设计分解为多个独立、可重用的模块的方法。每个模块都具有明确的功能和接口,可以单独设计、测试和优化,然后组合成一个完整的FPGA系统。模块化设计不仅降低了设计的复杂性,还提高了设计的可维护性和可重用性。

二、FPGA模块化设计的优势

降低设计复杂性:通过将FPGA设计分解为多个小模块,每个模块都具有相对简单的功能和结构,从而降低了设计的复杂性。这有助于减少设计错误和提高设计效率。

提高可维护性:模块化设计使得每个模块都具有明确的功能和接口,便于单独测试和维护。当系统出现问题时,可以快速定位到具体的模块,并进行针对性的修复和优化。

提高可重用性:模块化的设计使得模块可以在不同的FPGA项目中重用,从而减少了设计时间和成本。此外,模块还可以根据需要进行定制和扩展,以满足不同项目的需求。

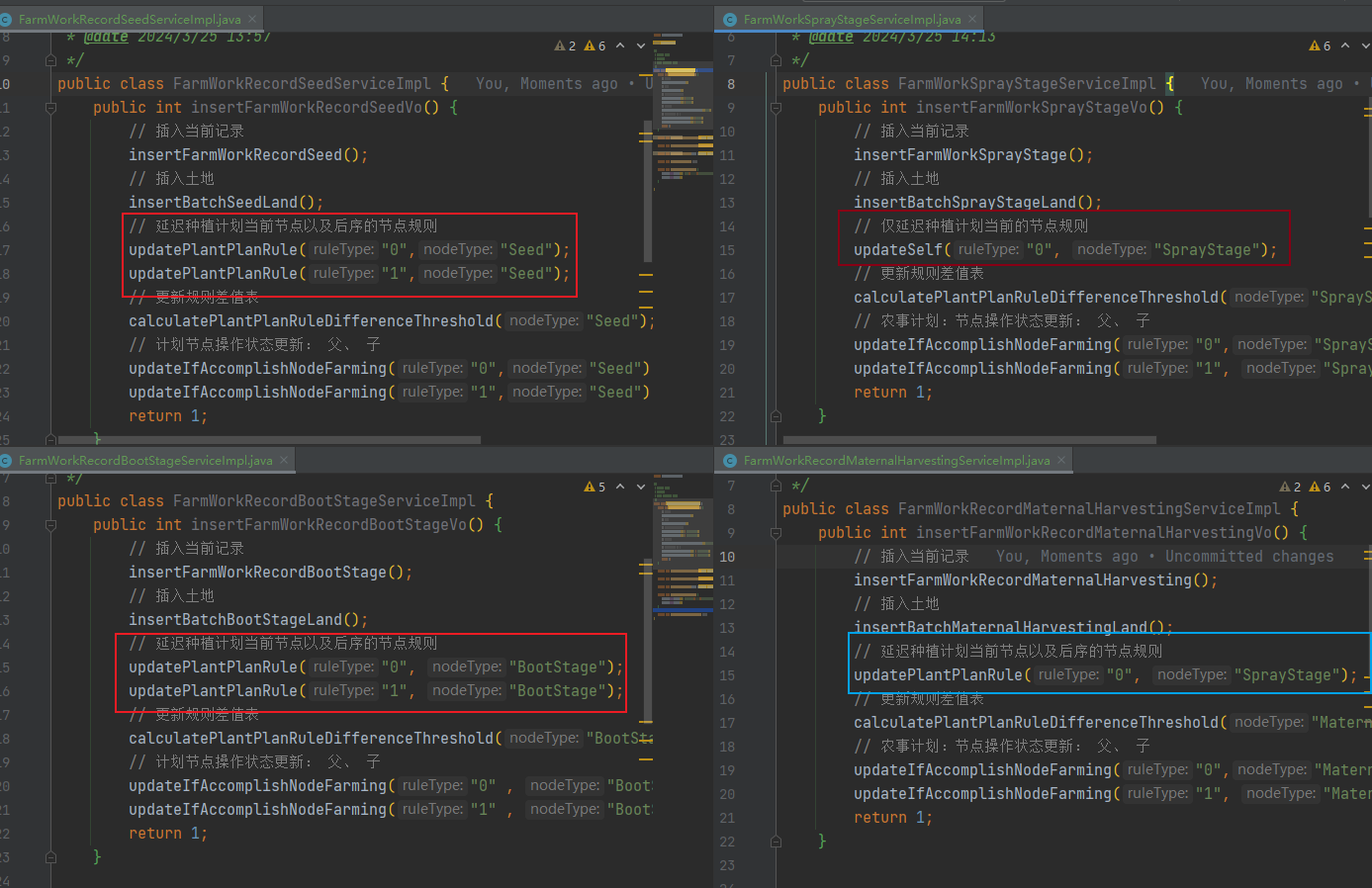

便于团队协作:模块化设计使得不同团队可以并行开发不同的模块,提高了团队协作的效率。同时,每个团队都可以专注于自己擅长的领域,从而提高了设计的质量和可靠性。

三、FPGA模块化设计的步骤

需求分析:明确FPGA系统的功能需求、性能指标和接口要求,为后续的设计提供指导。

模块划分:根据需求分析的结果,将FPGA设计划分为多个独立的模块。每个模块应具有明确的功能和接口,并尽可能保持模块之间的低耦合度。

模块设计:对每个模块进行详细的设计,包括模块的功能、接口、内部逻辑和时序等。在设计过程中,应充分考虑模块的可重用性和可维护性。

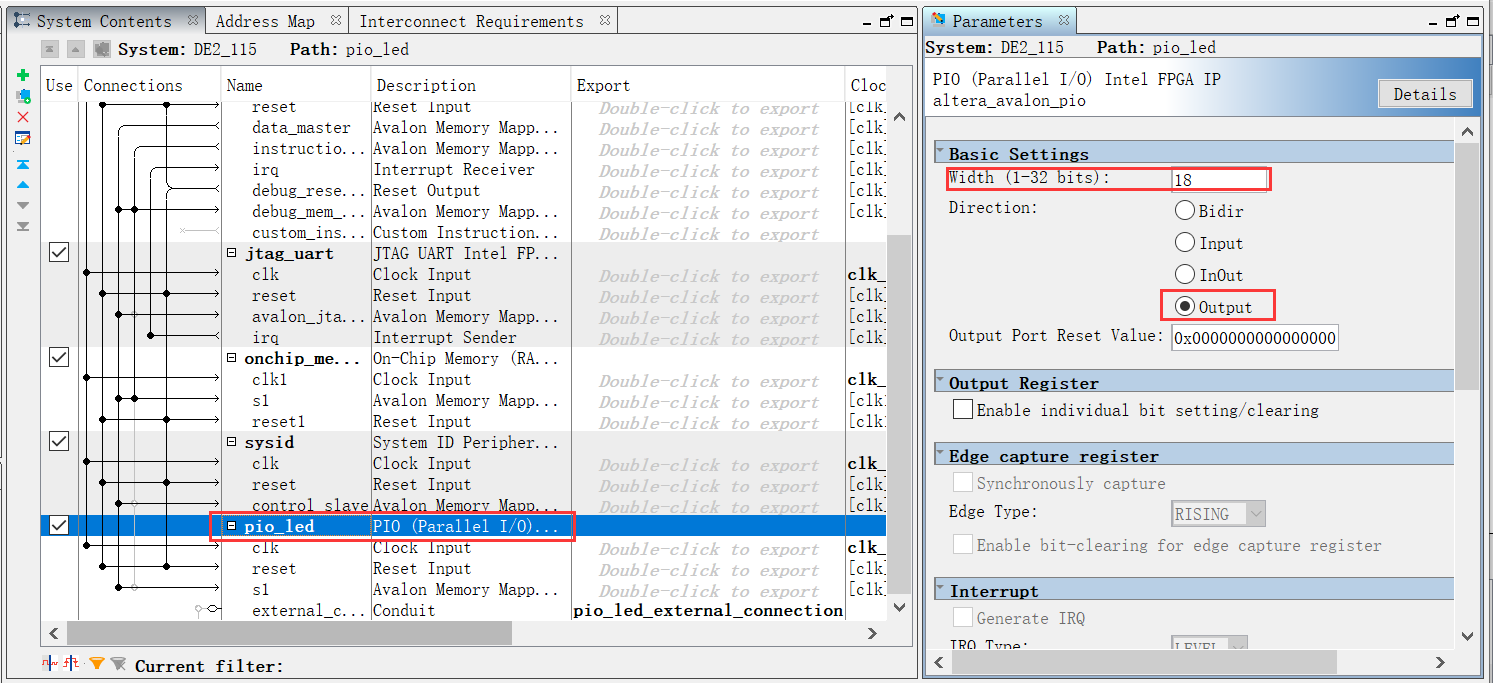

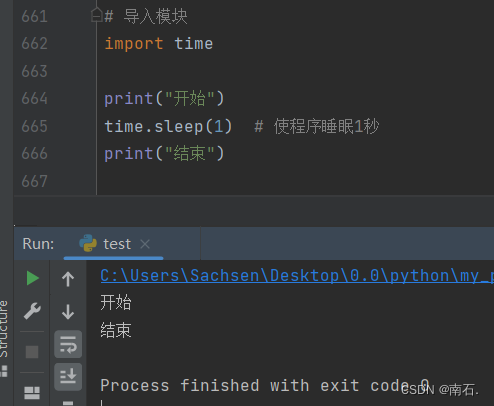

模块实现:使用硬件描述语言(如VHDL或Verilog)编写模块的源代码,并进行仿真验证。

四、案例解析

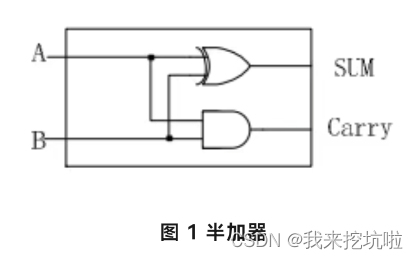

(1)半加器

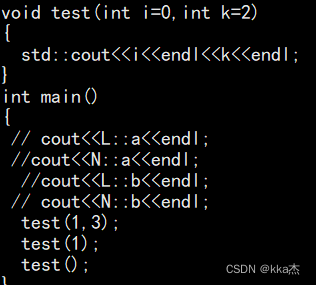

代码

module HalfAdder(A,B,Sum,Carry) ;input A,B;output Sum, Carry;assign #2 Sum = A ^ B;assign #5 Carry = A & B;endmodule

模块的名字是 HalfAdder。模块有 4 个端口:两个输入端口 A 和 B,两个输出端口 Sum 和Carry。由于没有定义端口的位数,所有端口大小都为 1 位;同时由于没有各端口的数据类型说明,这 4 个端口都是线网数据类型。模块包含两条描述半加器数据流行为的连续赋值语句。从这种意义上讲,这些语句在模块中出现的顺序无关紧要,因为这些语句是并发的。每条语句的执行顺序依赖于发生在变量 A 和 B 上的事件。

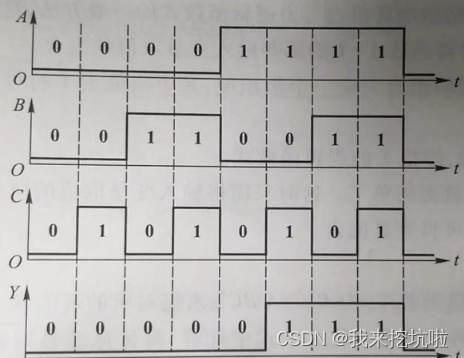

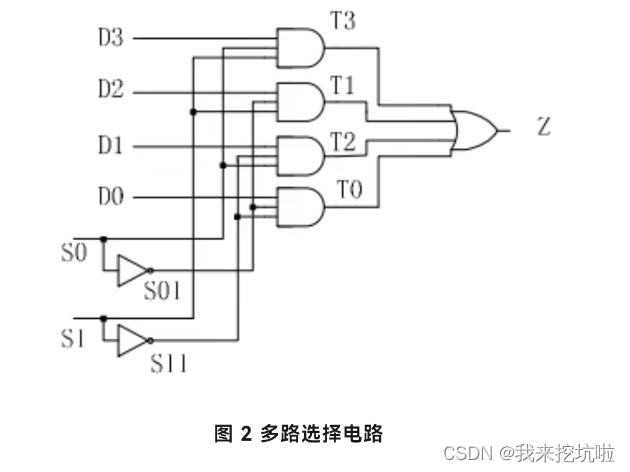

(2)多路选择电路

代码

module MUX4x1 (Z , D0 , D1 , D2 , D3 , S0 , S1) ;input D0 , D1 , D2 , D3 , S0 , S1;output Z;and (T0 , D0 , S01 , S11) ,(T1 , D1 , S01, S1) ,(T2 , D2 , S0 , S11) ,(T3 , D3 , S0 , S1) ,not (S01, S0) ,(S11 , S1) ;or (Z , T0 , T1 , T2 , T3) ;endmodule

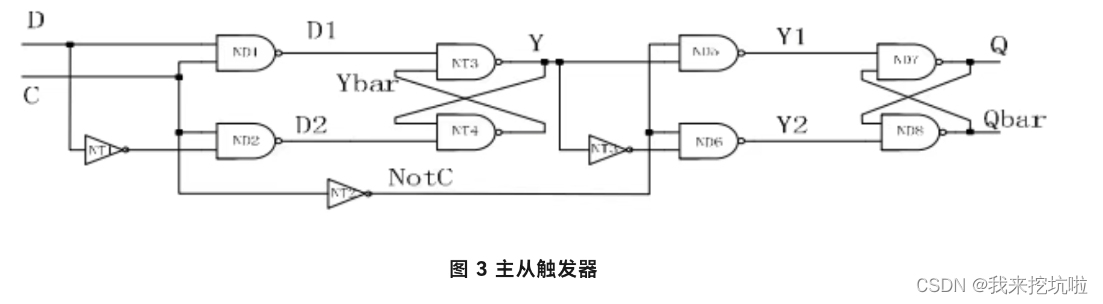

(3)主从触发器

代码

module MSDFF_DF (D, C, Q, Qbar) ;input D, C;output Q, Qbar;wire NotC, NotD, NotY, Y, D1, D2, Ybar, Y1, Y2 ;assign NotD = ~ D;assign NotC = ~ C;assign NotY = ~ Y;assign D1 = ~ (D & C) ;assign D2 = ~ (C & NotD) ;assign Y = ~ (D1 & Ybar ) ;assign Ybar = ~ (Y & D2) ;assign Y1 = ~ (Y & NotC ) ;assign Y2 = ~ (NotY & NotC) ;assign Q = ~ (Qbar & Y1) ;assign Qbar = ~ (Y2 & Q) ;endmodule

五、总结

FPGA模块化设计是一种重要的设计策略,能够显著提高FPGA设计的可重用性和灵活性。通过合理的模块划分、设计、实现和测试验证等步骤,可以构建出稳定可靠、易于维护和扩展的FPGA系统。在实施FPGA模块化设计时,应注意接口标准化、模块化程度、模块化测试和文档管理等关键问题。