1.时序参数

AN65974文档中明确了操作GPIF II接口时的时序参数,上一篇文章中给出了读写时序图,本篇第二节给出ZLP写周期时序,这里说明相关的时序参数。应该注意,这是Cyusb3014芯片的时序要求,与外部控制器是什么无关。另外要注意,PCLK信号是由外部控制器传递给Cyusb3014的时钟,而不是它自身的。

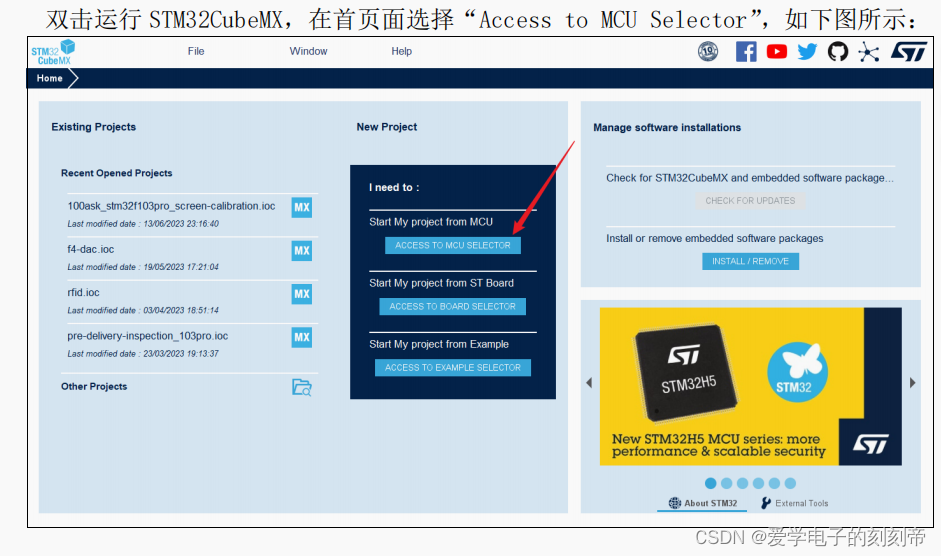

2.FX3_PCLK

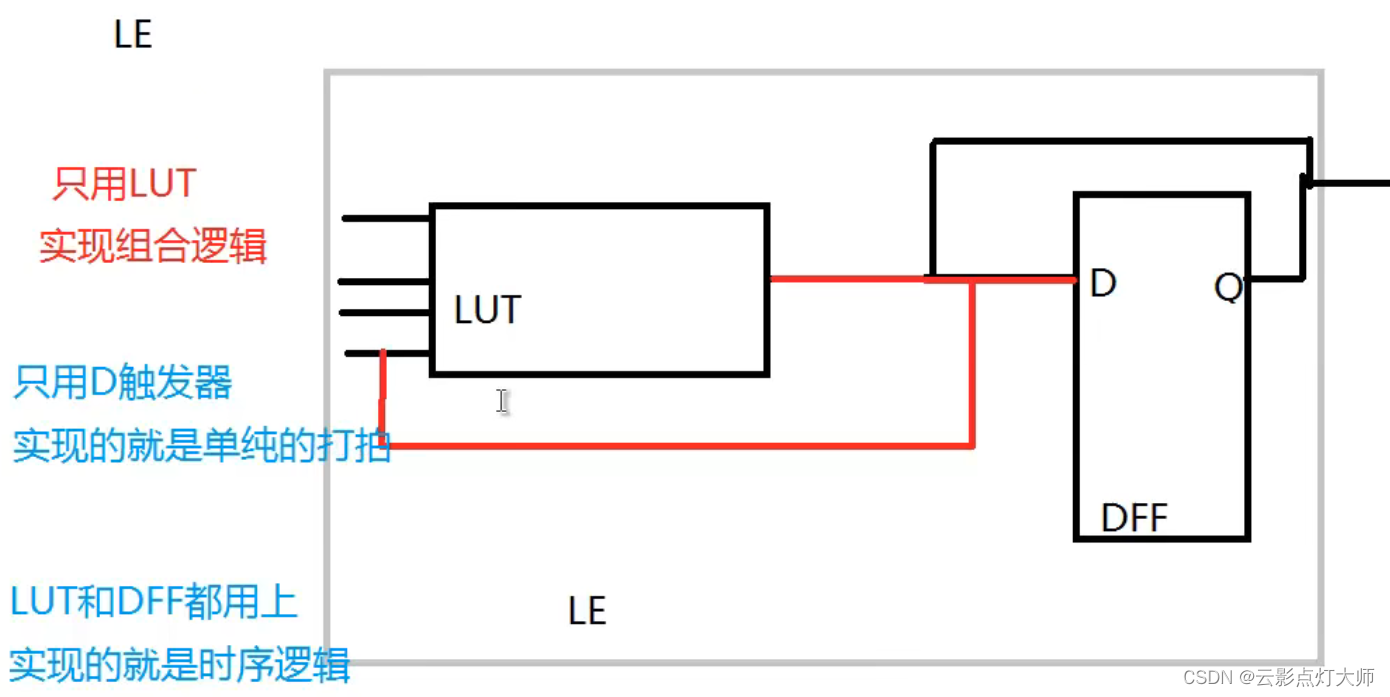

FX3_PCLK是由外部控制器产生的时钟,因此FPGA开发过程中有两个时钟信号和Cyusb3014相关,一个是驱动时钟,即连接到FX3_PCLK的时钟信号;还有一个是用户时钟,即FPGA工程里USB驱动模块的时钟。驱动时钟和用户时钟都应该是100MHz,但需要有180°的相位差。可以使用PLL锁相环生成,在锁相环管脚不够用的情况下也可以使用ODDR原语生成驱动时钟。这样做的目的就是为了满足cyusb3014对于时序参数的要求,既有充足的保持时间和建立时间,下图以slwr信号为例进行说明。

图中tap(0-1) 代表PCB走线延时,对于FX3_PCLK和SLWR几乎一样(信号等长设计)。Tap(1-2) 代表SLWR相对PCLK的延时(FPGA内部走线也需要时间,长短不同会造成到达IO的时间不一致s)。当tap(1-2)很小的时候,通向的FX3_PCLK可能无法满足Cyusb3014对于SLWR信号保持时间要求,而反相的FX3_PCLK,对保持时间和建立时间都有足够大的裕量,满足时序要求

3.短包和零包

前面已经详细的叙述了读与写的操作时序,但是仅有这些描述还不足以正确完成数据传输。考虑一个问题。AN65974中提到“标志与特定线程或当前寻址的线程相关联,用于表示映射到该线程的套接字状态”。以下行数据通道为例,当PIB还未通过自动DMA接收到数据的时候FLAGC为0。初始状态下,FLAGC为0,当上位机启动数据传输时,数据经过端点,UIB套接字到达缓冲区,只有数据从缓冲区达到PIB套接字,FLAGC才由0变成1标识缓冲区未空。而数据何时缓冲区到达PIB套接字是有条件的,即数据量刚好为一个缓冲区的大小,或,小于一个缓冲区但要执行执行一次COMMIT操作。『USB3.0Cypress』Cyusb3014开发(5)GPIF II接口中介绍了COMMIT的作用是缓冲区将被传输到管道的另一端。通常通过该操作,可强制缓冲区/数据包结束。当上位机发送的数据等于16KB时,正常发送数据即可到达PIB套接字,当数据小于16KB时应通过“短包或者零包的方式”发送,这种操作在介绍上位机的时候会讲(其实是通过特定的方式发送,只要能让小于缓冲区大小的数据到达PIB即可,这里把这种方式称作短包/零包)。那么也只有数据到达PIB,相应的FLAG信号才会变化,才能确保FPGA能够正确的读取数据。

本节讲的是上行数据通道,也就是对于FPGA来说,如何让小于缓冲区大小的数据从PIB到达缓冲区并到达UIB,这样做是为了上位机能够正确的读取数据。下图展示了AN65974的GPIF里面的状态机,可以清晰的看到只有在ZLP和SHORT_PKT中执行了COMMIT操作。因此这里说的零包和短包本质上是用不同组合的控制信号进入ZLP或SHORT_PKT状态执行COMMIT操作,那么短包和零包的应用场景便是完成小于缓冲区大小的数据的发送。依照现有结论向GPIF中写1024B数据,使用零包或者短包上位机都可以正确接收数据。3.1节和3.2节将分别测试,结果如何?拭目以待。

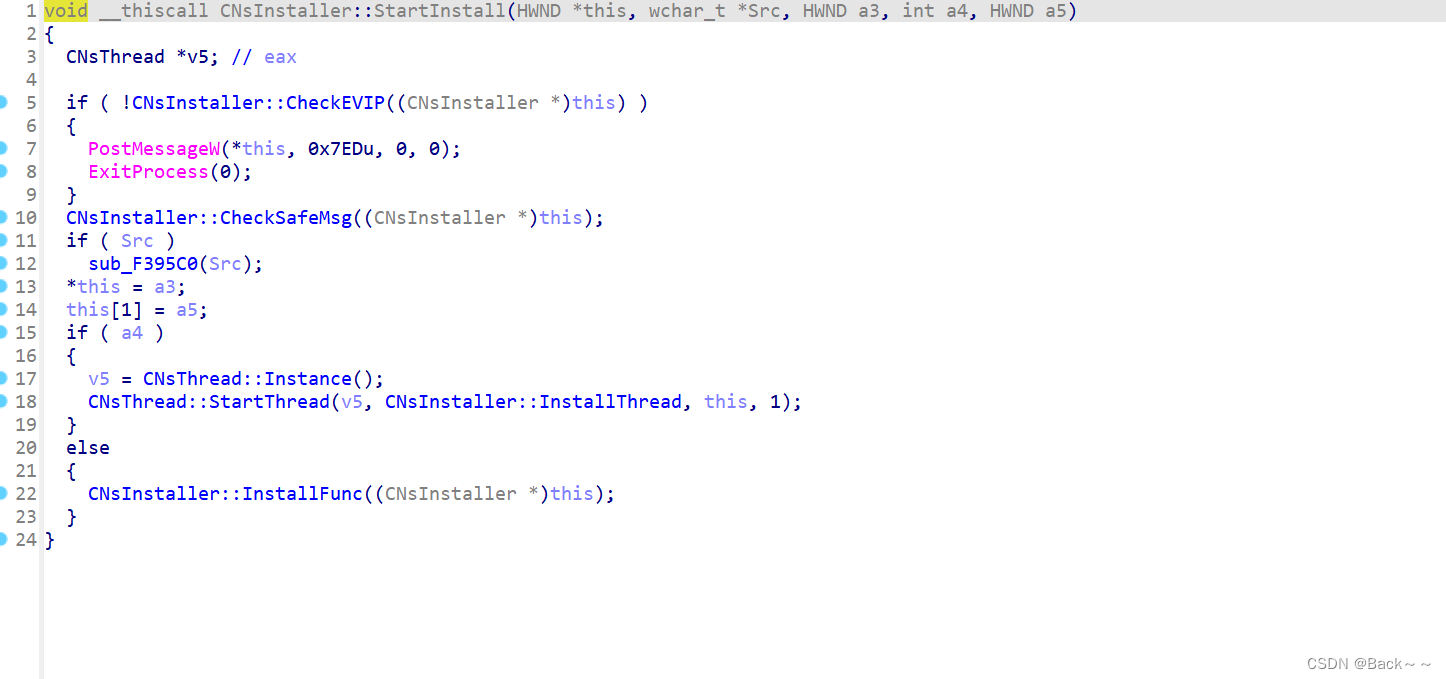

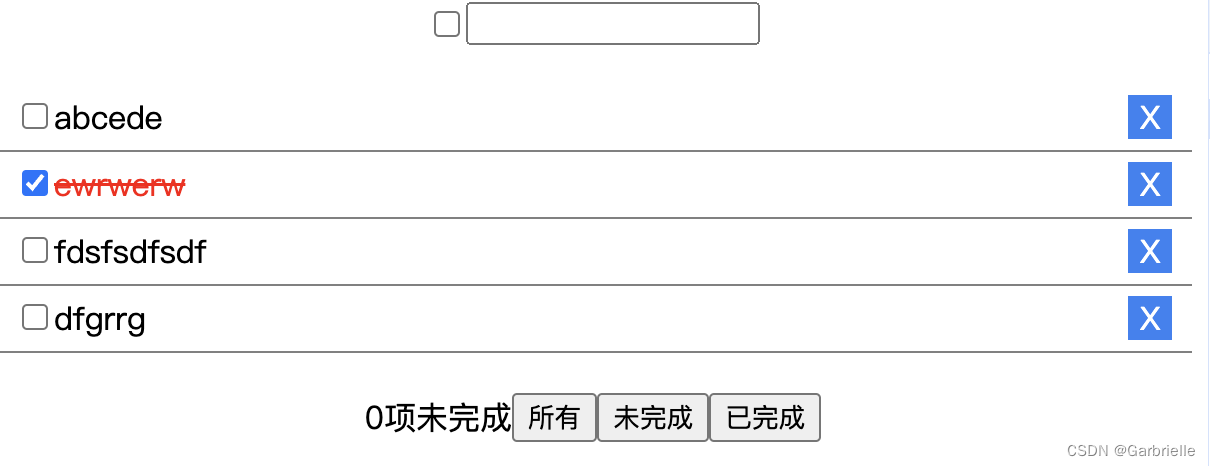

3.1短包时序

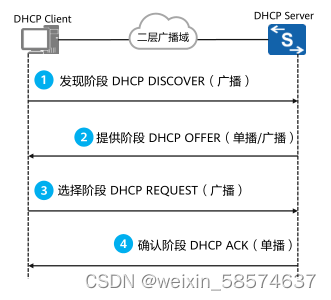

FPGA可控制仅通过激活PKTEND#,并且激活 SLWR#来传输一个短包(short package)。当然在此之前应该FIFO地址稳定且SLCS#激活。向GPIF II中写1024B数据,如图所示,在slwr拉高前的最后一个周期,将pktend信号拉低一个周期,便是以短数据包的形式写入数据,可以在control center中看到正确的数据。观察到在pktend信号置位三个周期后flaga信号会拉低一段时间,注意此时只向16KB的缓冲区写了1KB数据,按常规理解此时flaga不会为低电平,咨询赛普拉斯官方工程师,说是正常现象,可能是切换缓冲区了。

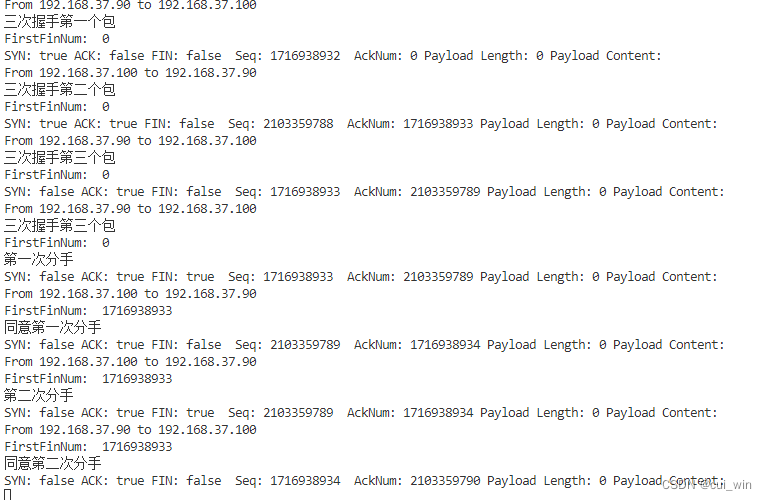

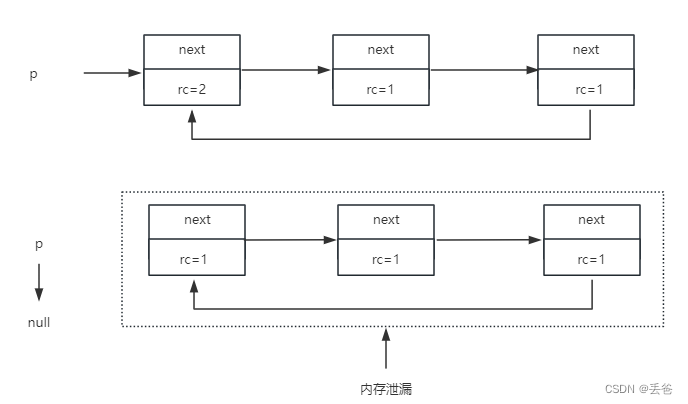

3.2零包ZLP时序

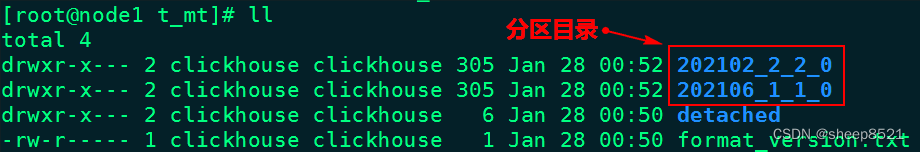

FPGA可控制仅通过激活PKTEND#,而没有激活 SLWR#来传输一个零长度数据包(ZLP)。但必须驱动 SLCS#和地址。向GPIF II中写1024B数据,在slwr拉高以后,再将pktend信号拉低一个周期,按照对AN65974的理解,这里应该为发送1024B之后再发送一个零数据包(ZLP)来使缓冲区commit,但按照如下图所示在写完1024B数据之后紧接着发送一个零包,使用control center接收数据,会出现997的错误。

对于此问题通过向官方社区询问已经得到解答,我们使用的是sync slave fifo这个状态机,在从WRITE到ZLP时需要经过IDLE状态,因此如果写结束后没有延迟直接拉低pktend信号不满足(PKEND&SLWR)|SLCS,状态机跳回到IDLE的条件因此会出现错误,所以这时需要创造使状态机跳回到IDLE的条件才能发送零长度数据包。这里采用将pktend延迟一个clk再拉低,状态机即可进入IDLE状态,从而后续再进入ZLP状态发送零长度数据包。正确的处理如下图所示。

4.传送门

| END |

🔈文章原创,首发于CSDN论坛。

🔈欢迎点赞❤❤收藏⭐⭐打赏💴💴!

🔈欢迎评论区或私信指出错误❌,提出宝贵意见或疑问❓。