FPGA时序分析与约束

时序分析:通过分析FPGA内部各个存储器之间的数据和时钟传输路径,来分析数据延迟和时钟延迟的关系,保证所有寄存器都可以正确寄存数据。

数据和时钟传输路径是:由EDA软件,通过针对特定器件布局布线得到的。

时序约束:告知EDA软件,尽力达到约束指标。

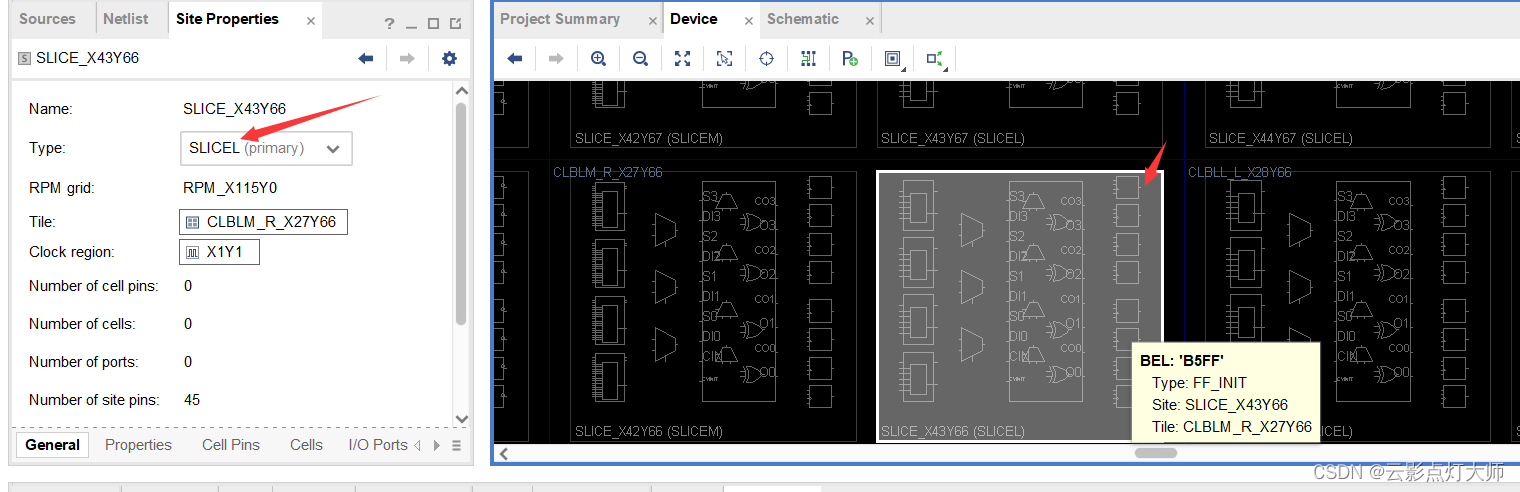

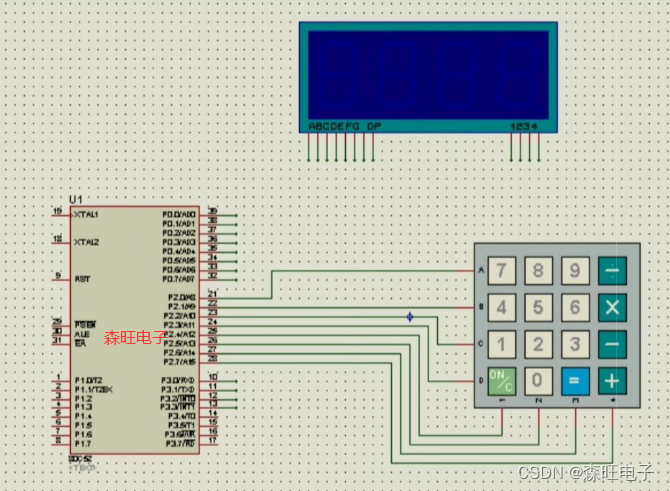

FPGA结构基础

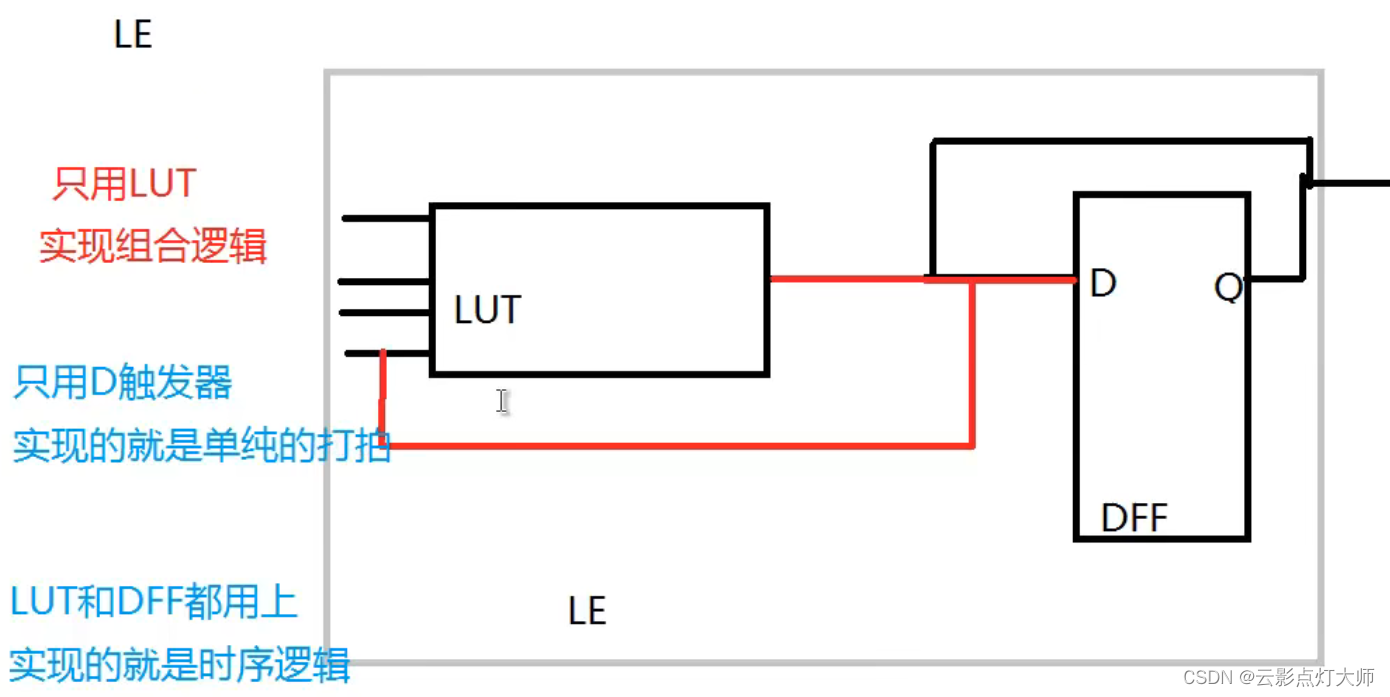

可编程逻辑功能结构

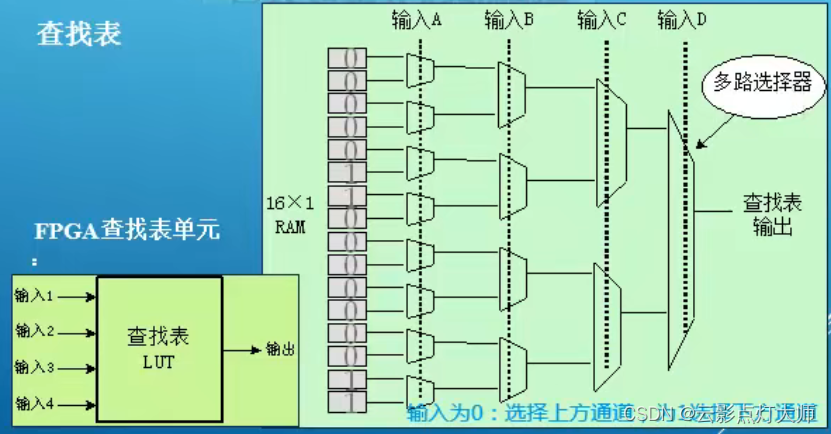

LUT 查找表的实现

fpga结构

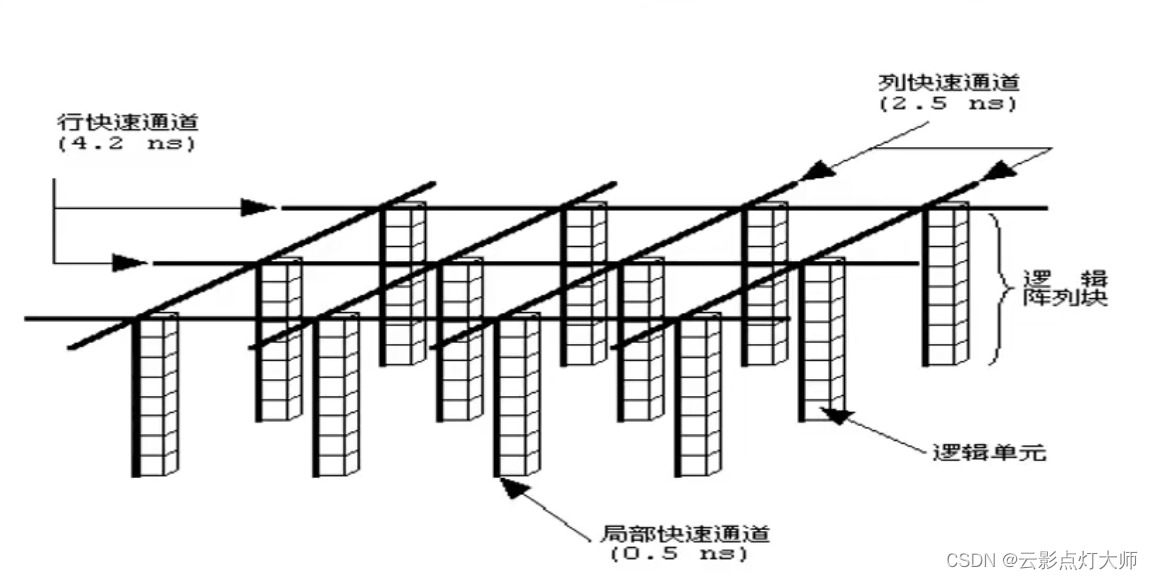

内部连线:

采用行,列,局部的快速通道

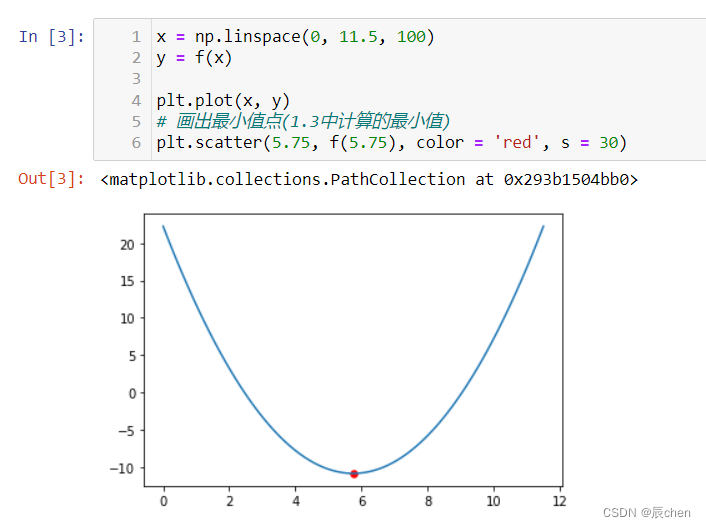

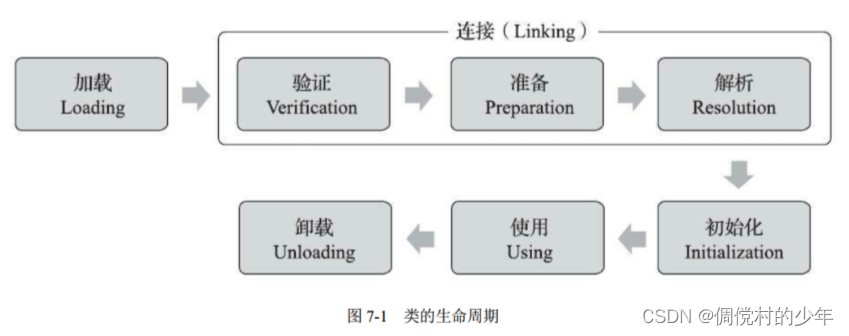

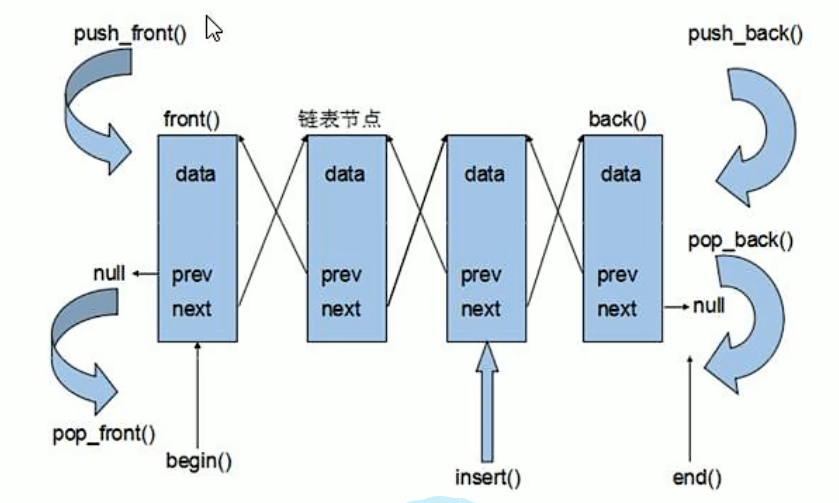

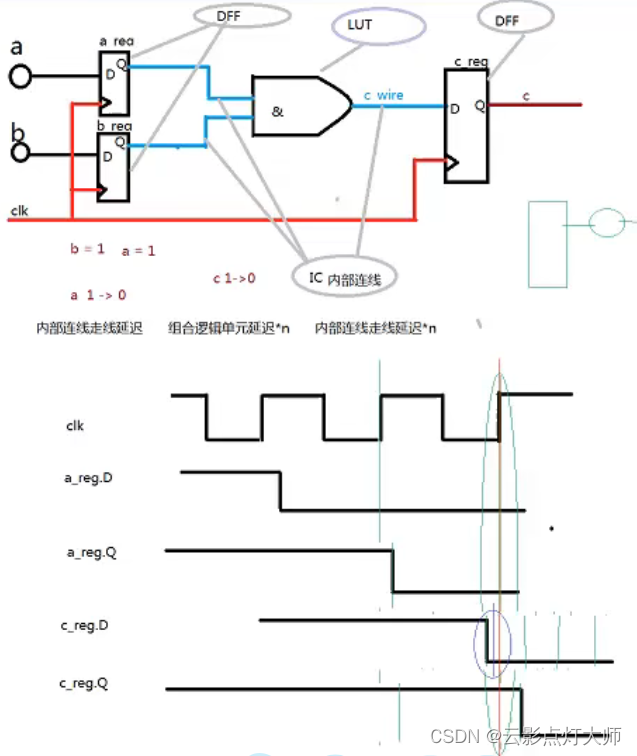

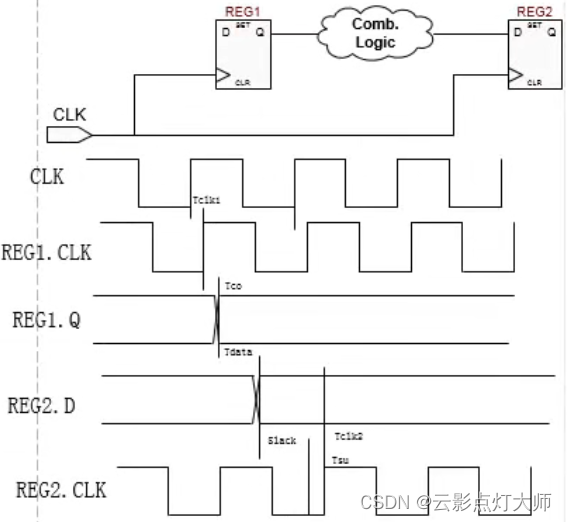

数据传输模型

Tco :时钟上升沿到达D触发器 到 数据输出到Q端的延迟 。

Tsu: 建立时间,数据输入端D的数据必须提前 N ns 稳定下来,否则就没办法保存下来数据。

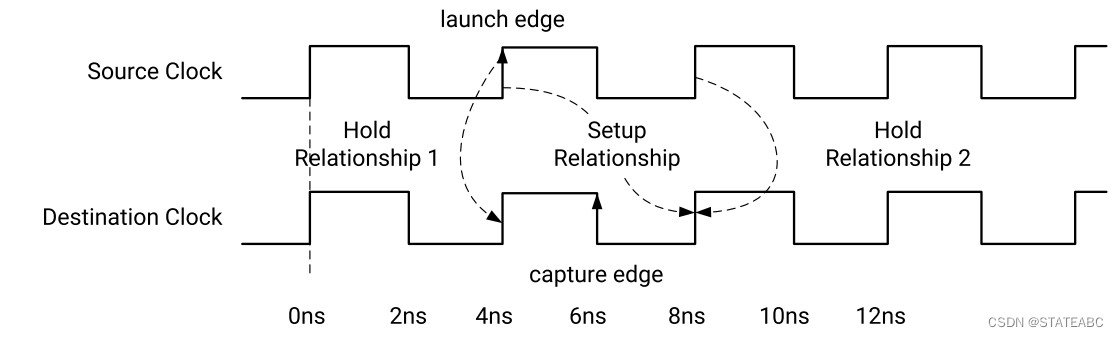

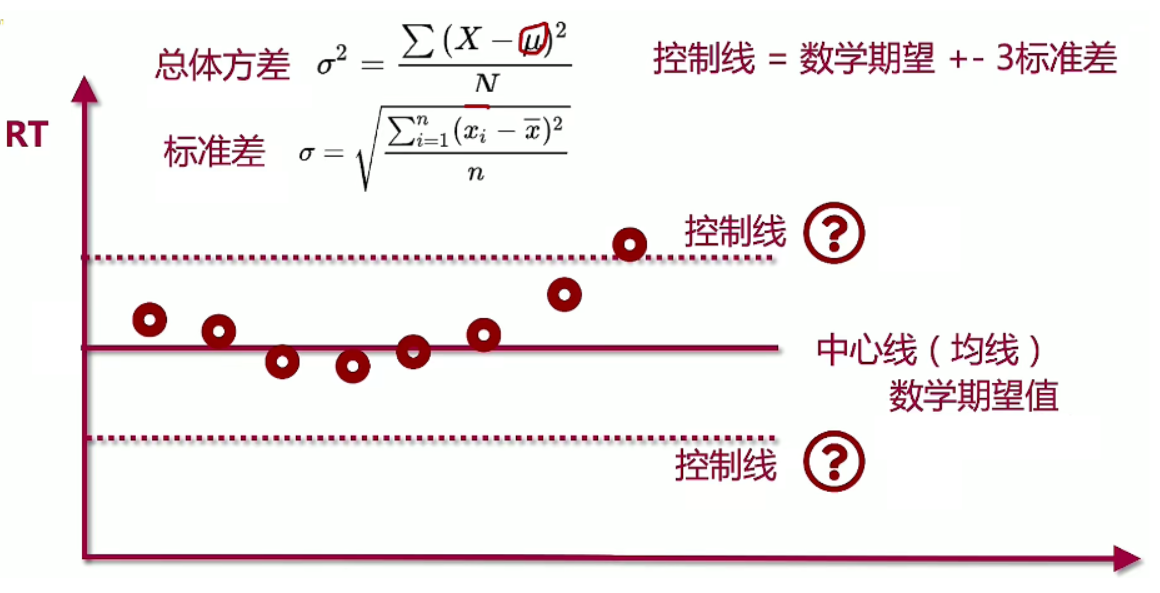

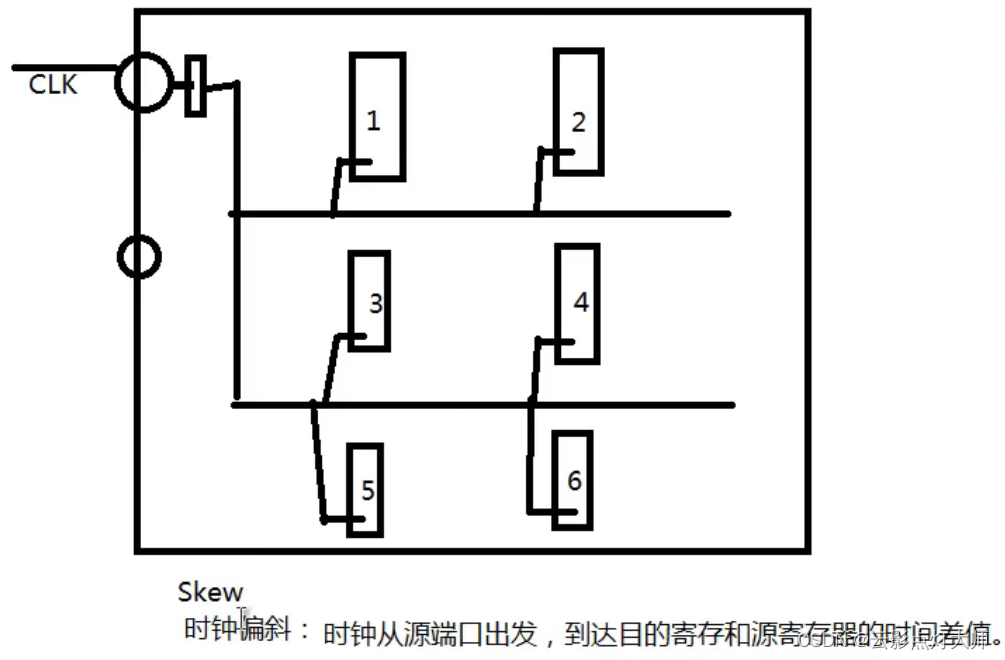

时钟偏斜原理:

在这个模型下:

Tclk1:时钟传到REG1有个延迟。

Tclk2:时钟传到REG2有个延迟。

Tco:触发器D 到Q输出的时间 。

Tdata:REG1的Q 传输到 REG2的D 的时间。

Tsu:建立时间。

Slack:余量时间。(下图是正的,说明可以正确读取到数据)

可以推导出公式,可以正确接收数据:

Tclk1+Tco+Tdata <= Tclk(时钟周期) + Tclk2 - Tsu

化简得: Tclk +(Tclk2 - Tclk1 )- Tco - Tdata - Tsu >= 0

再得:Slack = Tclk + Tsnew - Tco - Tdata - Tsu >= 0

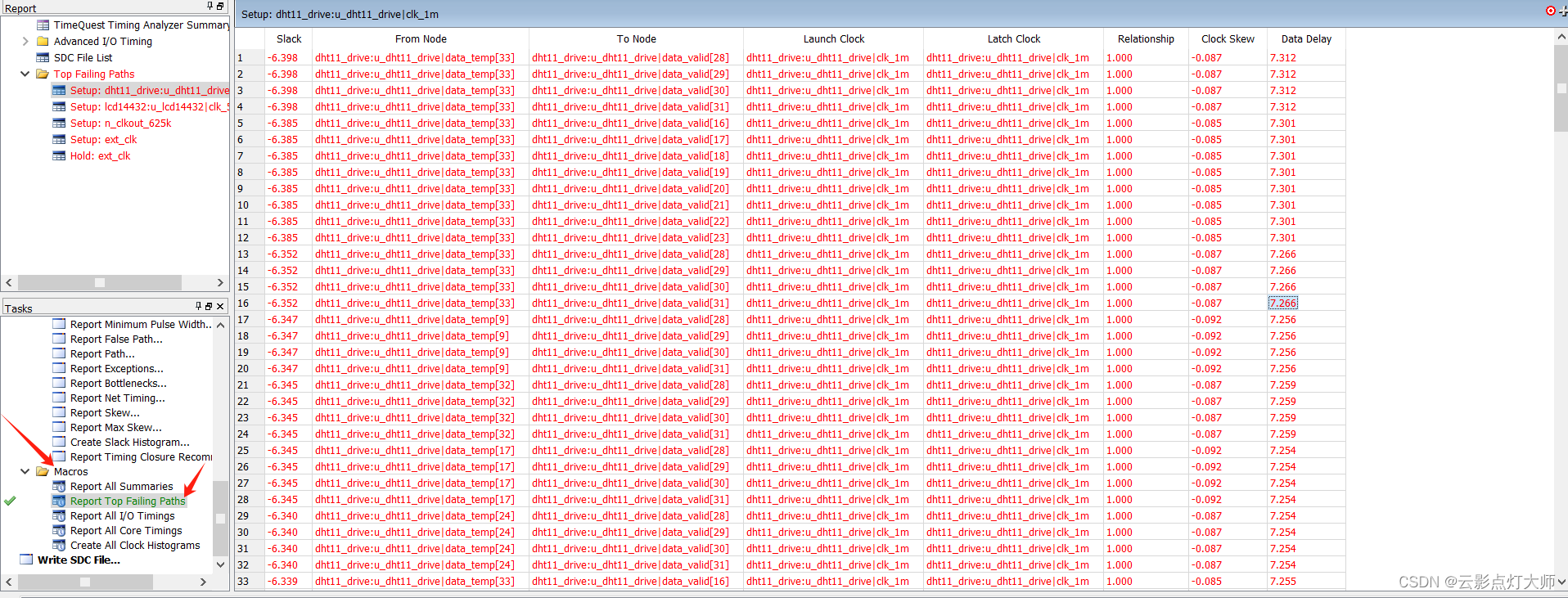

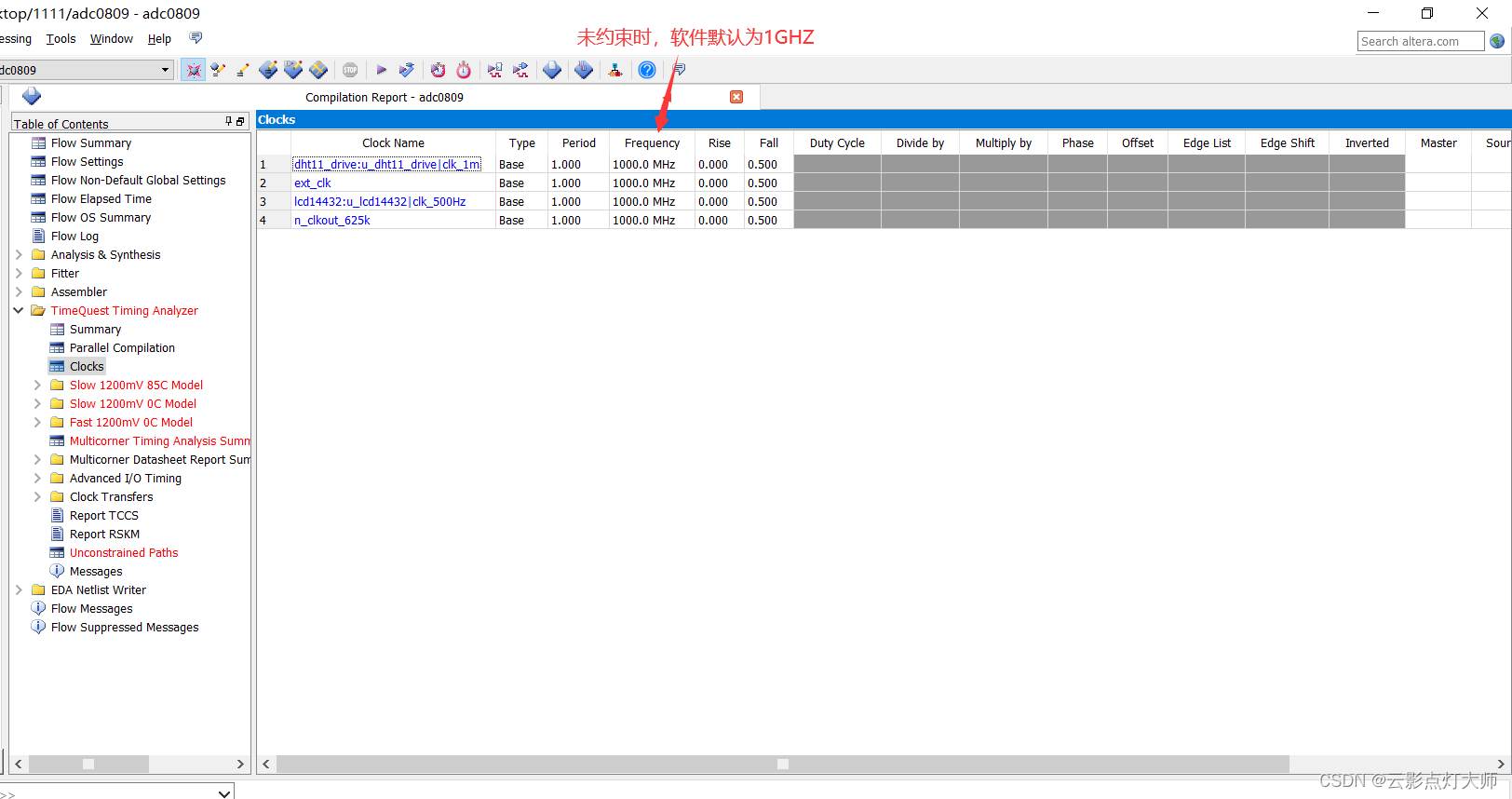

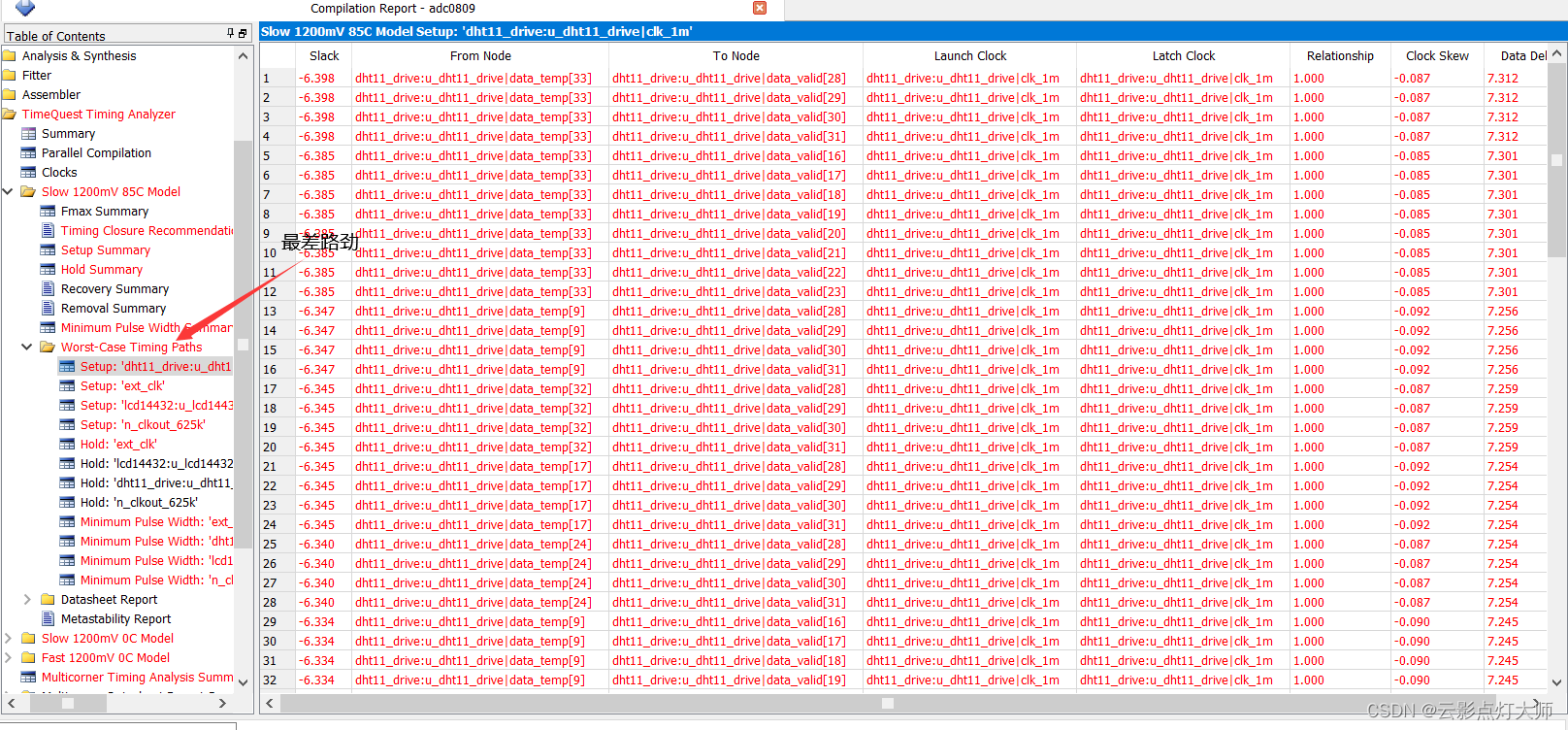

Quartus II 时序报告

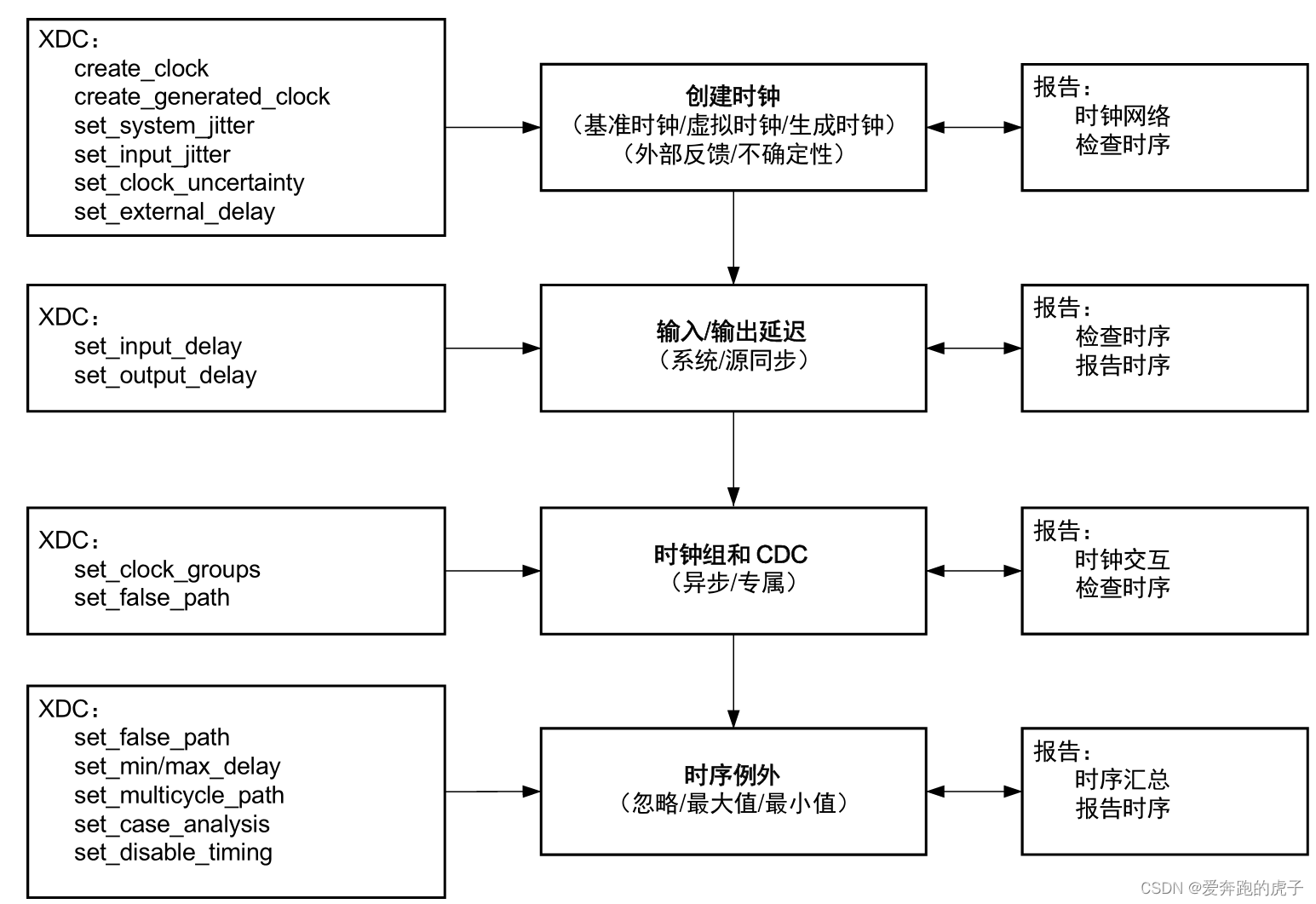

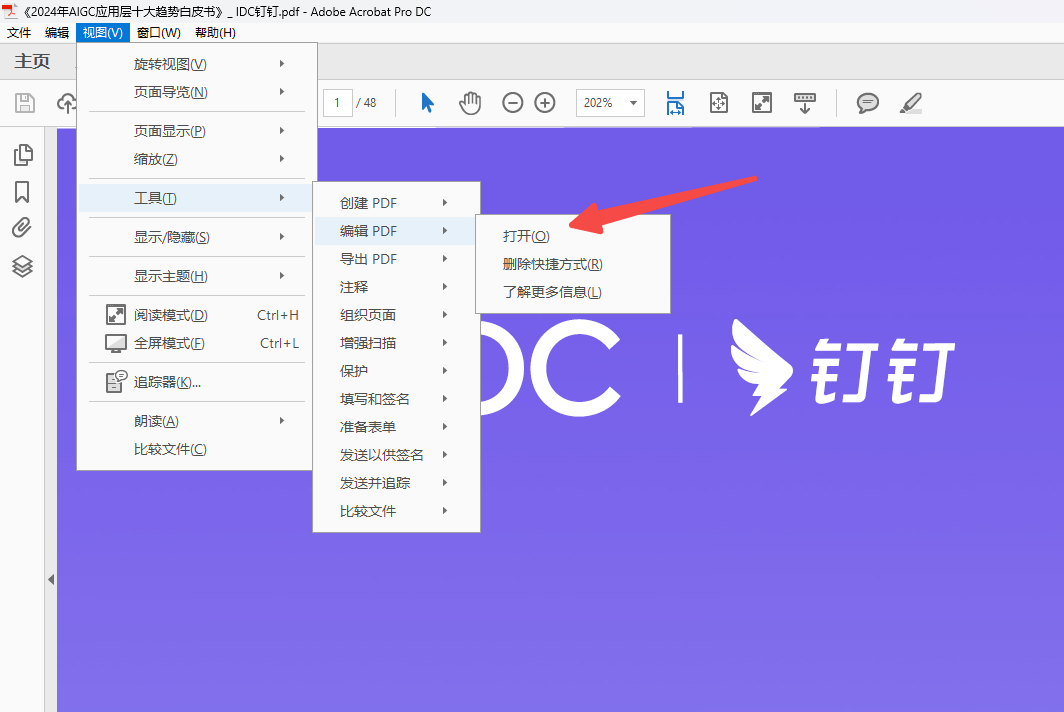

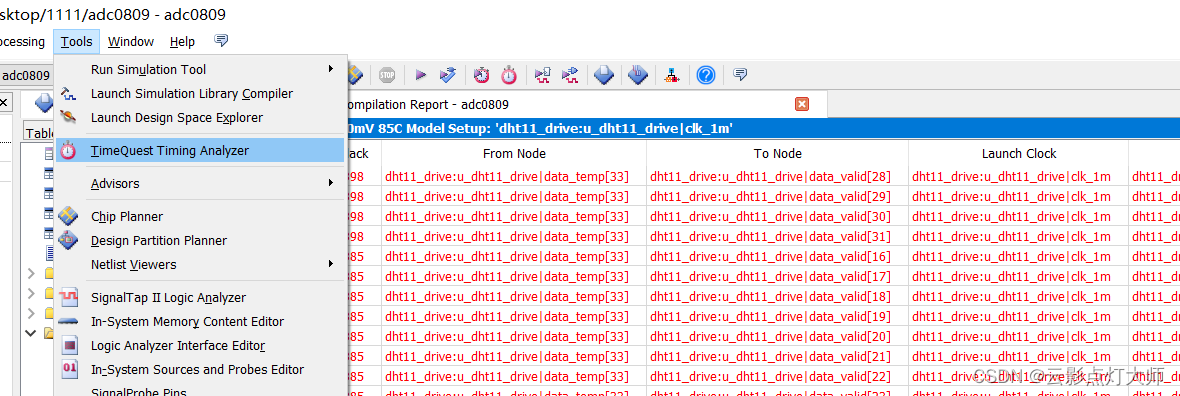

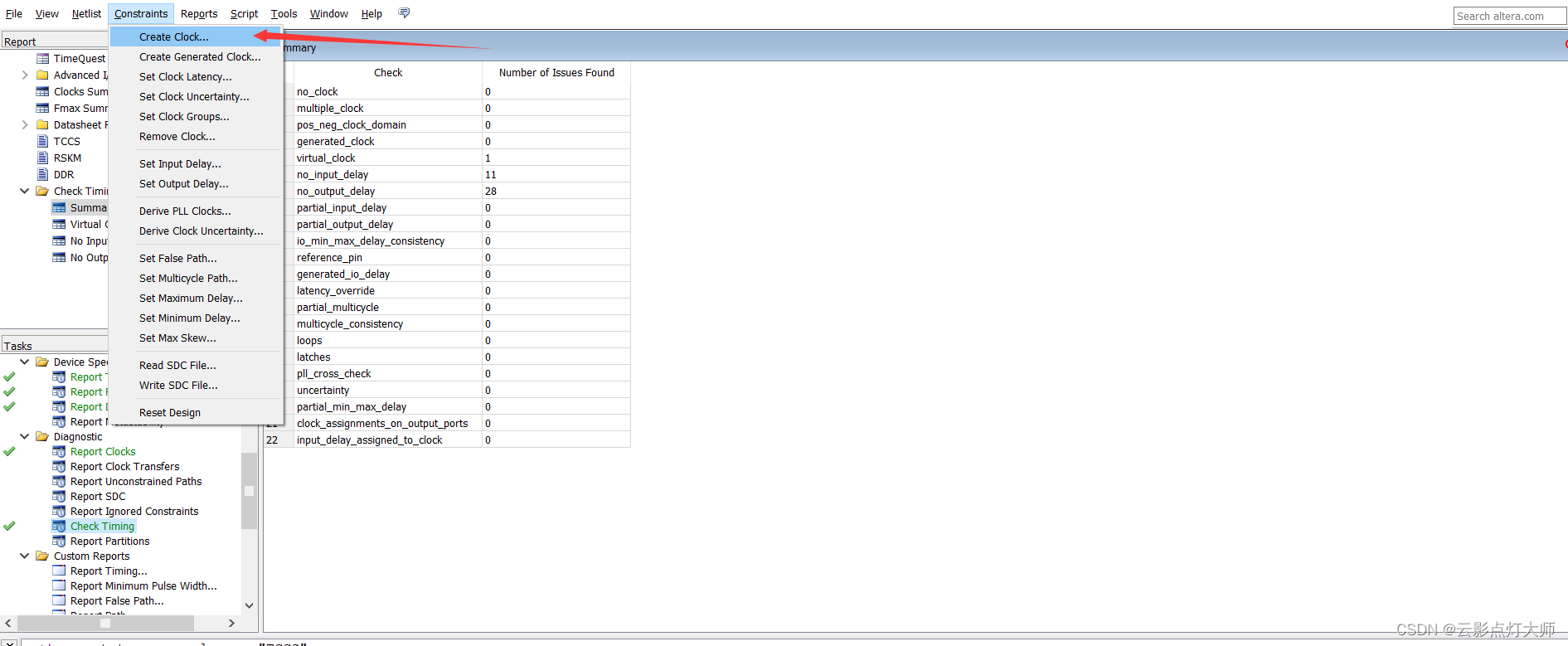

Quartus II 中TimeQuest的操作

1.打开工具

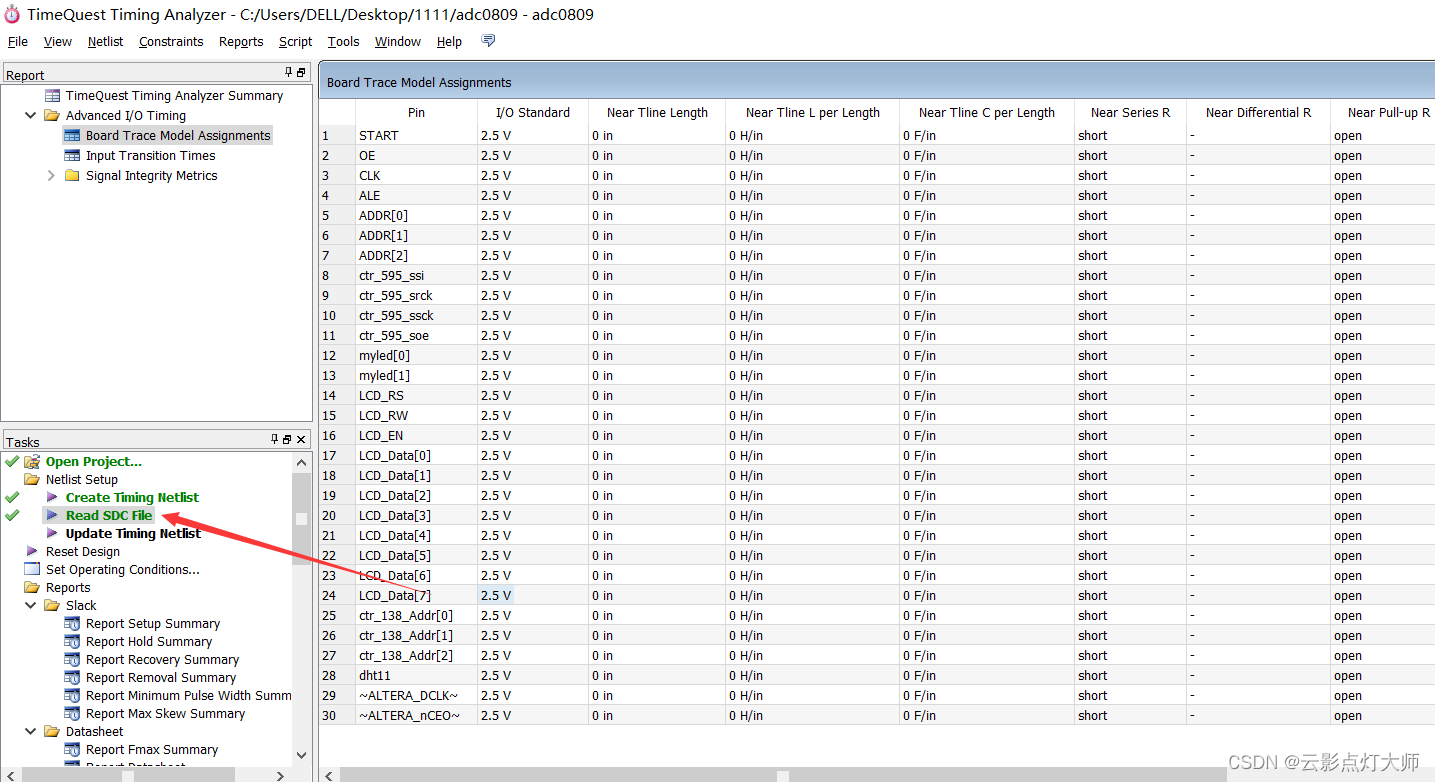

2.创建时序网表

包含:该器件具体位置,什么资源上实现,每个节点到下个节点的延迟时间

3.读取SDC文件

4.看报告和加入约束

看报告

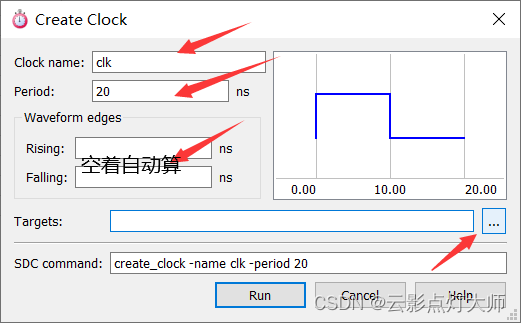

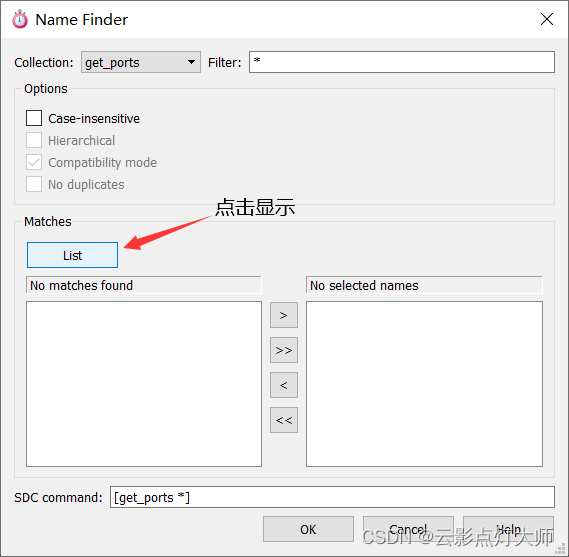

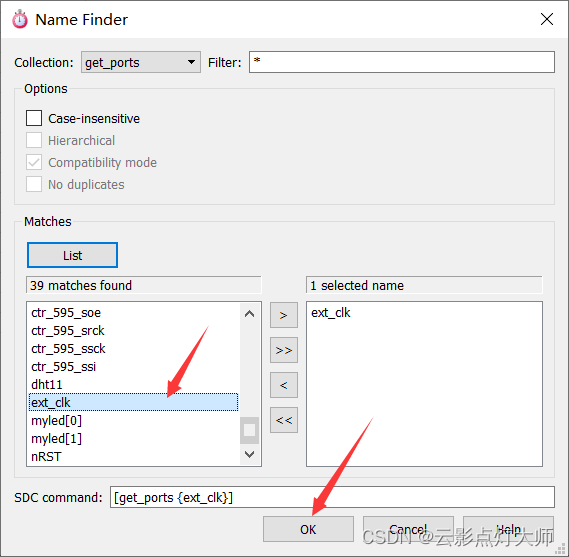

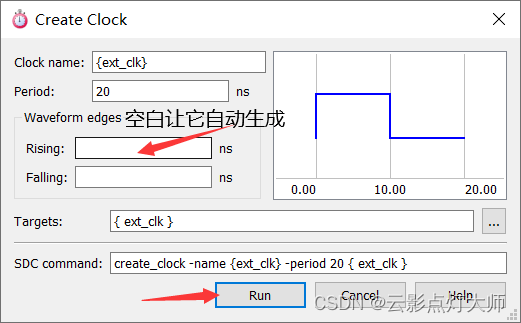

(1)加入约束,告诉软件外部时钟输入

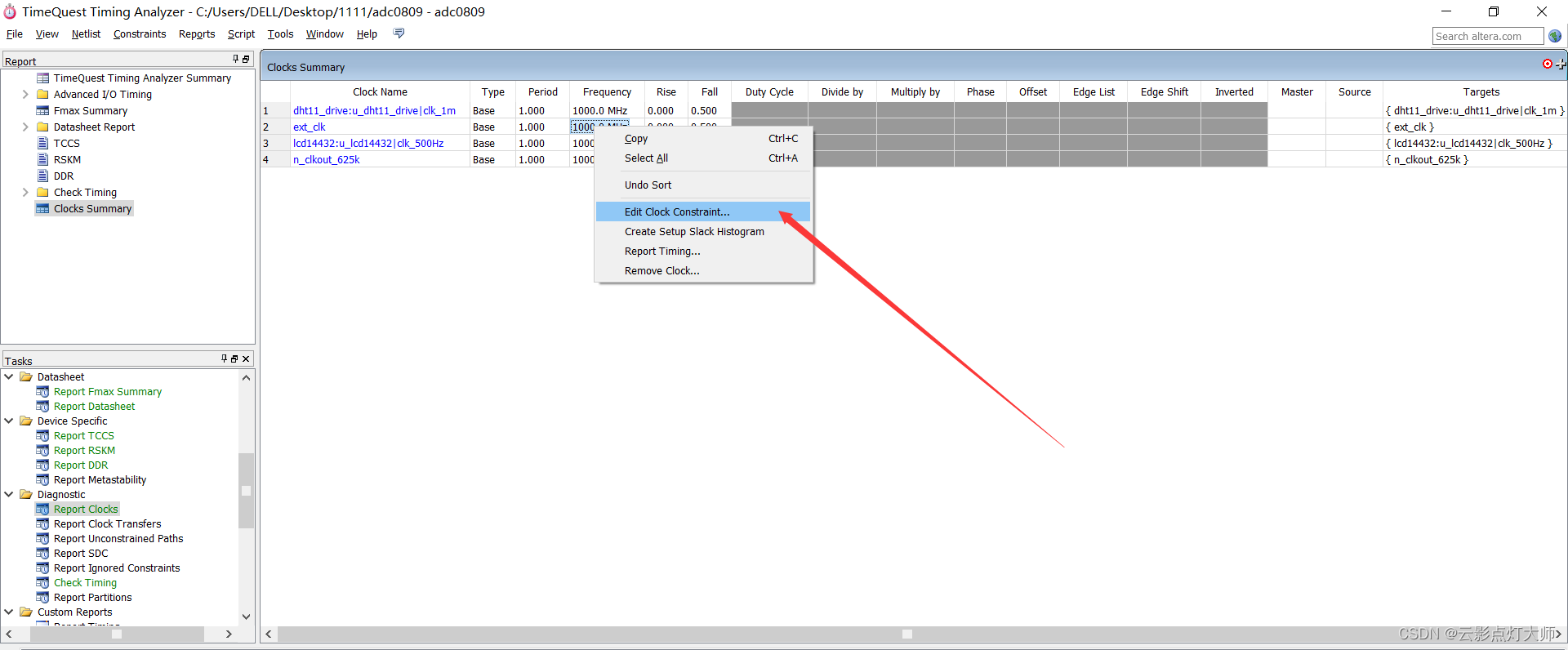

(2)编辑现有的约束

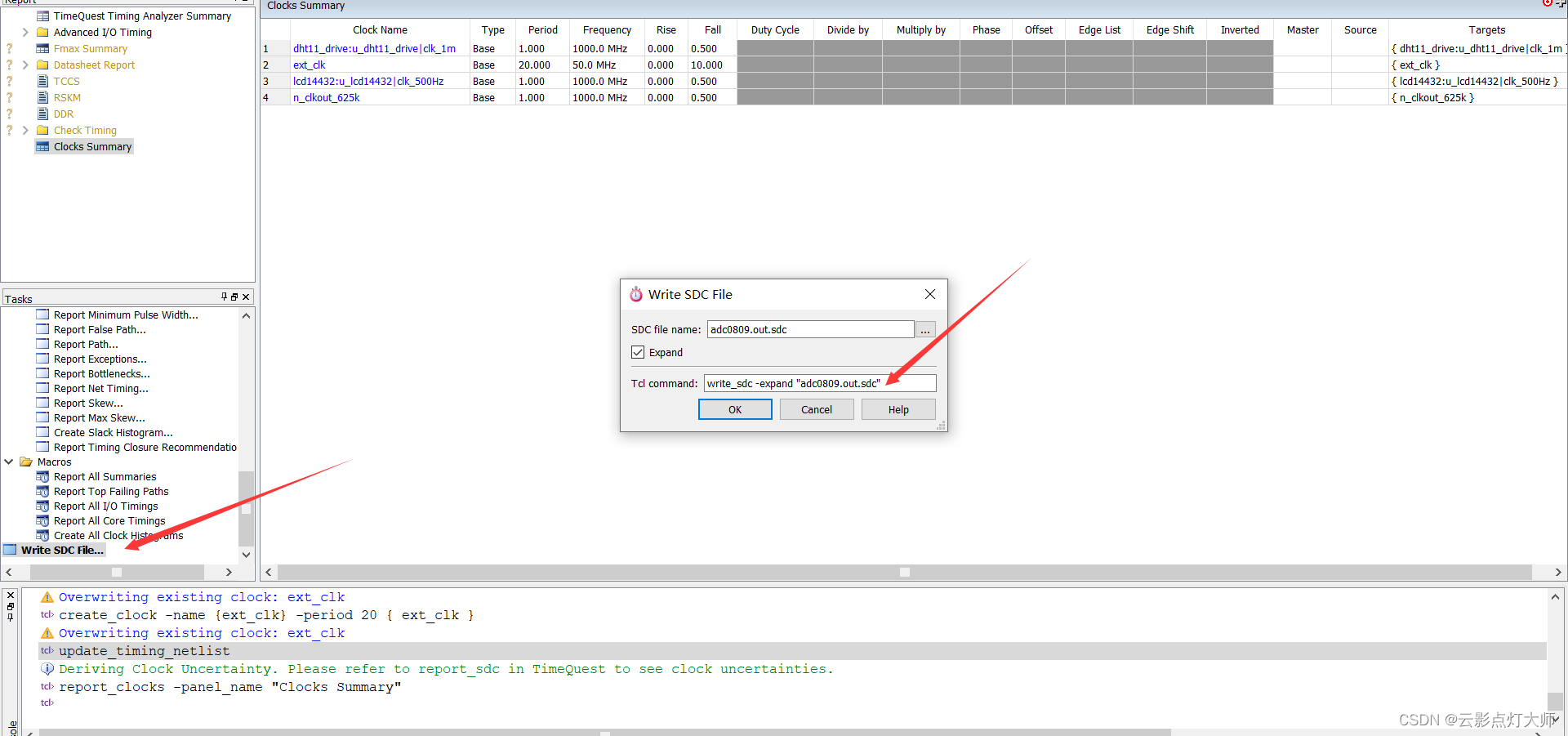

5.生成SDC文件

实操

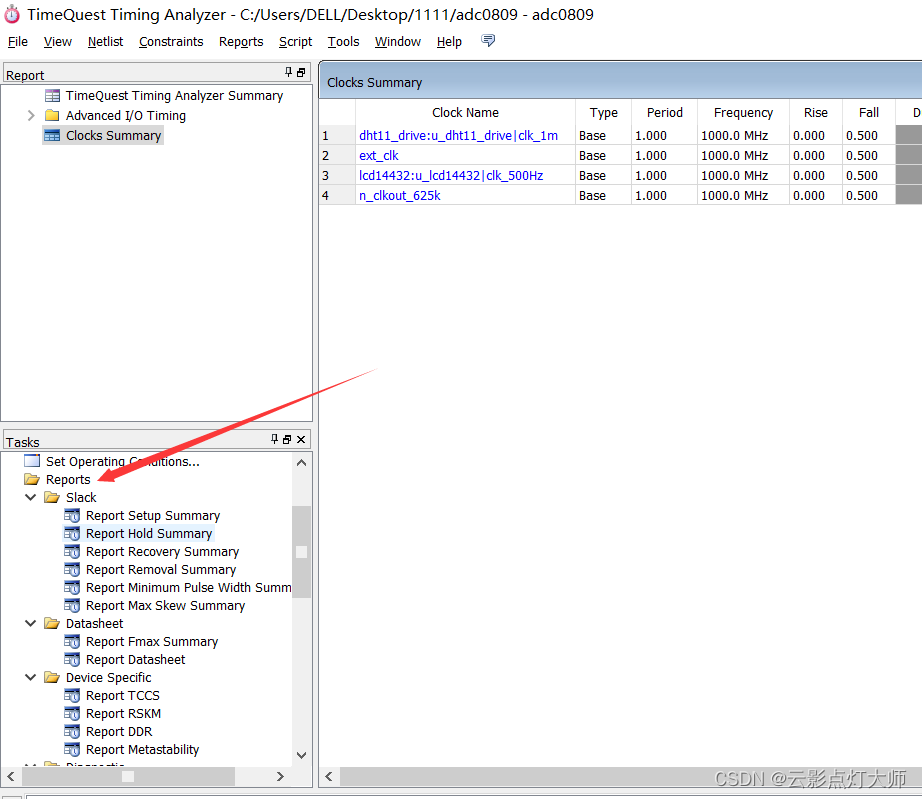

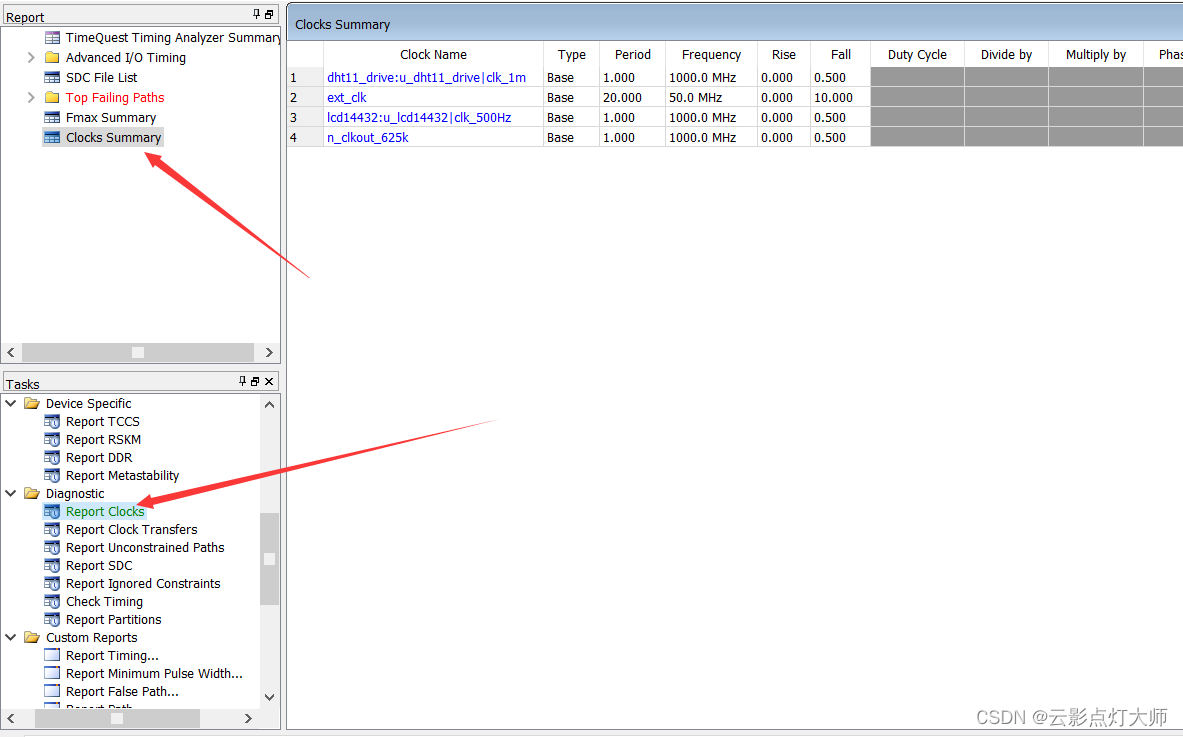

查看时钟

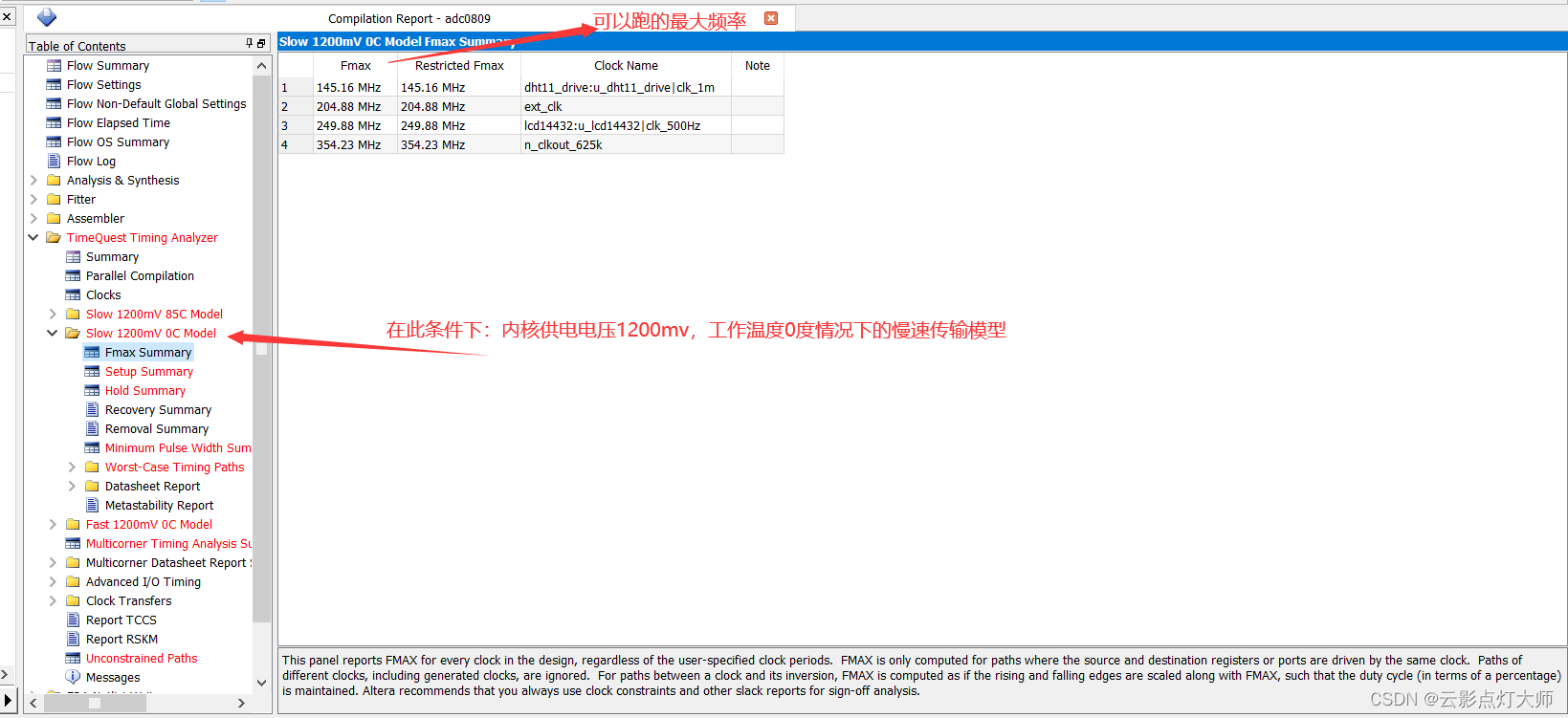

查看最坏路径的余量