3.1 存储器概述

3.1.1 存储器分类

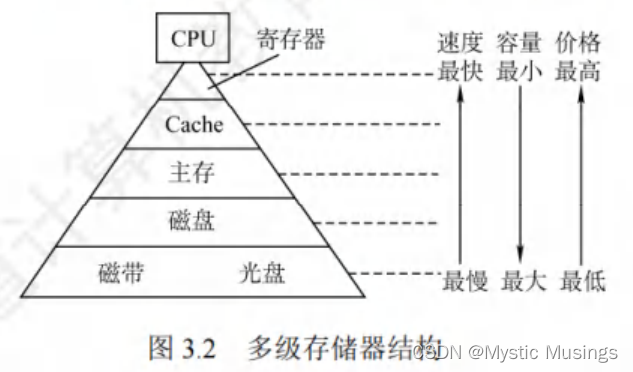

- 1.按照层次

- 可以直接被CPU读写:

- 1.主存: 【存放运行期间所需程序或数据】

特点:容量较小,存取速度快,价格较高

芯片组成:DRAM和ROM - 2.高速缓冲存储器: 【解决CPU与主存速度差距大】

特点:速度快,容量低,价格高

芯片组成:SRAM

- 1.主存: 【存放运行期间所需程序或数据】

- 不能直接被CPU读写:

- 3.辅助存储器:【存放暂时用不到的数据】

特点:容量大,速度慢,成本低。

芯片组成: ROM

- 3.辅助存储器:【存放暂时用不到的数据】

- 可以直接被CPU读写:

- 2.按存储介质分类

- 磁表面存储器:磁盘,磁带

- 半导体存储器:

- MOS型存储器:用于DRAM

- 双极型存储器:用于SRAM

- 光存储器:光盘

- 3.按存取方式:

- 随机存储器(RAM):【任何存储单元都可以直接存取,断电易丢失】

- DRAM:用于主存,需要刷新

- SRAM:用于cache和快表,不需要刷新

- 只读存储器(ROM):【只能写入数据,不能修改数据,断电不会失去数据,可以随机存储】

- 串行访问存储器:【随机存储+顺序存储】

- 按内存访问存储器:【用于全相联存储器】

- 随机存储器(RAM):【任何存储单元都可以直接存取,断电易丢失】

- 4.按信息可保存性:

- 断电易失性存储器:RAM

- 断电不丢失存储器:ROM

- 破坏性读出储存器:DRAM

- 非破坏性读出存储器:SRAM,ROM,磁盘,光盘等

3.1.2 存储器的性能指标

- 存储容量=存储字长(MAR位数)*字长(MDR位数)

- 单位成本:单位价格=总成本/总容量

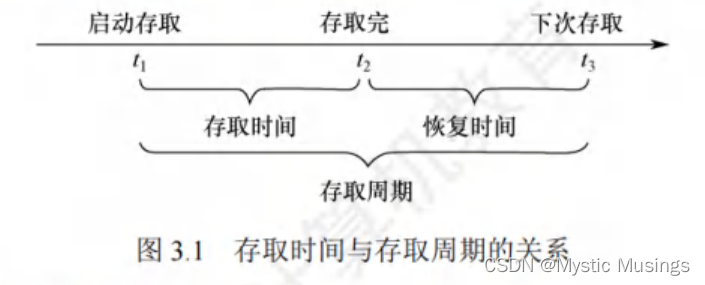

- 存储速度:速度传输率 = 数据宽度(存储字长)/存取周期

存取时间<存储周期

3.1.3 多级层次的存储系统

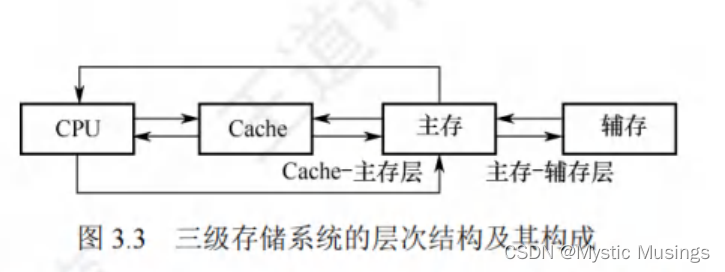

主存和cache交换数据由硬件自动完成,解决主存和CPU速度怕不匹配的问题。对所有程序员透明

主存和辅存由硬件和操作系统实现。虚拟存储技术解决主存容量不足的问题。对系统程序员不透明。对应用程序员透明。

cache容量过小的原因是控制应硬件开发成本。

3.2 主存储器

主存储器由

DRAM和ROM组成。cache由SRAM组成。

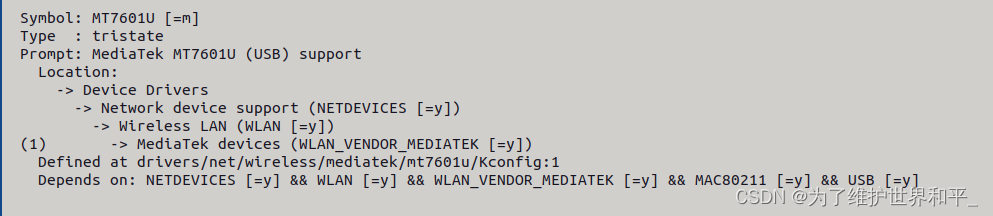

3.2.1 SRAM芯片和DRAM芯片

1.SRAM的工作原理

SRAM由双稳态触发器存储信息,信息读出后不会丢失。

特点:存储速度快,集成度低,功耗大,价格昂贵。用于高速缓冲存储器。2.DRAM的工作原理

DRAM由MOS管存储信息,读出会破坏数据,同时电荷也容易丢失,所以需要刷新再生。

特点:集成度高,价位低,容量大,功耗低。用于主存储器。

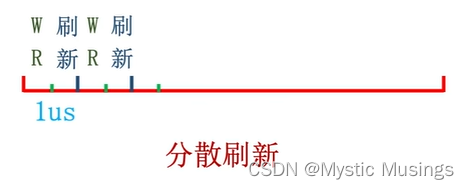

刷新方式:【每次刷新占用一个存取周期。以一行为刷新周期】①分散刷新:

- 每次存取完后就刷新。

存取周期变成了原来的2倍。 - 优点:

无死区 - 缺点:延长系统存取周期

- 每次存取完后就刷新。

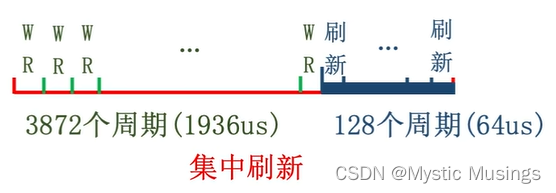

②集中刷新

- 设刷新周期为T,存取周期为t。

刷新周期包含T/t个存储周期。设r为DRAM芯片的行数。前T-r个存储周期用于刷新操作,后r个存取周期用于正常存取操作。 - 优点:读写操作不受刷新工作影响

- 缺点:存在不能访问访存的

死区

- 设刷新周期为T,存取周期为t。

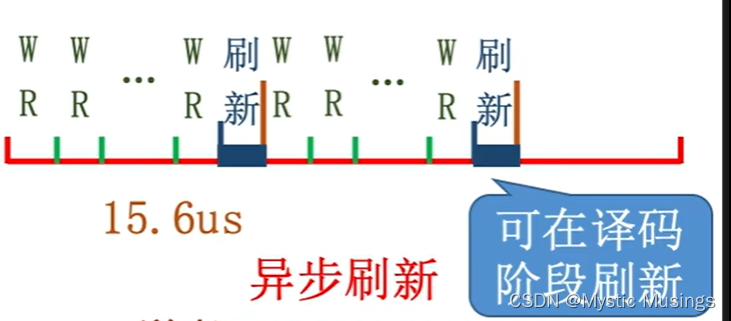

③异步刷新

- 设刷新周期为T,存取周期为t,r为DRAM的行数。以每T/r个存取周期刷新没有刷新的一行。

- 优点:缩短死时间。

注意事项:①刷新对CPU透明 ②DRAM刷新单位是行 ③刷新占用一个存取周期

- 3.SRAM和DRAM对比

| SRAM | DRAM | |

|---|---|---|

| 存储信息 | 触发器 | 电容 |

| 破坏性读出 | 非 | 是 |

| 需要刷新 | 不要 | 需要 |

| 送行列地址 | 同时送 | 分两次送 |

| 运行速度 | 快 | 满 |

| 集成度 | 低 | 高 |

| 存储成本 | 高 | 低 |

| 主要用途 | cache和快表 | 主存 |

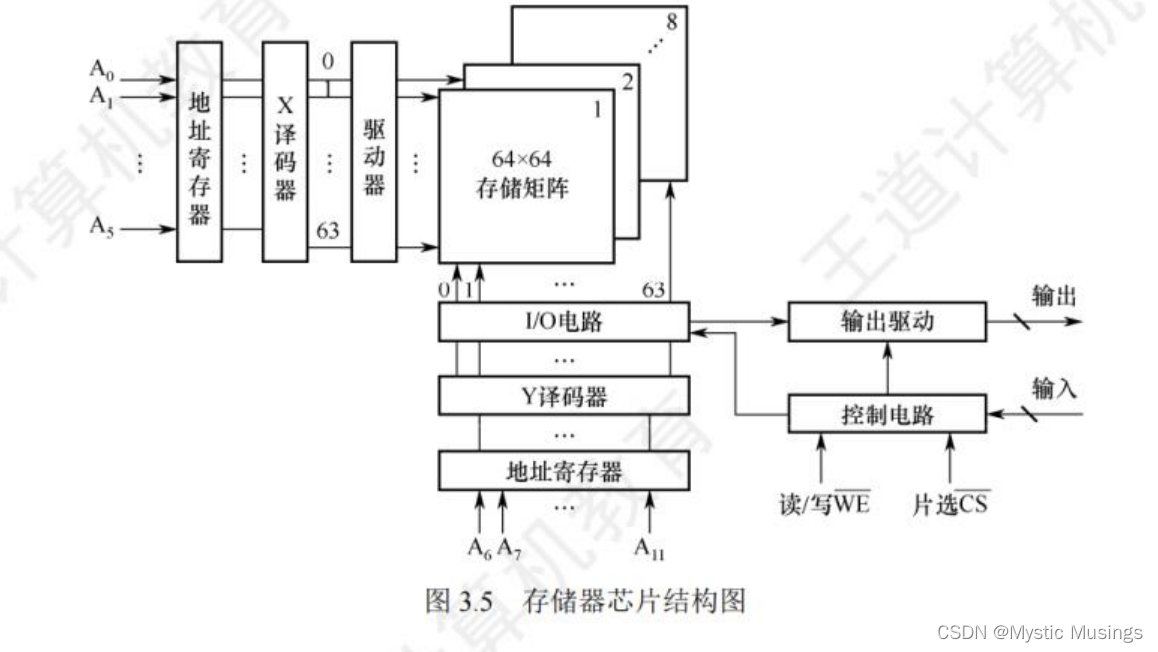

- 4.存储器芯片内部结构

①存储体

②地址译码器

③I/O控制器

④片选信号 【选择芯片】

⑤读写控制信号 【发出读写信号】

3.2.2只读存储器

1.只读存储器的特点 (重点内容)

①支持随机存储

②结构简单

③读写速度较慢

④断电不丢失信息2.ROM类型

- 1.掩模式只读存储器【写后不能修改】

- 优点:可靠性高,集成度高,价格便宜

- 缺点:灵活性差

- 2.一次可编程只读存储器【允许写入一次后不能修改】

- 3.可擦除可编程只读存储器【可以多次擦除重写,

不能代替RAM(重写次数有限)】 - 4.Flash存储器【断电不丢失,可以快速擦除重写】

- 5.固态硬盘【基于Flash,比传统机械硬盘快】

- 1.掩模式只读存储器【写后不能修改】

3.2.3主存储器的基本组成

芯片引脚判断:

- DRAM:

数据线+地址线(地址线复用)+读写线(1根/2根)+行通选线(1根)+列通选线(1根) - SRAM:

数据线+地址线+读写线(1根/2根)+片选线(1根)

3.2.4 多模块存储器

- 1.单体多字存储器

一行包含多m个字,总线宽度也是m个字,一次并行读出m个字。

缺点:不能读取单个字

优点:读取同一个存储单元更快 - 2.多体并行存储器

灵活性更高。

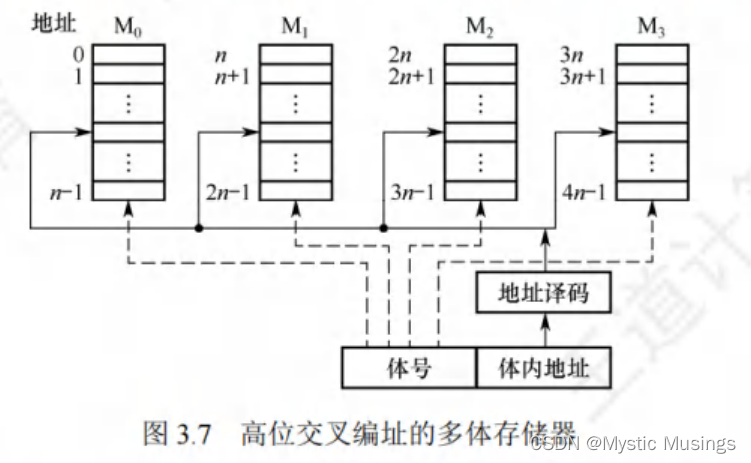

(1) 高位交叉存储器(顺序方式)【使用高位表示存储模块编号】

相当于仅仅扩容。

相邻地址在同一个存储体中。

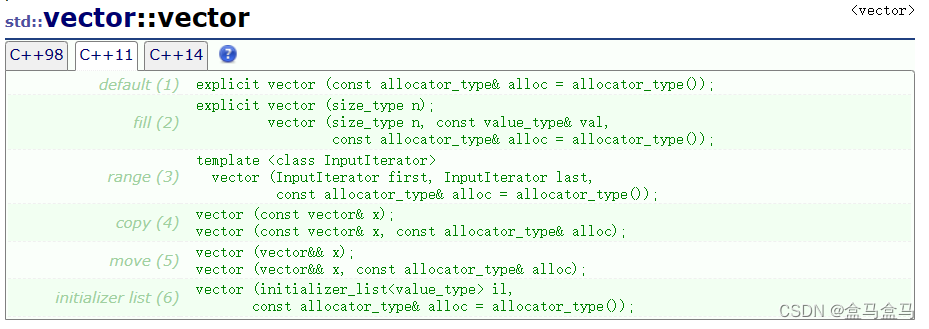

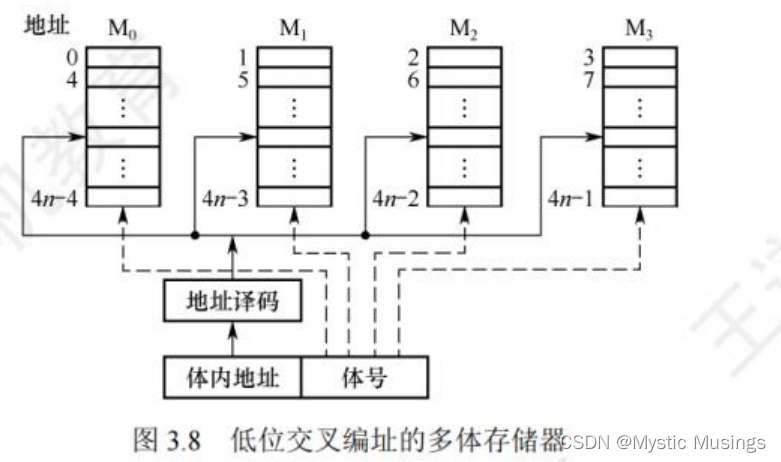

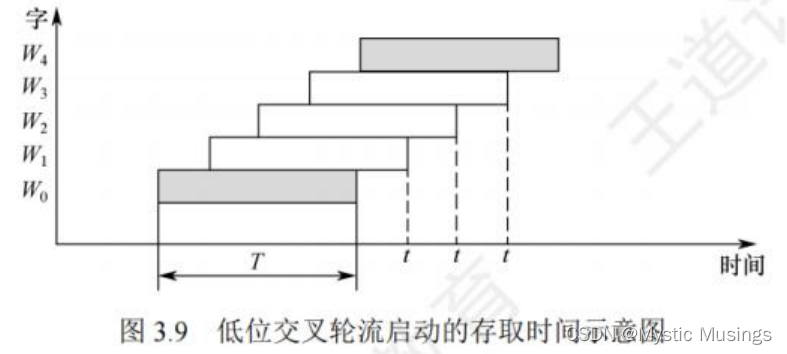

(2) 低位交叉存储器(交叉)【使用低位表示存储模块编号】

性能更高。扩容+读写速度提升

相邻地址在不同的存储模块中,因此连续读取地址的数据不需要等待恢复时间。

设存取周期为T,存取时间为r,为了使流水线不间断,模块数m≥ T r 。 \frac{T}{r}。 rT。

![[408计算机组成原理] <span style='color:red;'>第</span>三<span style='color:red;'>章</span> <span style='color:red;'>存储</span><span style='color:red;'>系统</span>](https://img-blog.csdnimg.cn/direct/11de7a5b82c2465a85d0bd7380867802.png)