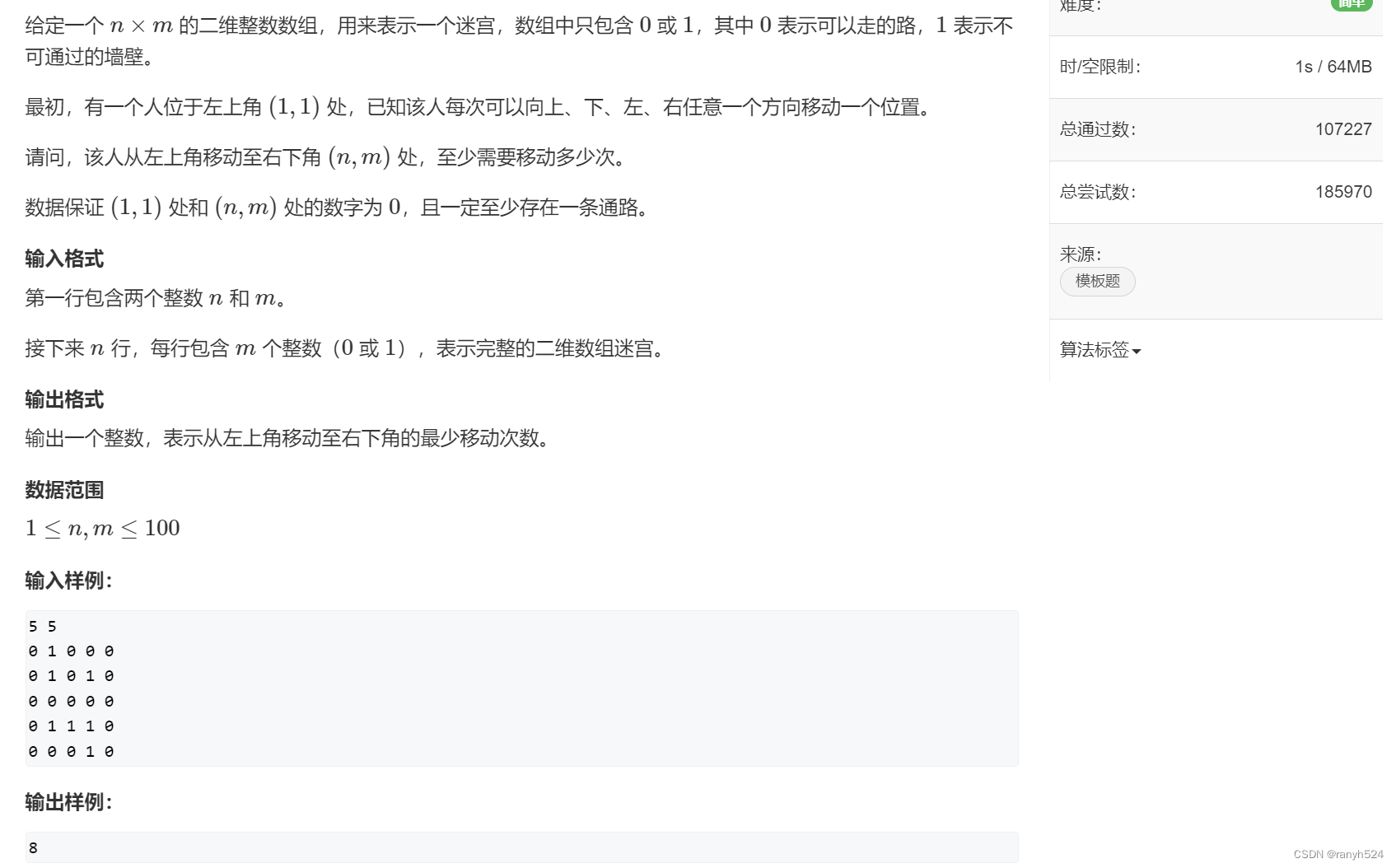

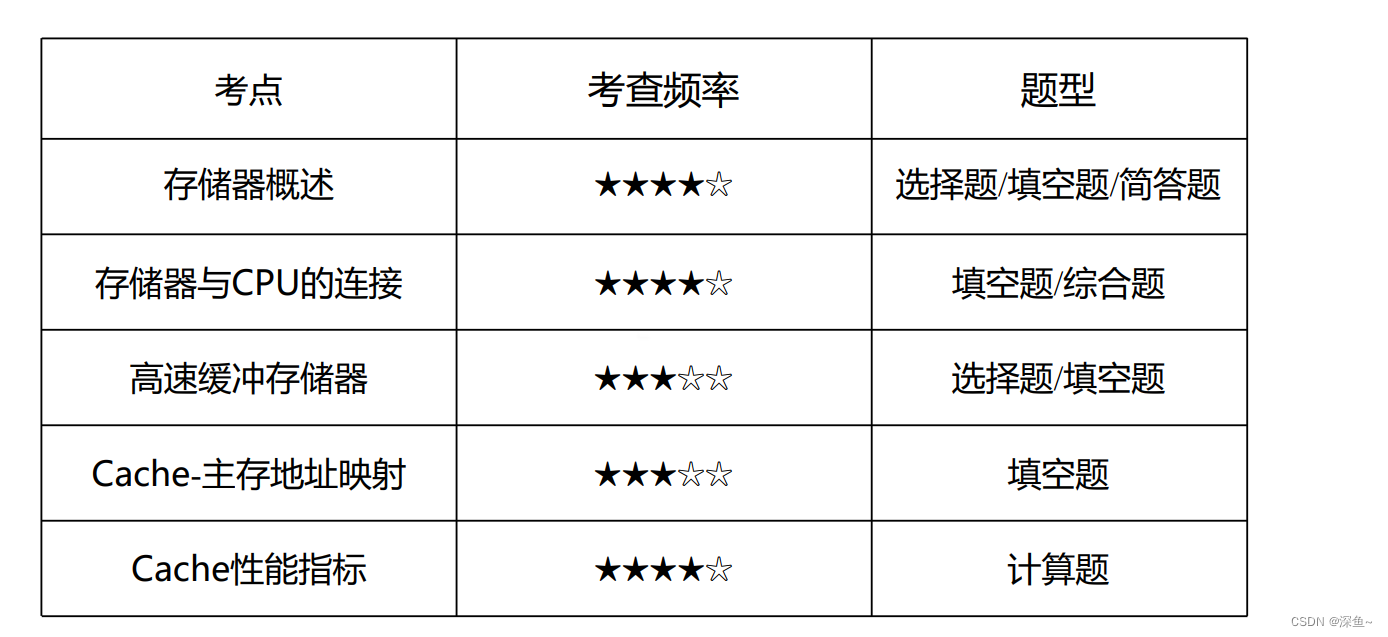

一、存储器的概述

🚀【考纲要求】存储器的分类,层次化存储器的基本结构

1.1存储器的分类

给出不同的分类标准,就可以进行不同的分类

1)按着在计算机中的层次结构分类

- ❀主存储器:就是我们常说的内存,它可以和高速缓存和辅助存储之间交换数据,CPU可直接与主存中交换数据; 特点:容量较小,单位价格贵,存取速度较快。

- ❀辅助存储器:就是我们常说的外存,它不可以和CPU交换数据,辅助存储器中存储的数据被调入主存后才可被CPU访问;特点:容量大,单位价格低,存取速度较慢。

- ❀高速缓冲存储器(Cache):经常被使用的命令和数据会被提前调入Cache,CPU直接访问Cache得到数据;特点:速度快,容量小,单位价格贵。

2)按着在计算机中的存取方式分类

- ❀随机存储器(RAM):储存器中的任意一个存储单元都可以被随机存取,存取时间和位置无关,读写方便;RAM有DRAM(动态RAM)和SRAM(静态RAM)两类。

- ❀只读存储器(ROM):只能随机读不可写,但是随着技术的发展和用户的需求,其可不可写特性没有保留,ROM它也可以进行随机存取,但存的速度较慢。

需要注意的是ROM只是具有随机存储的特性并不是随机存储器,它和随机存储器最大的区别是ROM断电信息不丢失,RAM断电信息丢失。

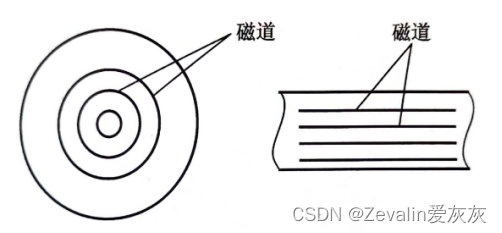

- ❀串行访问存储器:分为顺序存取:磁带 ;和直接存取:磁盘,光盘。

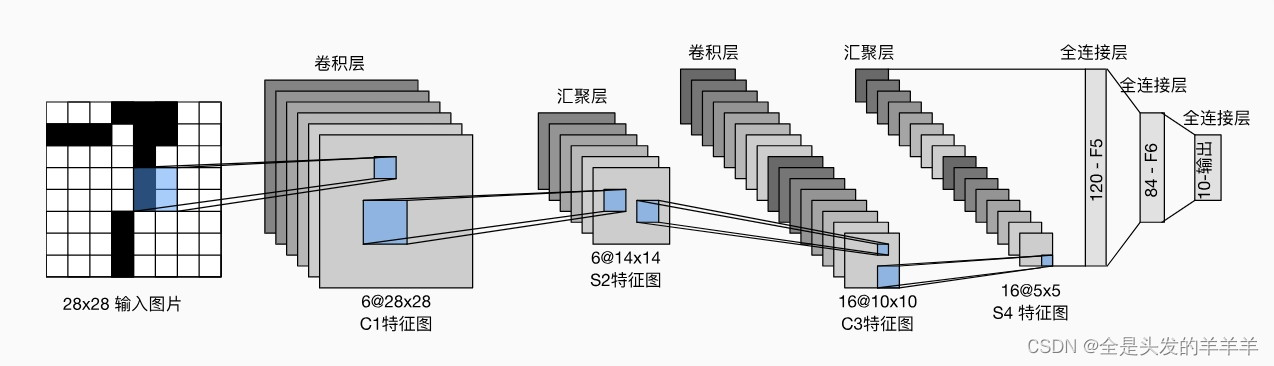

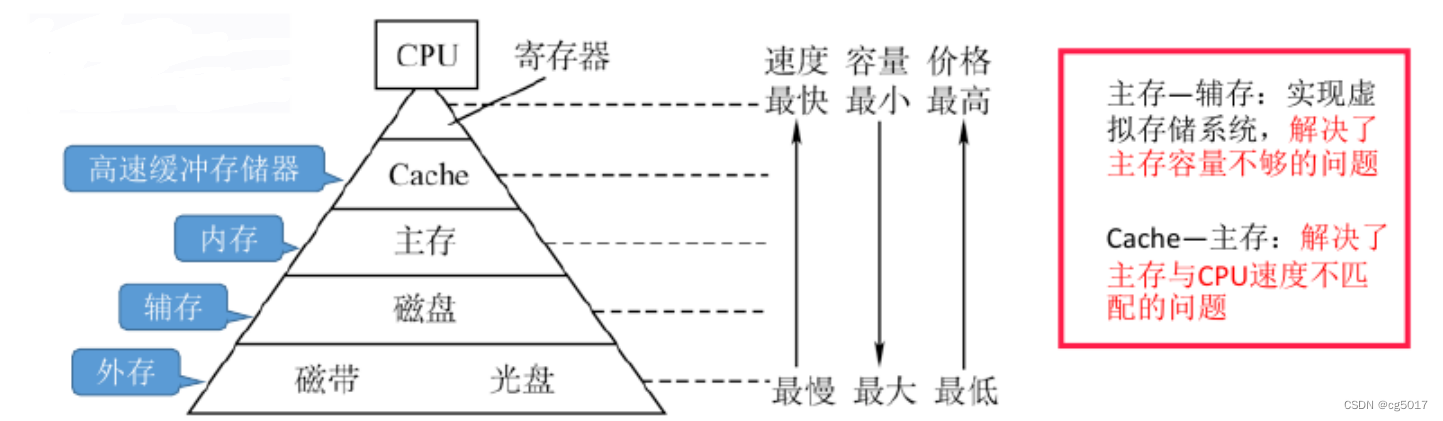

1.2多级层次的存储系统

1)三级存储系统的层次结构

- Cache----主存层 :由硬件直接完成,对所有程序员透明。

- 主存----辅存层:由硬件和操作系统共同完成,对应用程序员透明,对系统程序员不透明。

1)多级存储结构

二、主存储器

🚀【考纲要求】RAM SRAM DRAM Flash存储器 主存储器中的DRAM芯片和内存条,多模块存储器

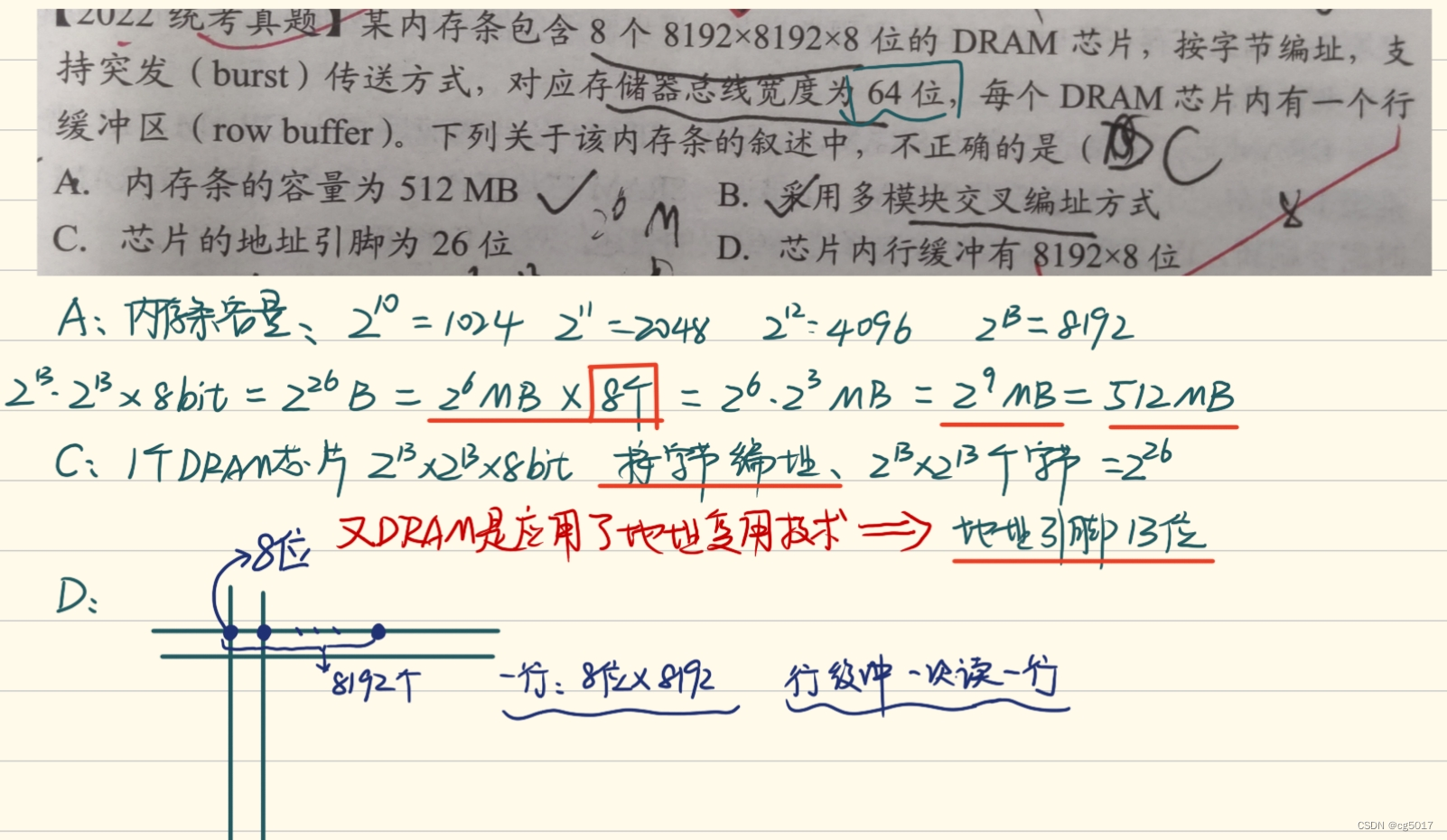

2.1DRAM和SRAM

都是RAM(随机存储器),都具有随机存取的特点,掉电信息丢失。

DRAM的工作原理:

双稳态触发器存储信息,它的存储元为触发器

DRAM的工作原理:

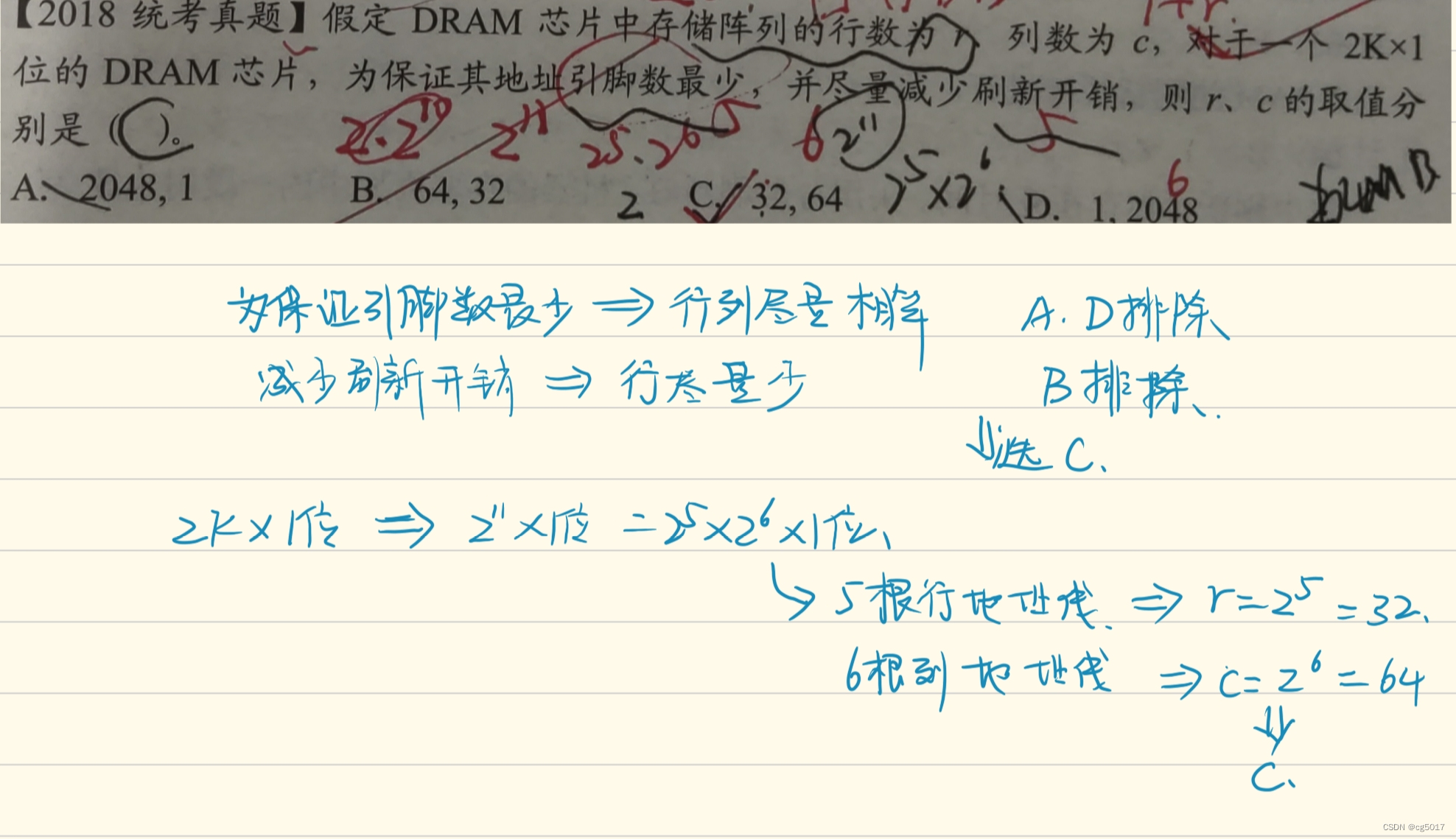

电容存储信息,它的存储元为电容。使用电容存储信息的话,由于电容上的电荷本身会随着时间逐渐减少,所以为了让存储的信息不丢失就要定时的刷新电容,以保证信息不丢失,刷新方式有以下三种

- **集中刷新:**固定在一段时间内刷新,存在死区,死区内不能对存储器进行读写操作。

- **分散刷新:**一次存取结束刷新一次,无死区,是一种过度刷新。

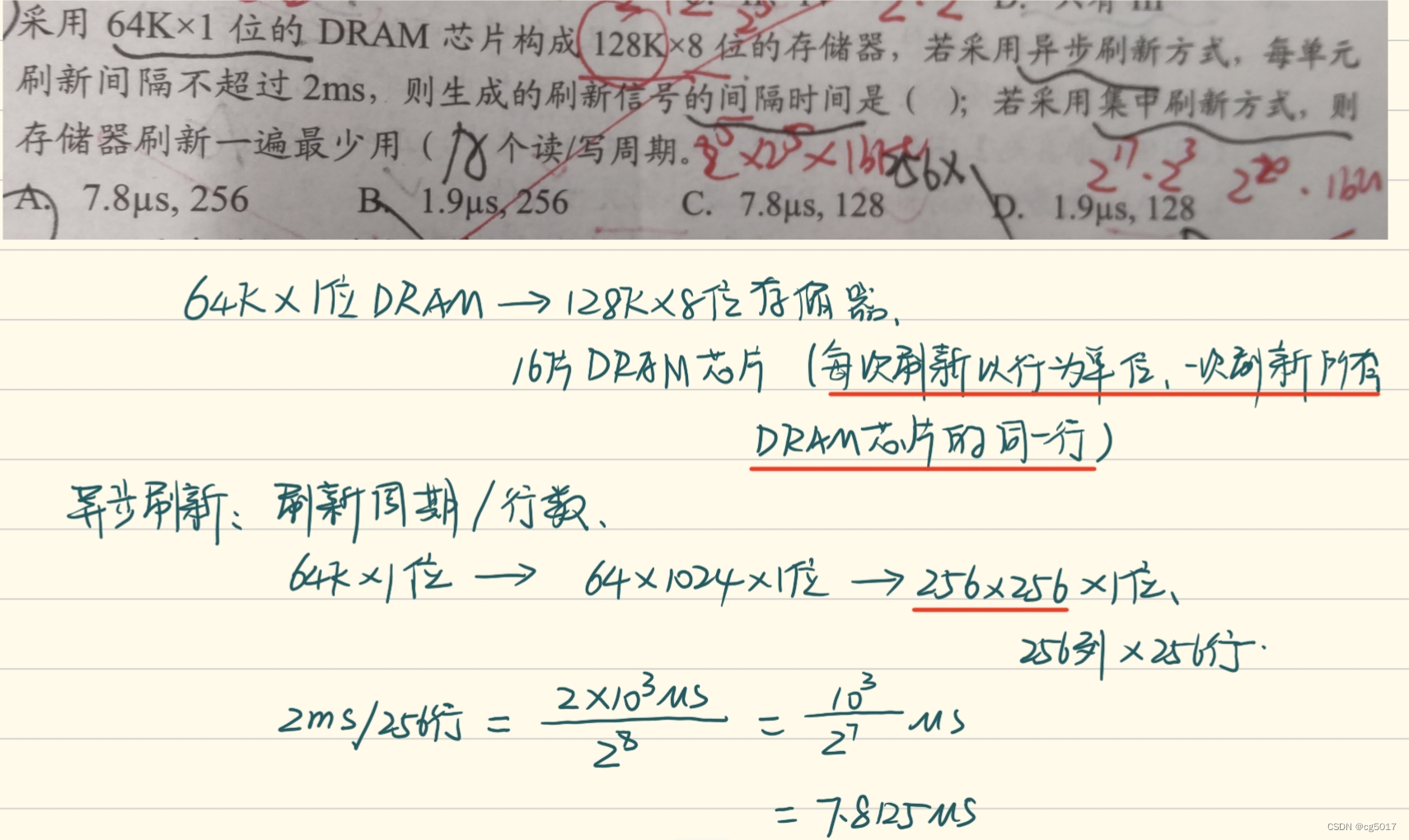

- **异步刷新:**使用一个刷新周期/DRAM芯片的行数=每一行刷新的最小时间间隔。让死区时间分散,避免让CPU等待时间太长。

DRAM的刷新以行为单位刷新;刷新操作类似于读的操作,但又有所不同;同时刷新时不需要片选,即整个存储器中的所有芯片的同一行同时被刷新。

目前更常用的时SDRAM(同步动态RAM),传统的动态RAM和CPU进行数据交换时异步于时钟信号的,而SDRAM(同步动态RAM)和CPU之间的数据交换是同步的。SDRAM支持突发式传送,即CPU给出读取的首地址,同一行所有的数据会被送至行缓冲器,所以之后的每个时钟周期都能连续的从行缓冲器中读取一个数据。(在总线第一节中,也学习到了突发式传送。总线的传输方式被分为了两种方式:①非突发式传送:每一次读取一个字长的数据,先给出数据地址,再准备数据,再传送数据;②突发式传送:只给出首地址,准备数据,连续传送数据,直到完成释放总线。)

2.2DRAM和SRAM的对比

| 特点 \ 类型 | SRAM | DRAM |

|---|---|---|

| 存储元 | 触发器 | 电容 |

| 是否刷新 | 否 | 是 |

| 速度 | 快 | 慢 |

| 价格 | 高 | 低 |

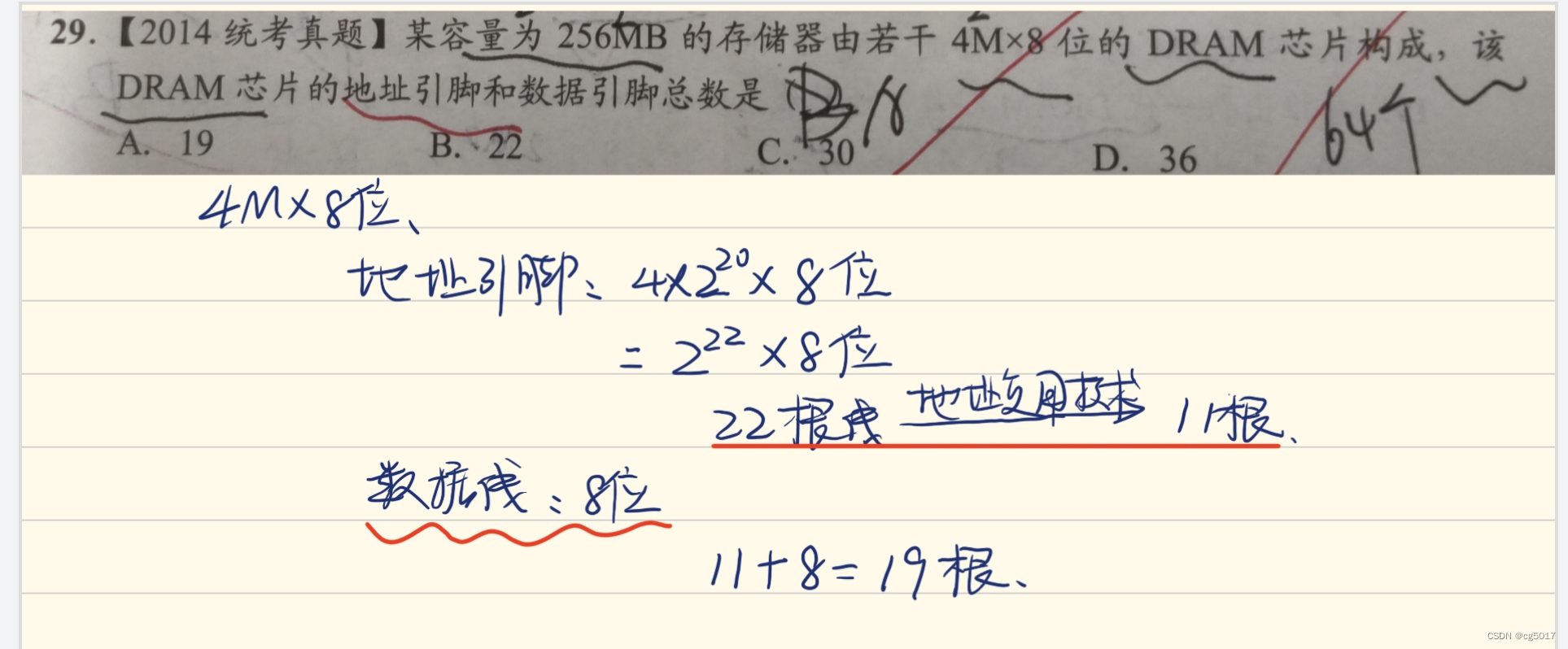

| 地址传送 | 同时送送 | 两次(地址复用) |

| 集成度 | 低 | 高 |

| 用途 | Cache | 主存 |

2.3只读存储器(ROM)

ROM和RAM都支持随机存取,ROM是非易失性其间,RAM是非易失性器件。ROM的分类如下

- MROM:无法修改内容,出厂里面的信息就被写好了。

- PROM:可以一次性编程,只可以写一次。

- EPROM:可多次写,但是不可取代RAM,因为其速度慢,且写的次数有限,写次数太多会坏。

- Flash存储器:兼具RAM和ROM的特点,由EPROM发展而来。

- SSD固态硬盘:基于Flash存储器,由控制电路和Flash芯片发展而来。价格较高。

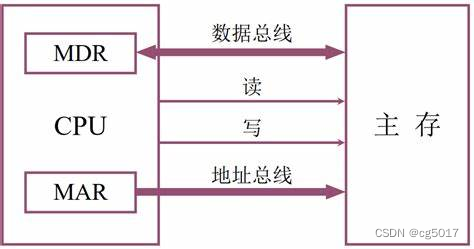

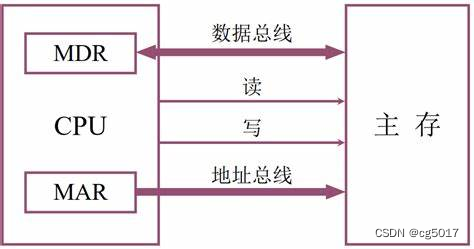

2.4主存储器的基本结构

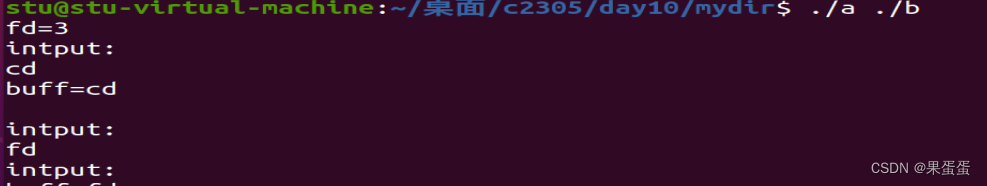

读过程: CPU即将要访问数据的地址送至MAR(地址寄存器),由地址译码电路译码,选中即将要操作的数据单元,再由CPU给出的读命令控制主存将译码地址中的内容通过数据线传至MDR(数据寄存器)中,CPU从MDR中取得它这次要访问的数据

写过程: CPU即将要访问数据的地址送至MAR(地址寄存器),由地址译码电路译码,选中即将要操作的数据单元,再将要写的内容送至MDR,再由CPU给出的写命令控制MDR(数据寄存器)中的内容写入选中单元。

MAR的位数反应了最大的一个寻址范围,即地址线的位数;MDR的位数反应了数据线的位数。(通常存储字长也等于MDR的位数)

DRAM芯片制作主存,其会采用引脚复用技术,行地址和列地址采用时序加控制的方式依次传送行列地址。 使得其引脚数大大减少;同时为使引脚数量少的话就尽量让行地址线和列地址线相同,为使得刷新代价小,应尽量减少行的数量,因为DRAM的刷新是以行为单位进行的。

2.5多模块存储器

多模块存储器的目的是为了提高访存速度的,对于提高访存速度的措施有以下几种

- 采用更加高速的器件

- 采用层次结构(Cache——主存)

- 改变主存的存储结构----多模块存储器(一种空间并行技术)

2.5.1单体多字存储器

就是一个存储体里面放多个字,假设一个存储体里可以放n个字,那么总线的宽度就也设置为n个字,一次访存读取操作就可以读出n个指令,将这n个指令依次送CPU执行。简单就是说一次访存多拿几个字。

缺点: 命令和数据必须得连续存放,若要不是连续存放,取出来的都不是CPU想要的指令或者数据,还得重新读取,一旦遇到跳转指令较多的程序,速度提升几乎就不起作用了。

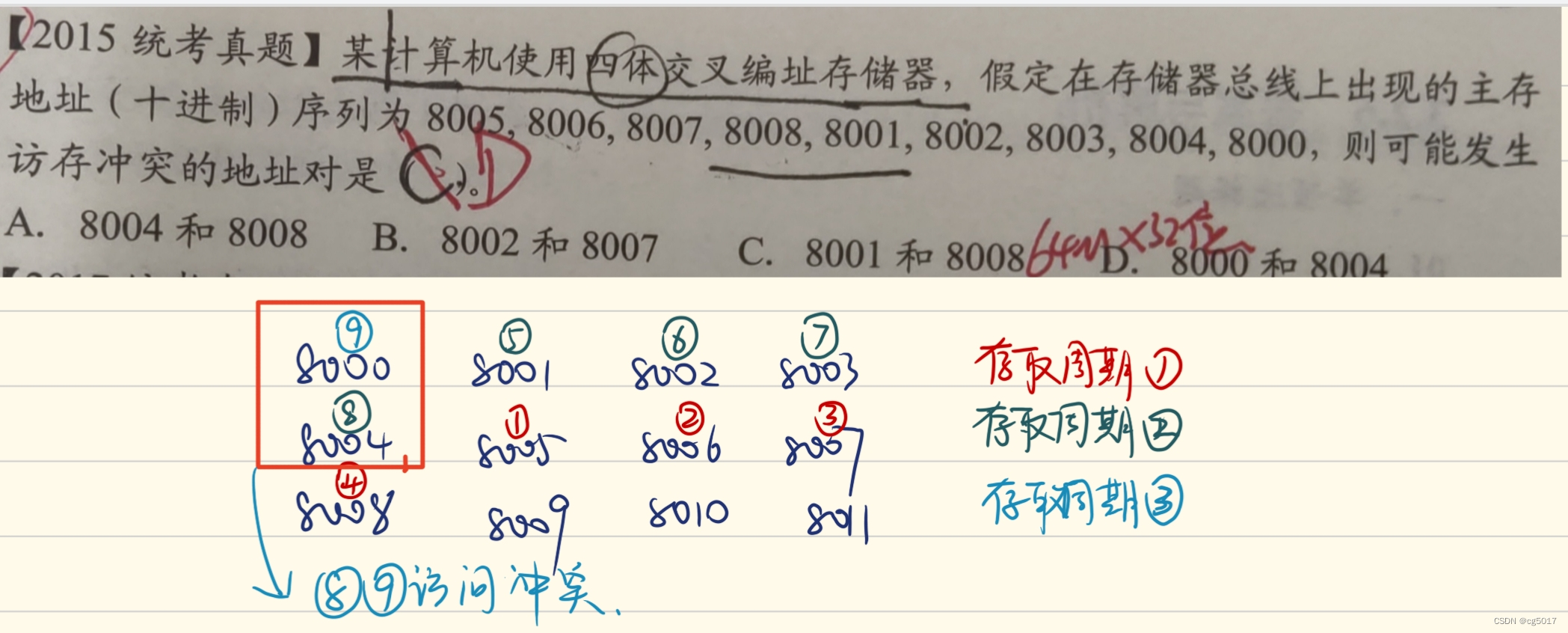

2.5.1多体并行存储器

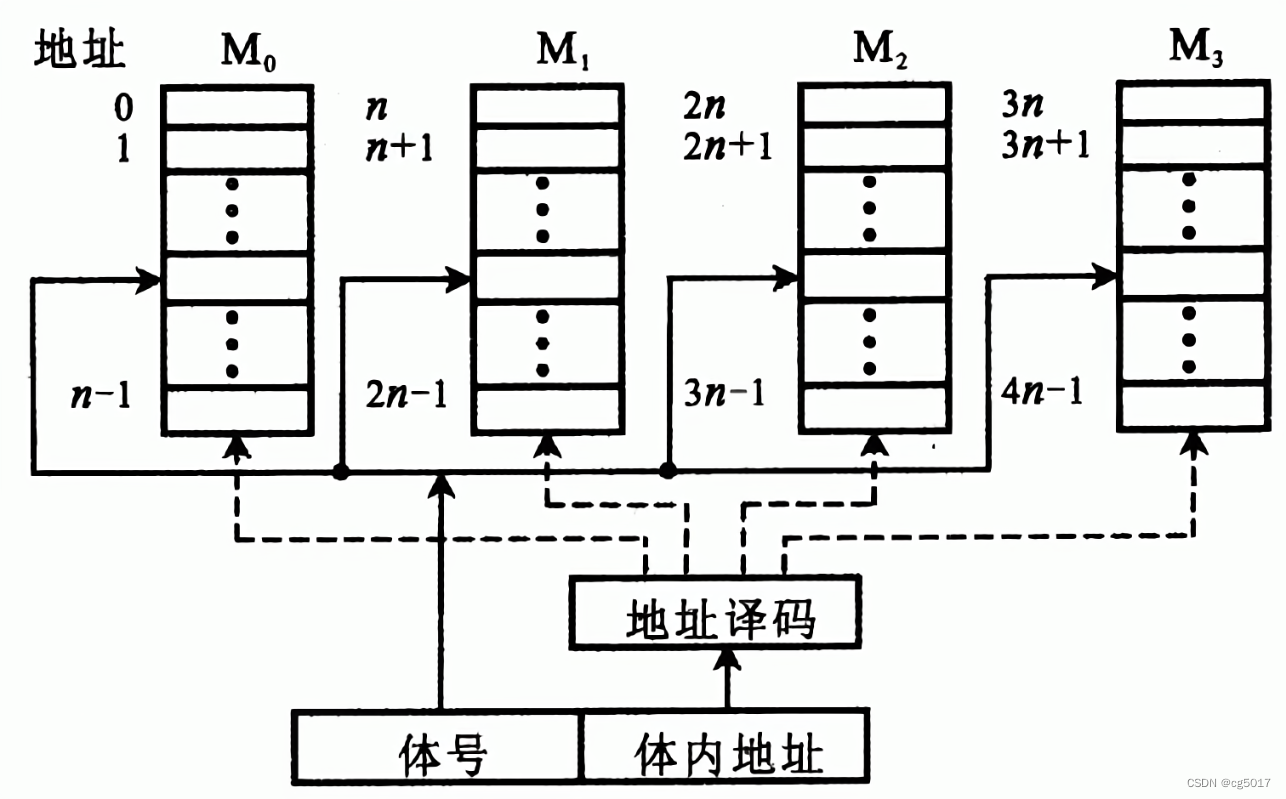

①高位交叉/顺序方式(高位表示体号,低位表示体内地址)

根据程序局部性原理来说:指令会依次执行,假设程序的起始地址是000000,接下去的下一条指令大概率就是000001的位置,接下去是000010,000011~~~的位置,而这时每次访问的都是 M 0 M_0 M0存储体。所以各模块不能被并行访问,不能提高存储器的吞吐率。

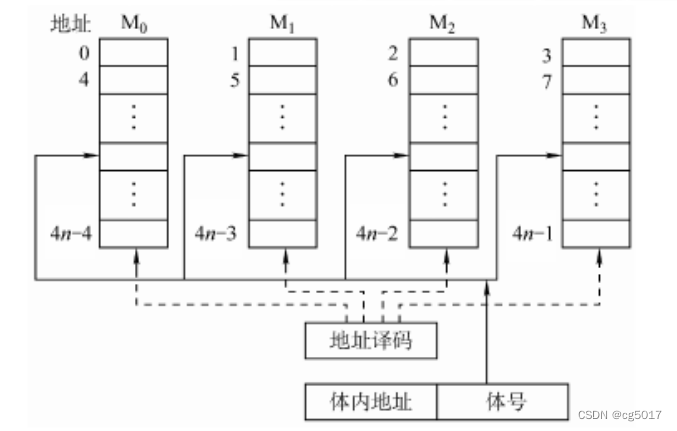

②低位交叉/交叉方式(低位表示体号,高位表示体内地址)

同样指令会依次执行,假设程序的起始地址是000000,接下去的下一条指令大概率就是000001的位置,接下去是000010,000011~~~的位置,而这次是依次访问 M 0 M_0 M0、 M 1 M_1 M1、 M 2 M_2 M2、 M 3 M_3 M3存储体。所以各模块被并行访问。

对于低位交叉/交叉方式来说,其每个存储体的启动时间可以不同,按着存储体启动方式的顺序分为

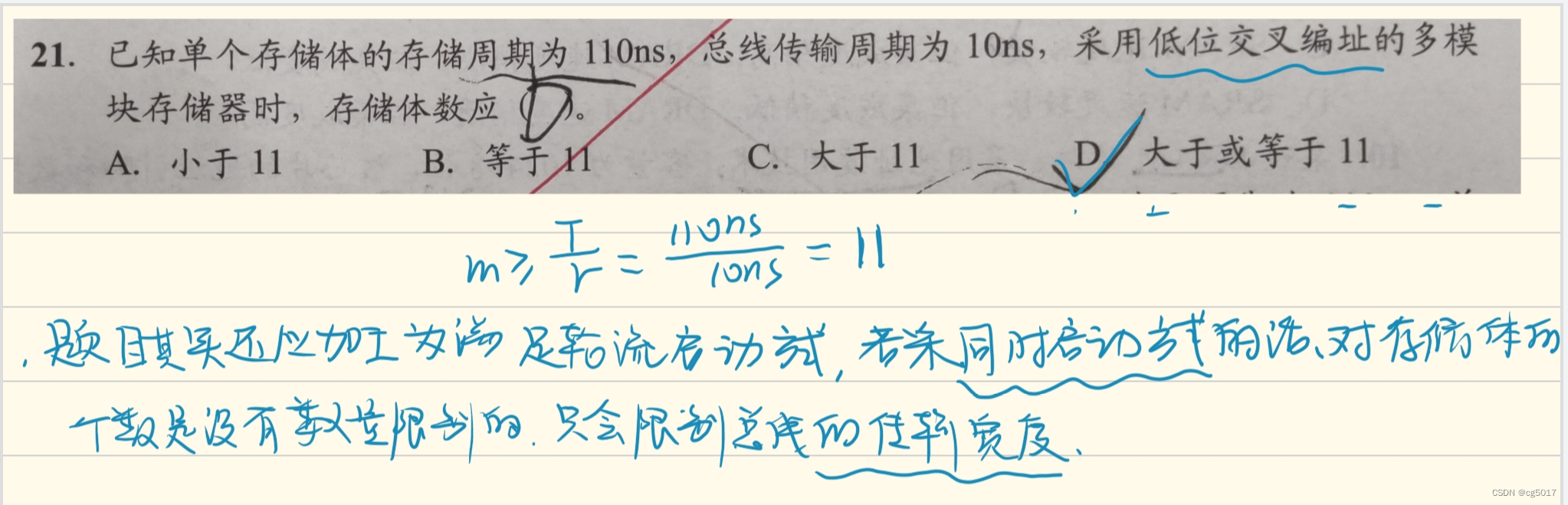

- 轮流启动方式:每个模块一次读写的位数刚好等于总线位数 ;对于轮流启动方式来说,假设存储周期是 T T T,总线周期是 r r r,那么为了实现存储轮流启动方式,其交叉模块数量至少为 T / r T/r T/r。

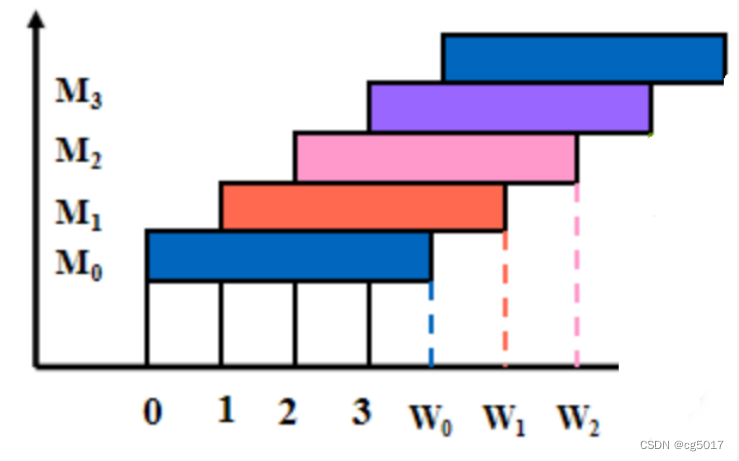

对于轮流启动方式,若存取周期是 T T T,存储体的个数为 M M M个,每间隔 T / M T/M T/M时间轮流启动 M 0 M_0 M0、 M 1 M_1 M1、 M 2 M_2 M2、 M 3 M_3 M3存储体。每间隔 T / M T/M T/M时间就会从被选中的存储中读出一个存储字长的数据。连续读 m m m个字的时间为 t 1 = T + ( m − 1 ) ∗ r t_1=T+(m-1)*r t1=T+(m−1)∗r r = T / M r=T/M r=T/M若要读2个字得花费下图的 W 1 W_1 W1的时间。

轮流启动方式还会出现访问冲突,模块被访问一次后需等待一个存取周期才能被访问,若未等待一个存取周期就访问,就会发生访问冲突。

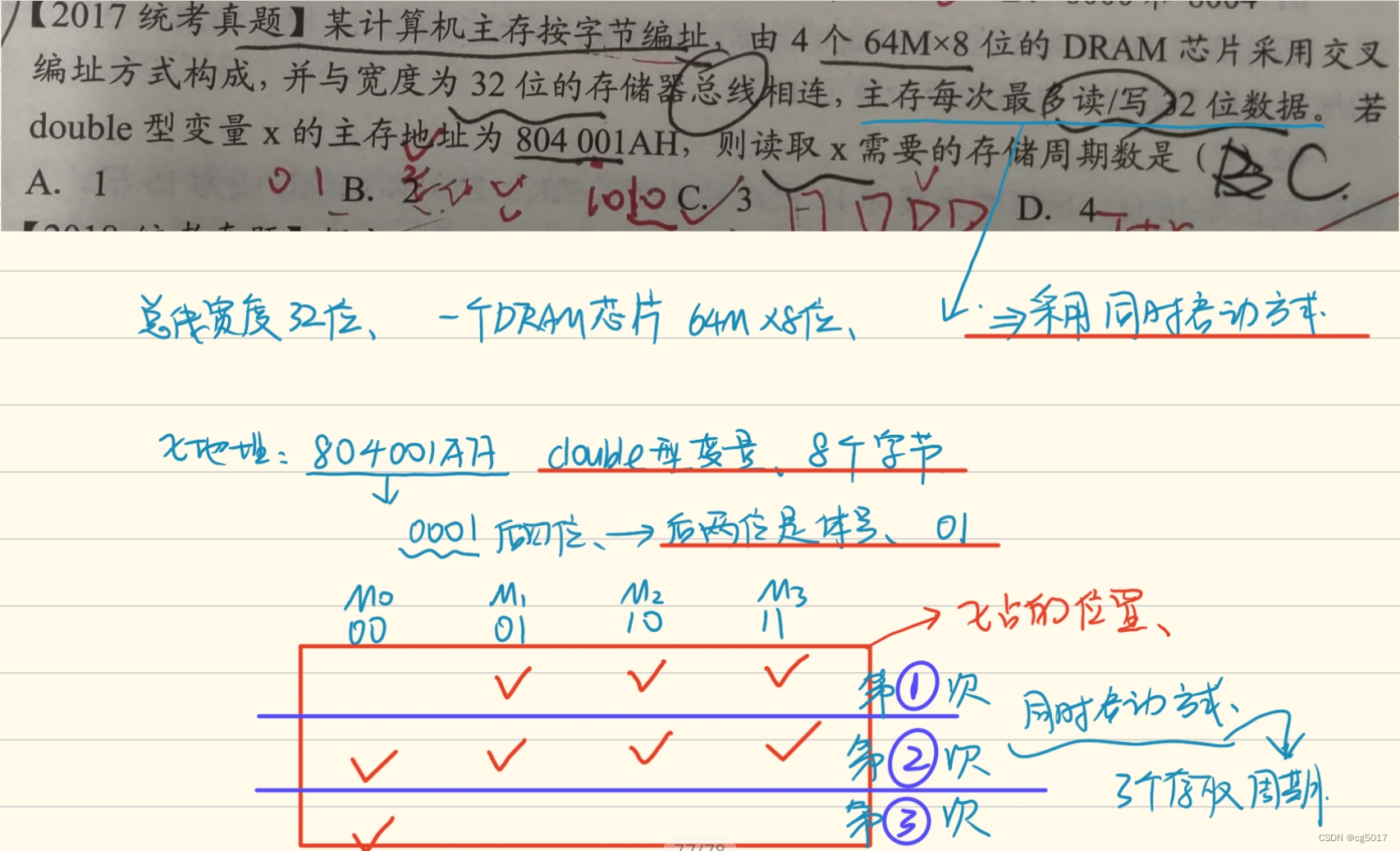

2. 同时启动方式:每个模块同时一次读写的位数刚好等于总线位数

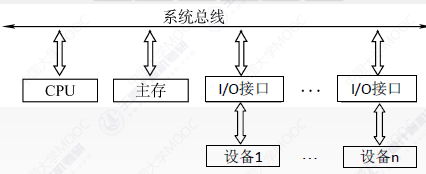

三、主存储器和CPU之间的连接

🚀【考纲要求】主存储器中的主存储器和CPU之间的连接

仍然是下面这张图片,很清晰的展示的主存储器和CPU之间的连接关系。

在这里强调的更多的是对于主存容量扩展后其和CPU地址线的一个连接以及扩展后其和CPU数据线的连接,先学习的是主存的扩展,三种方式。

3.1主存容量的扩展

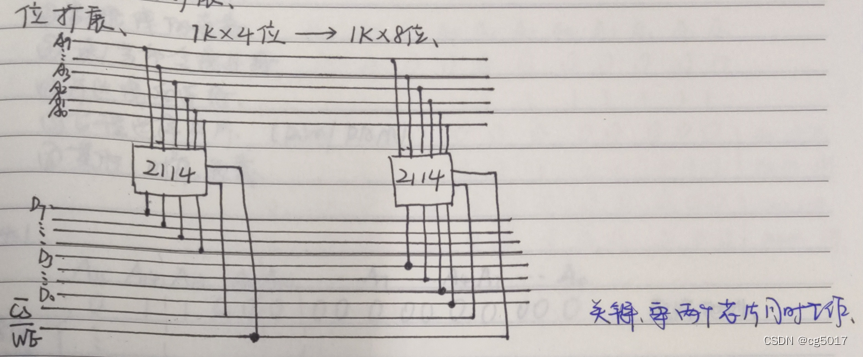

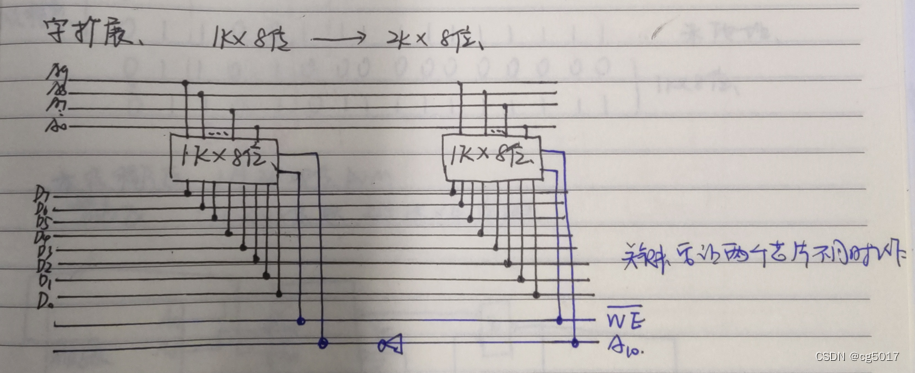

①位扩展

位扩展的关键:让多个芯片同时工作

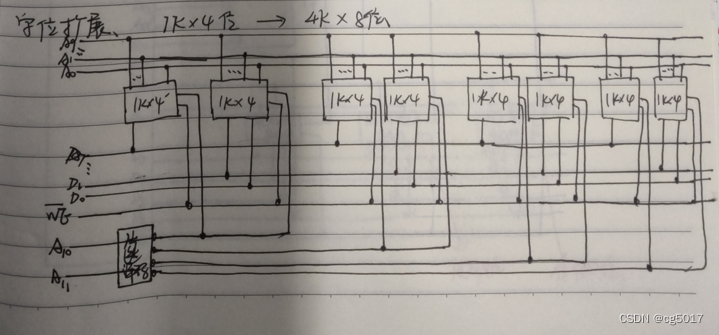

②字扩展

字扩展的关键:让多个芯片不同时工作

③字位同时扩展

先位扩后字扩

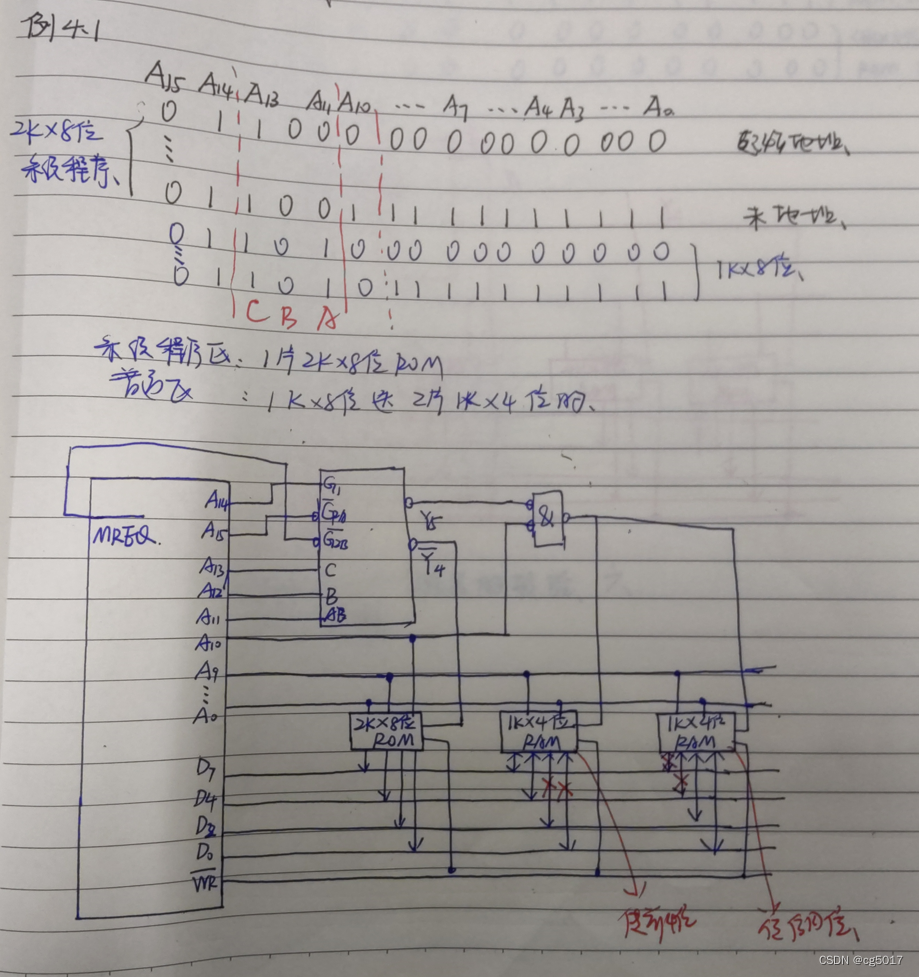

3.2存储芯片的地址分配和片选、存储器和CPU的连接

①地址分配和片选

CPU实现对主存特定位置的访问,首先片选芯片或芯片组,然后再选择芯片内部的具体的存储单元。

片选的方式: 线选法、译码片选法

②存储器和CPU的连接

- 合理选择芯片。存放系统程序选ROM,普通区选RAM。

- 地址线和CPU的连接

- 数据线的连接

- 读/写命令线的连接(¬RD和¬WE,都是低电平有效)

- 片选线的连接(不可忘¬MREQ)

四、外存储器

🚀【考纲要求】磁盘存储器 固态硬盘SSD

还未学,之后补充!!!!!

五、高速缓冲存储器

🚀【考纲要求】Cache的基本原理;Cache和主存之间的映射方式;Cache中主存块的替换算法;Cache的写策略

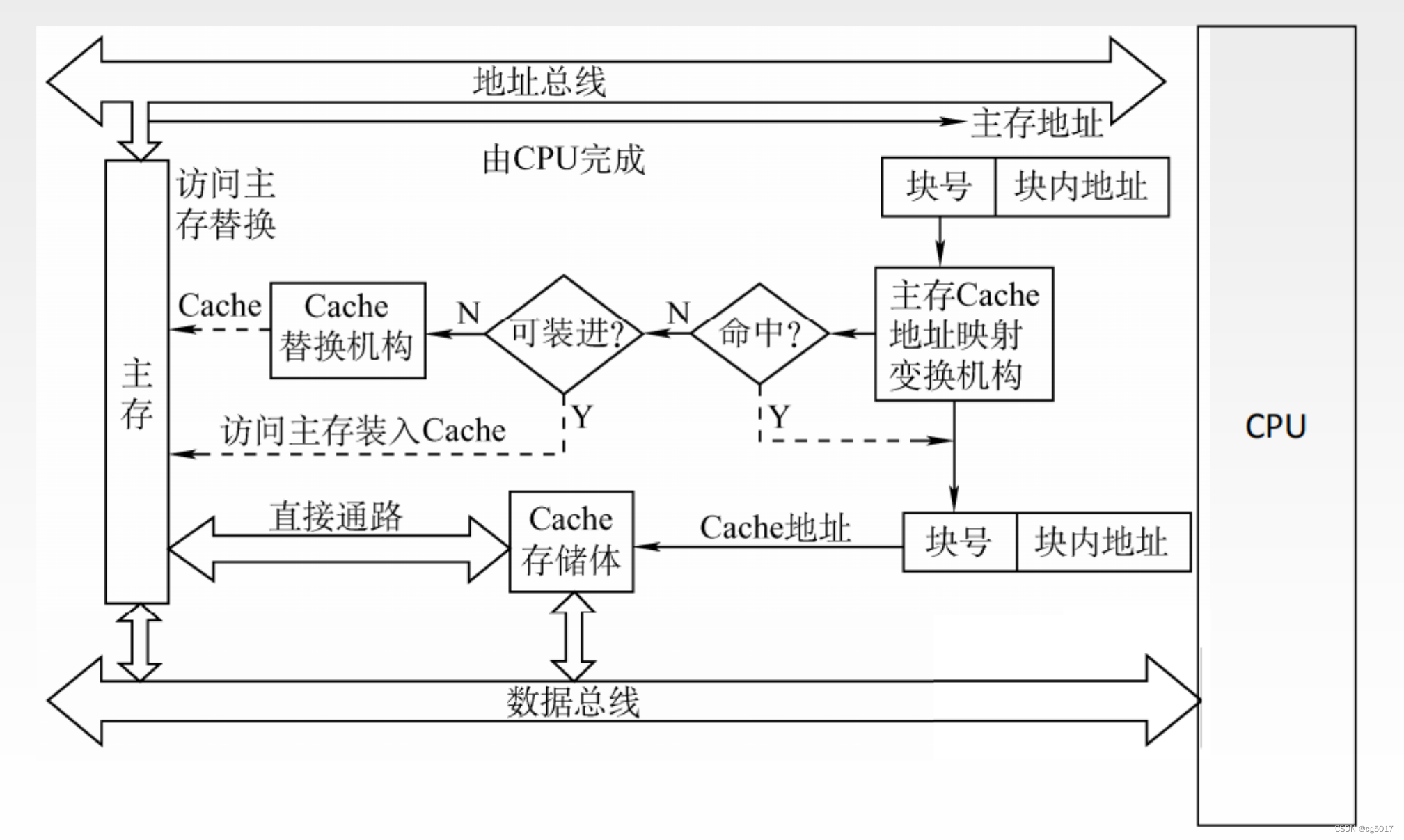

5.1Cache的基本原理

CPU发出读操作: CPU通过地址线给出地址,Cache映像变换机构将主存地址与Cache中的进行比对,命中直接读,未命中判断Cache是否满,未满装进Cacha,满通过Cache替换机构替换,装入新的。(Cache和主存之间以块未单位传送,CPU和Cache以字为单位)

CPU发写读操作: 若Cache命中,向Cache写,此时就会出现Cache和主存内容不一致的问题,此时就需要解决主存和Cache之间的一致性问题。

5.2主存和Cache之间的一致性问题

①全写法:

CPU对Cache写命中,同时将内容写回主存;时时刻刻主存和Cache一致,但是由于会多次对主存写内容,对主存写的速度会慢于对Cache的,即设置了一个写缓冲。

②回写法

在Cache的每行设置一个脏位(修改位),脏位为0,表示数据未被更改过,不需要写回主存;脏位为1,表示数据被更改过,需要写回主存。

5.3主存和Cache之间的映射方式

①全相连

- 优点:命中率高,空间利用率高,冲突率低

- 缺点:标记的比较速度慢,实现成本高

地址结构:

| 标记(主存块号) | 块内地址 |

|---|

②直接相连

- 优点:实现简单

- 缺点:空间利用率低,冲突率高

地址结构:

| 标记(组中第几块) | Cache行号(组号) | 块内地址 |

|---|

③组间相连

是直接映射和全相连映射的综合考虑

组号=主存的块内地址 mod 组数(例:9mod4=1,被放在第一组的任意一个位置)

地址结构:

| 标记 | 组号 | 块内地址 |

|---|

5.4比较器的个数

通常每一个Cache行都设于一个比较器,对于组全相连映射来说N行N个比较器;对于直接映射只需要一个;对于组相连映射,组内有几个Cache行就要几个比较器。

5.5 Cache的标记位

- 替换控制位:LRU的计数器

- 有效位:表示该数据有效

- 脏位:回写法(标记数据有没有被更改)

| 有效位 | 脏位 | 替换控制位 | 标记位 |

|---|

六、虚拟存储器

🚀【考纲要求】虚拟存储器的基本概念;页式虚拟存储器:基本原理、页表、地址变换、TLB(块表);段式虚拟存储器的基本原理;段页式虚拟存储器的基本原理。

操作系统中总结!!!!!

![[<span style='color:red;'>408</span><span style='color:red;'>计算机</span><span style='color:red;'>组成</span><span style='color:red;'>原理</span>] <span style='color:red;'>第</span>四<span style='color:red;'>章</span> 指令<span style='color:red;'>系统</span>4.2](https://img-blog.csdnimg.cn/direct/8d1dffc9e3f74aa29fa2d912a2aa124a.png#pic_center)

![[管理者与领导者-163] :团队管理 - 高效执行力 -1- 高效沟通的架构、关键问题、注意事项](https://img-blog.csdnimg.cn/direct/477f64ff0e2c422b9d4310ed9a6a964b.png)