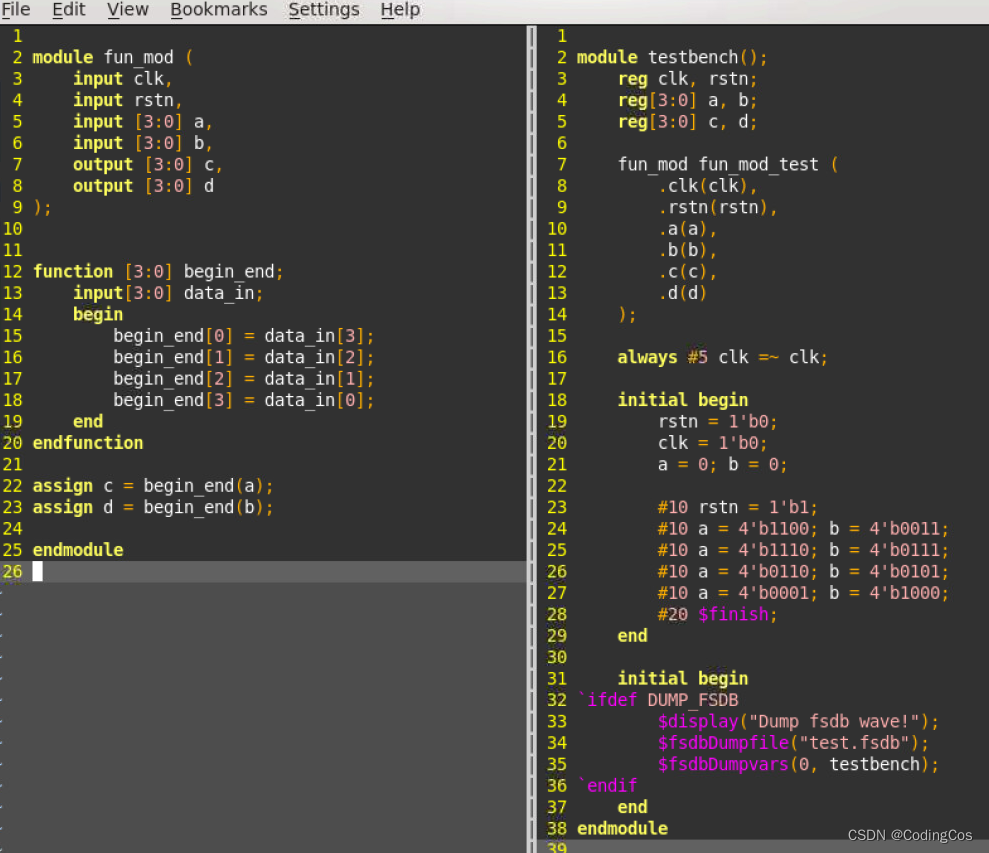

函数实现数据大小端转换

在数字芯片设计中,经常把实现特定功能的模块编写成函数,在需要的时候再在主模块中调用,以提高代码的复用性和提高设计的层次,分别后续的修改。

请用函数实现一个4bit数据大小端转换的功能。实现对两个不同的输入分别转换并输出。

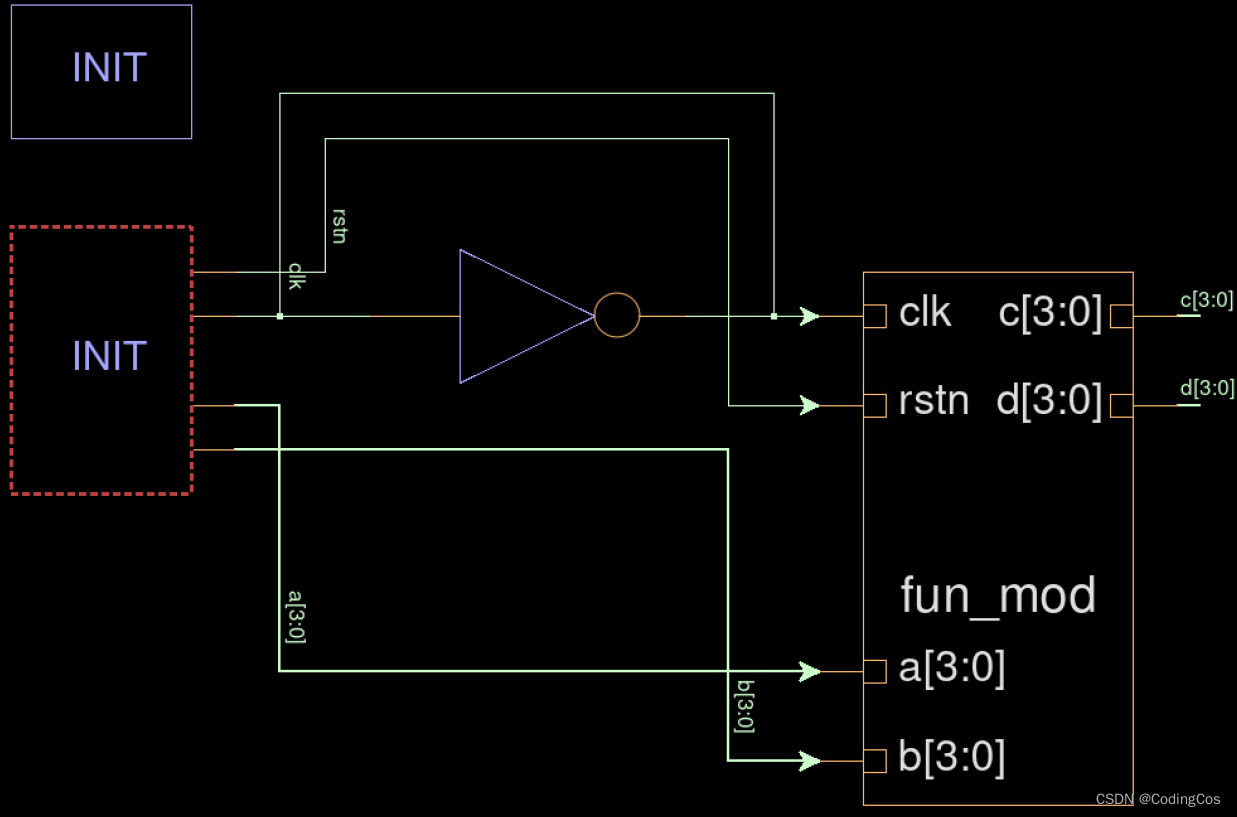

程序的接口信号图如下:

使用Verilog HDL实现以上功能并编写testbench验证。

输入描述:

- clk:系统时钟

- rst_n:异步复位信号,低电平有效

- a,b:4bit位宽的无符号数

输出描述:

- c,d:4bit位宽的无符号数

函数语法

function [range] function_id;

input_declaration

other_declarations

procedural_statement

endfunction

中文版:

function <返回值的类型或范围>函数名;

<端口说明语句>

<变量类型说明语句>

begin

<语句>

end

endfunction

- function 语句标志着函数定义结构的开始;

- <返回值的类型或范围>: 这一项为可选项,如果缺失,则返回值为一位寄存器类型数据,函数名就是返回值,默认是reg类型;

- input_declaration 用于对函数各个输入端口的位宽和类型进行说明,在函数定义中至少要有一个输入端口;

- endfunction为函数结构体结束标志。

函数使用的规则

函数定义不能包含有任何的时间控制语句,即任何用#、@、wait来标识的语句。

函数不能调用“task”。

定义函数时至少要有一个输入参数。

在函数的定义中必须有一条赋值语句给函数中与函数名同名、位宽相同的内部寄存器赋值。

verilog中的function只能用于组合逻辑;

函数中只有组合逻辑,所以函数是可以综合的。

Verilog and Testbench

综合图

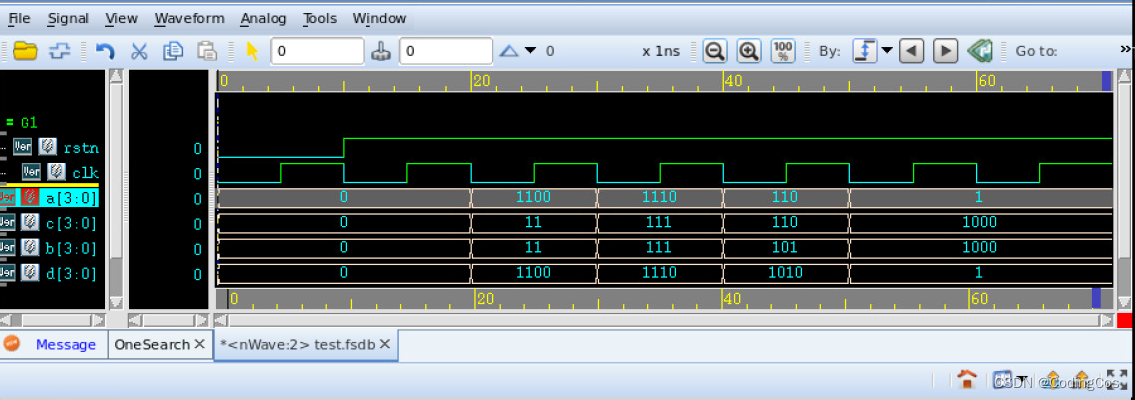

VCS 仿真波形

![[office] excel如何计算毛重和皮重的时间间隔 excel计算毛重和皮重时间间隔方法 #笔记#学习方法](https://img-blog.csdnimg.cn/img_convert/04b2a9eec725fd61a32b994a95e22ca6.jpeg)