【芯片设计- RTL 数字逻辑设计入门 9 -- 异步复位的串联T触发器】

- 开发

- 57

-

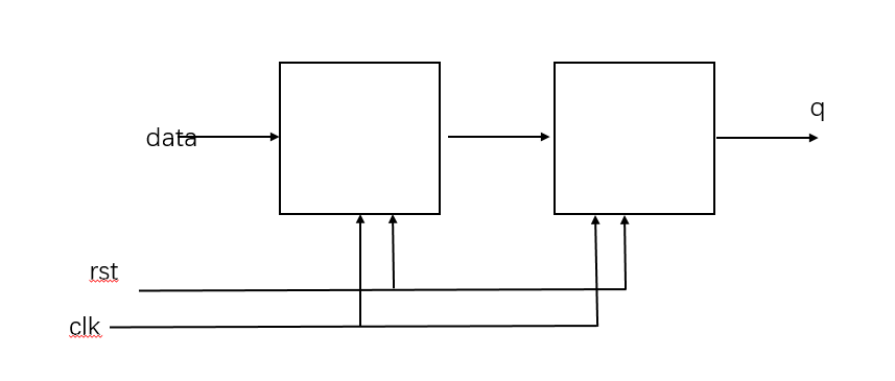

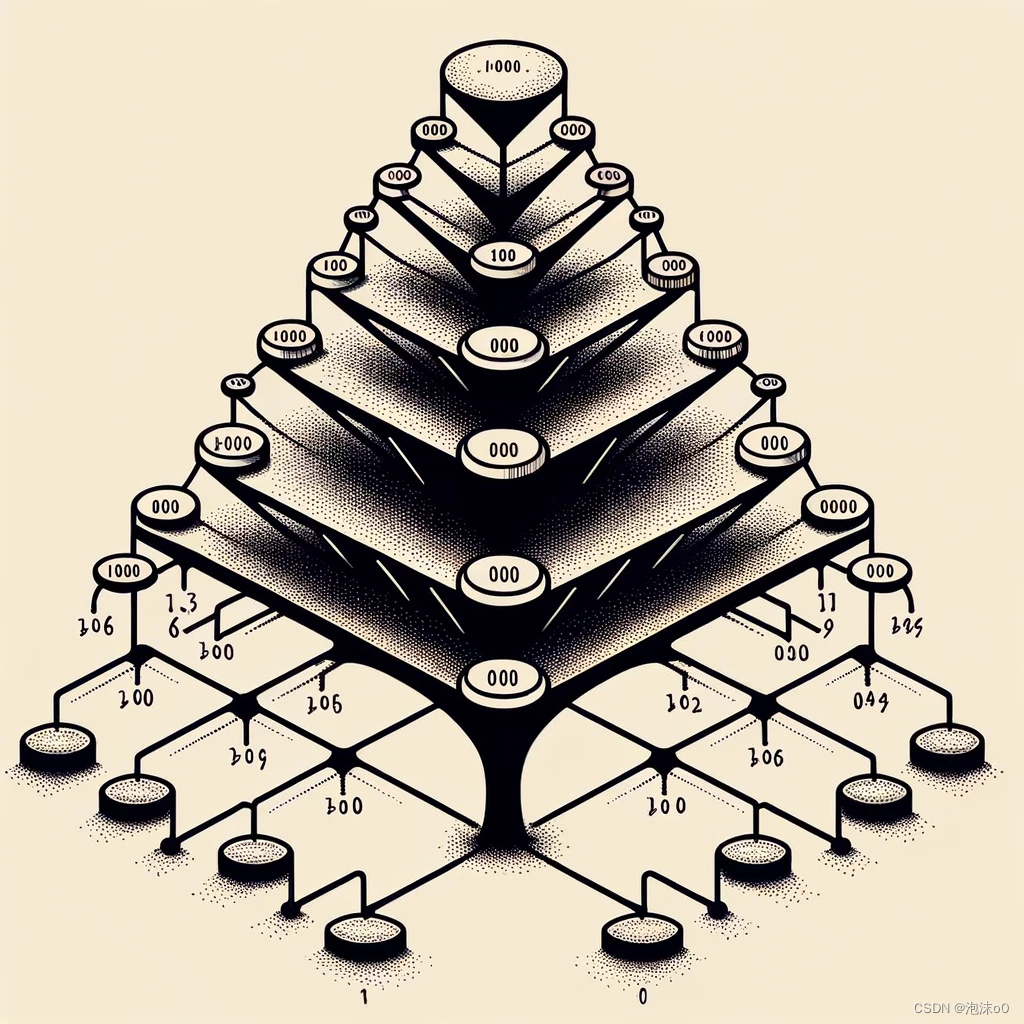

异步复位的串联T触发器

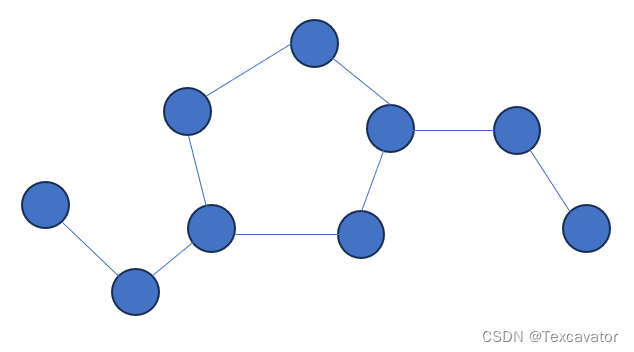

用 verilog 实现两个串联的异步复位的T触发器的逻辑,结构如图:

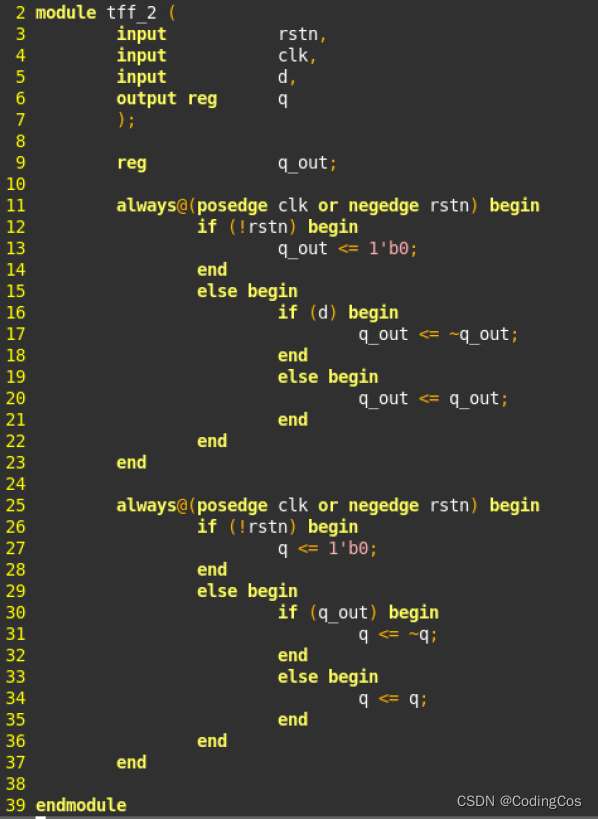

T 触发器的概念:来 1 翻转,来 0 保持。

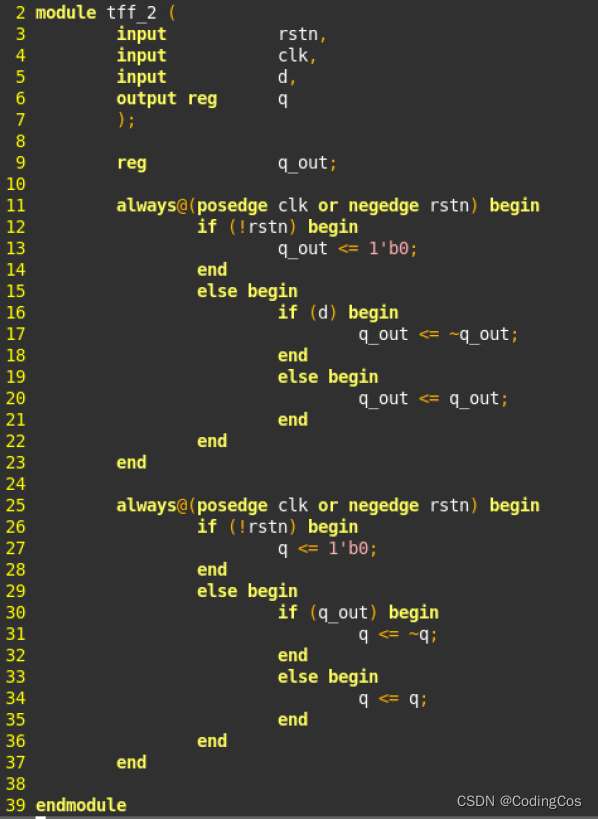

verilog 代码

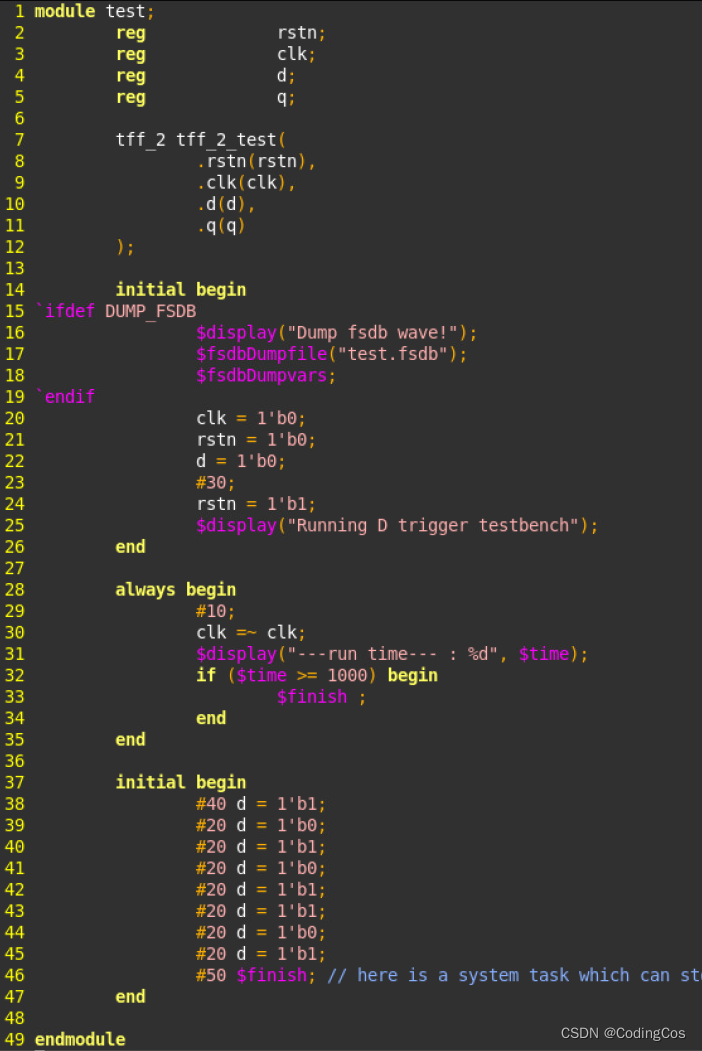

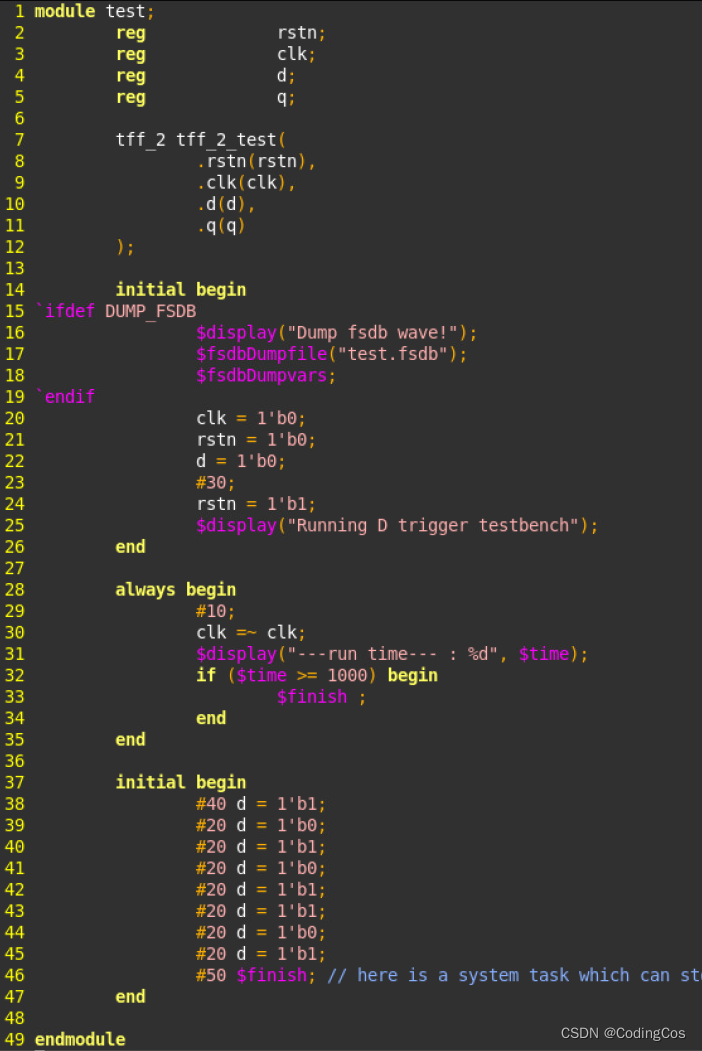

TestBench 代码

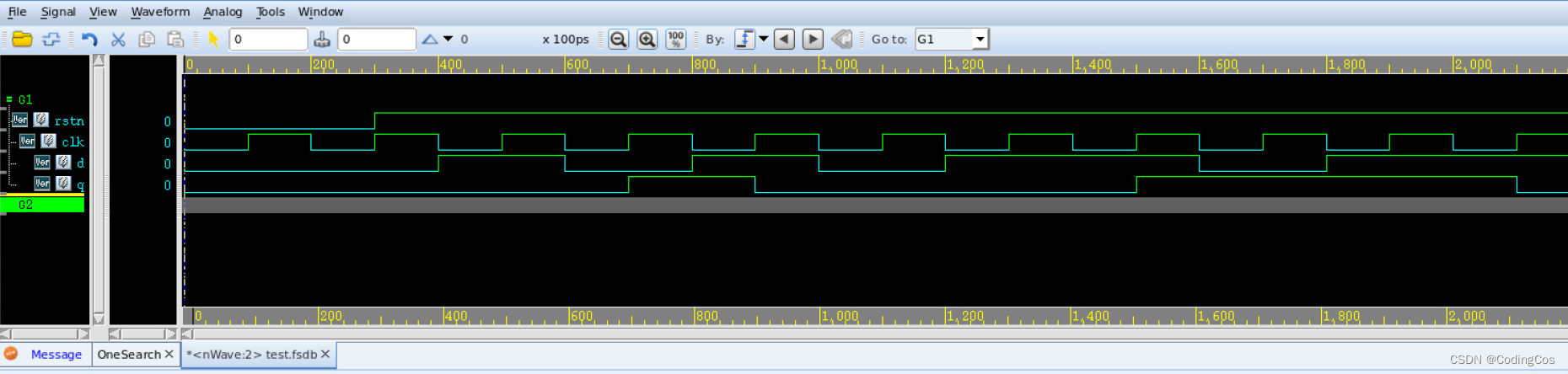

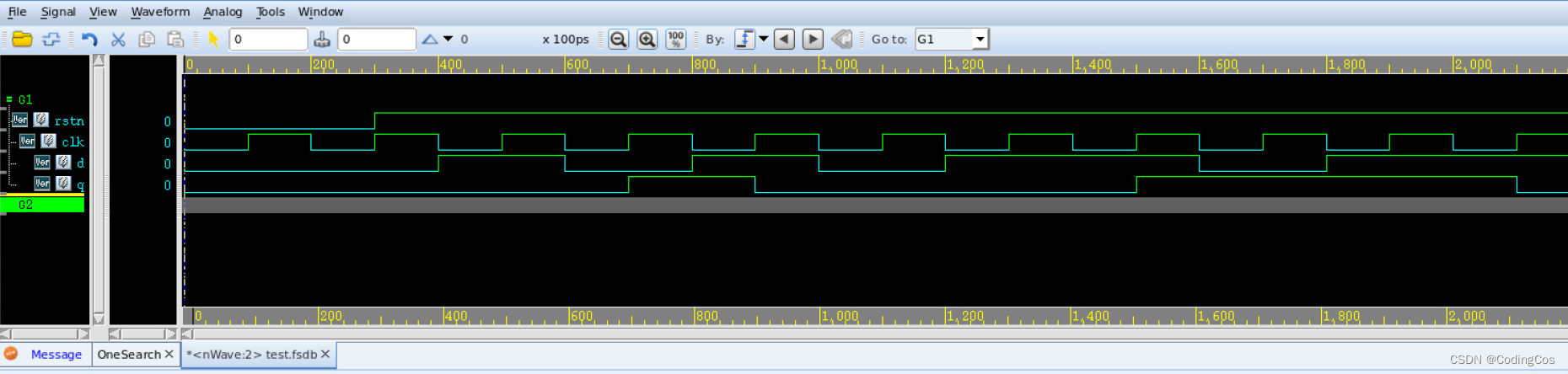

VCS 波形仿真

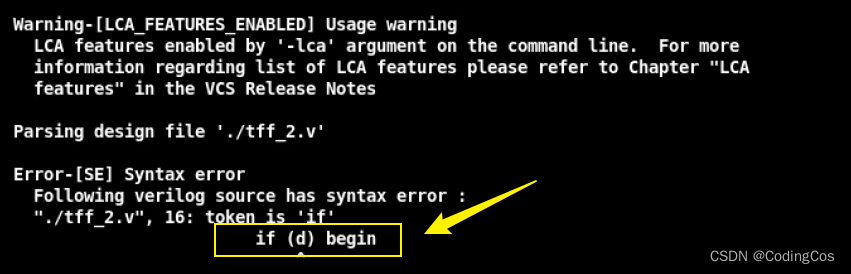

问题小结

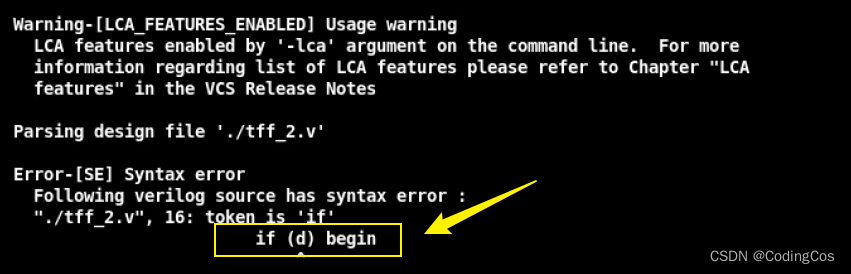

问题导致的原因是 if (d) begin 语句之后没有 end 结束符,直接 else begin,所以在每个 if (expression) begin 之后都不能少掉 end。

推荐阅读:

https://www.nowcoder.com/exam/oj?page=1&tab=Verilog%E7%AF%87&topicId=301

原文地址:https://blog.csdn.net/sinat_32960911/article/details/136053327

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。

本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。

如若转载,请注明出处:https://www.suanlizi.com/kf/1754862006520909824.html

如若内容造成侵权/违法违规/事实不符,请联系《酸梨子》网邮箱:1419361763@qq.com进行投诉反馈,一经查实,立即删除!