架构

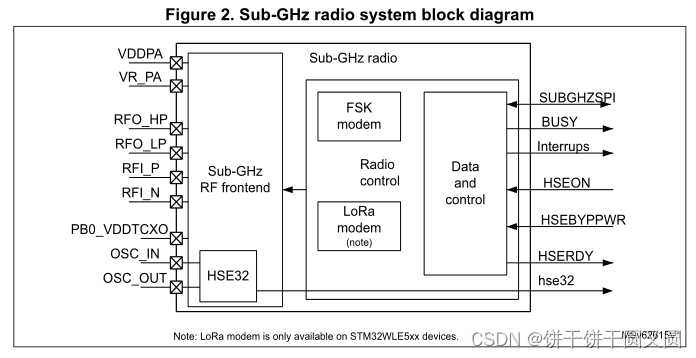

该器件嵌入了一个sub-GHz RF子系统,该子系统使用ARM Cortex-M4(称为CPU)与通用微控制器子系统接口。

需要一个RF低层堆栈,它与主机应用程序代码一起在CPU上运行。

射频子系统的通信是通过内部SPI接口完成的。

ARM Cortex-M 内核

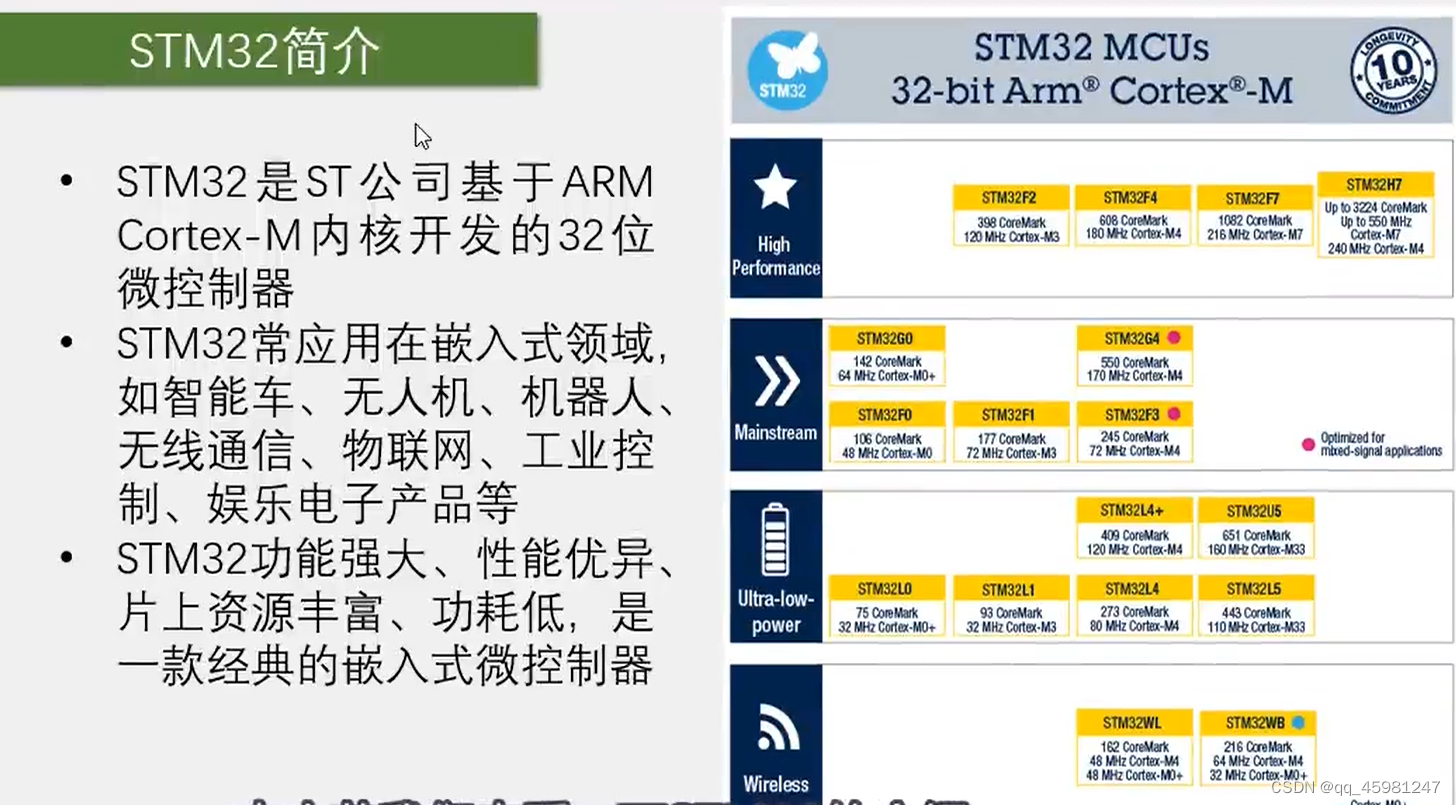

凭借其嵌入式Arm内核,STM32WLE5/E4xx器件与所有Arm工具和软件兼容。

ARM Cortex-M4是一款嵌入式系统处理器。它的开发是为了提高一个满足MCU实现需求的低成本平台,具有减少的引脚数和低功耗,同时提供出色的计算性能和先进的中断响应。

ARM Cortex-M4 32位RISC处理器具有卓越的代码效率,在通常与8位和16位设备相关的内存大小下提高ARM核心所期望的高性能。

该处理器支持一组DSP指令,允许高效的信号处理和复杂的算法执行。

自适应实时内存加速器(ART Accelerator)

ART加速器是针对STM32工业标准ARM Cortex-M4处理器进行优化的内存加速器。ART加速器平衡了ARM Cortex-M4相对于闪存技术的固有性能优势,后者通常需要处理器等待更高频率的闪存。

为了使处理器在48MHz时的性能接近60DMIPS,ART加速器实现了指令预取队列和分支缓存,从而提高了64位闪存的程序执行速度。

基于CoreMark基准测试,ART加速器实现的性能相当于在高达48MHz的CPU频率下从闪存执行0等待状态程序。

内存保护单元(MPU)

内存保护单元MPU用于管理CPU对内存的访问,防止某个任务意外损坏其它活动任务使用的内存或资源。

这个存储区域被组织成多达8个保护区,这些保护区又被分成8个子区域。

保护区域的大小介于32字节和整个4GB的可寻址内存之间。

对于必须保护某些关键代码或认证代码以防止其它任务的不当行为的应用程序,MPU特别有用。

它通常由RTOS(实时操作系统)管理。如果一个程序访问了MPU禁止的内存位置,RTOS可以检测到它并采取行动。

在RTOS环境中,内核可以根据要执行的进程动态更新MPU区域设置。

MPU是可选的,可以绕过不需要它的应用程序。

嵌入式闪存

闪存接口管理从CPU AHB ICode/DCode到闪存的访问。实现了对闪存的访问、擦除和编程操作以及读写保护。

- 内存组织方式:BANK

- 主存:最大256KB

- 页大小:2KB

- 72位宽数据读取(64位+8位ECC)

- 72位宽数据写入(64位+8位ECC)

- 页擦除和整块擦除

由于选项字节,可以配置灵活的保护:

读出保护(RDP)保护整个内存:有三个级别:

- 0级:无读出保护

- 1级:存储器读出保护。如果连接了调试功能,选择从SRAM启动或选择引导加载程序启动,则无法从内存读取或向其写入。

- 2级:芯片读出保护。调试功能(JTAG和串行线),在SRAM中启动和引导加载程序选择被禁用(JTAG保险丝)。这种选择是不可逆的。

WRP:保护区域不被擦除和编程。可以选择两个区域,粒度4KByte。

专有代码读出保护(PCROP):闪存的两个部分可以防止第三方读取和写入。该保护区域是仅执行的:它只能被STM32 CPU作为指令码访问,而其他访问(DMA、调试和CPU数据读、写、擦除)都是严格禁止的。

可以选择两个区域,粒度为2KByte。

另外一个选项位(PCROP_RDP)用于选择当RDP保护从1级更改为0级时是否擦除PCROP区域。

整个非易失性存储器嵌入纠错码(ECC)功能,支持:

- 单个错误检测和纠正

- 双重错误检测

- 可以在FLASH_ECCR寄存器中读取ECC故障的地址

嵌入的SRAM

该器件具有高达64KB的嵌入式SRAM,分为两个块:

- SRAM1:最大32KB,映射到地址0x2000 0000

- SRAM2:位于地址0x2000 8000的32KB(在SRAM1 32KByte配置的情况下与SRAM1相邻),也镜像在0x1000 0000,具有硬件奇偶校验(此SRAM可以保留在待机模式)

在所有CPU时钟速度下,SRAM都可以在0等待状态下以读/写方式访问。

安全管理

设备包含许多安全块,例如:

- RNG

- 128位和256位AES,支持ECB、CBC、CTR、GCM、GMAC和CCM链模式

- PKA:模运算包括取幂,最大模大小为3136

- 素数场上的椭圆曲线标量乘法,ECDSA签名,最大模大小为521位的ECDSA验证

- 循环冗余校验计算单元

启动模式

在启动时,BOOT0引脚和BOOT1选项位用于选择以下启动选项之一:

- 从用户闪存启动

- 从启动系统内存启动(嵌入式引导加载程序所在的位置)

- 从嵌入式SRAM启动

引导加载程序使从USART或SPI下载程序成为可能。

如果启动选择使用BOOT0引脚从主闪存启动,但是发现第一个闪存为空,则Flash空检查机制强制从系统内存(包含嵌入式引导加载程序)引导。

然后,由于引导加载程序激活,一些GPIO从高Z状态重新配置。

可以通过配置选项字节来禁用此功能,以强制从闪存启动(nSWBOOT0=0,nBOOT0=1)