验证I/O和时钟规划

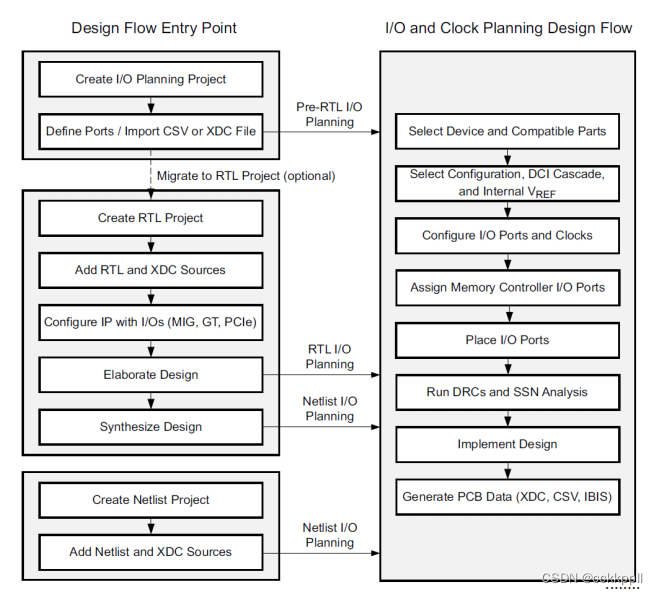

执行I/O和时钟规划后,验证您的设计以确保其符合设计要求。AMD Vivado™ 工具允许您运行DRC来检查违规行为,以及执行SSN分析以估计切换噪声水平。对I/O执行最终验证和时钟分配,您必须实现设计并生成比特流。

运行DRC

运行DRC是引脚规划中最关键的步骤之一。DRC检查当前设计根据一组指定的设计规则检查(称为规则组),并报告任何错误或违规行为。本节介绍运行I/O端口和时钟相关的DRC所需的步骤以及查看DRC违规行为。

注意:有关高级DRC控制,请参阅Vivado Design中的创建自定义设计规则检查一节Suite用户指南:使用Tcl脚本(UG894)。关于report_ drc和相关Tcl命令的信息,请参阅《Vivado Design Suite Tcl命令参考指南》(UG835)。

运行I/O端口和时钟逻辑相关的DRCs

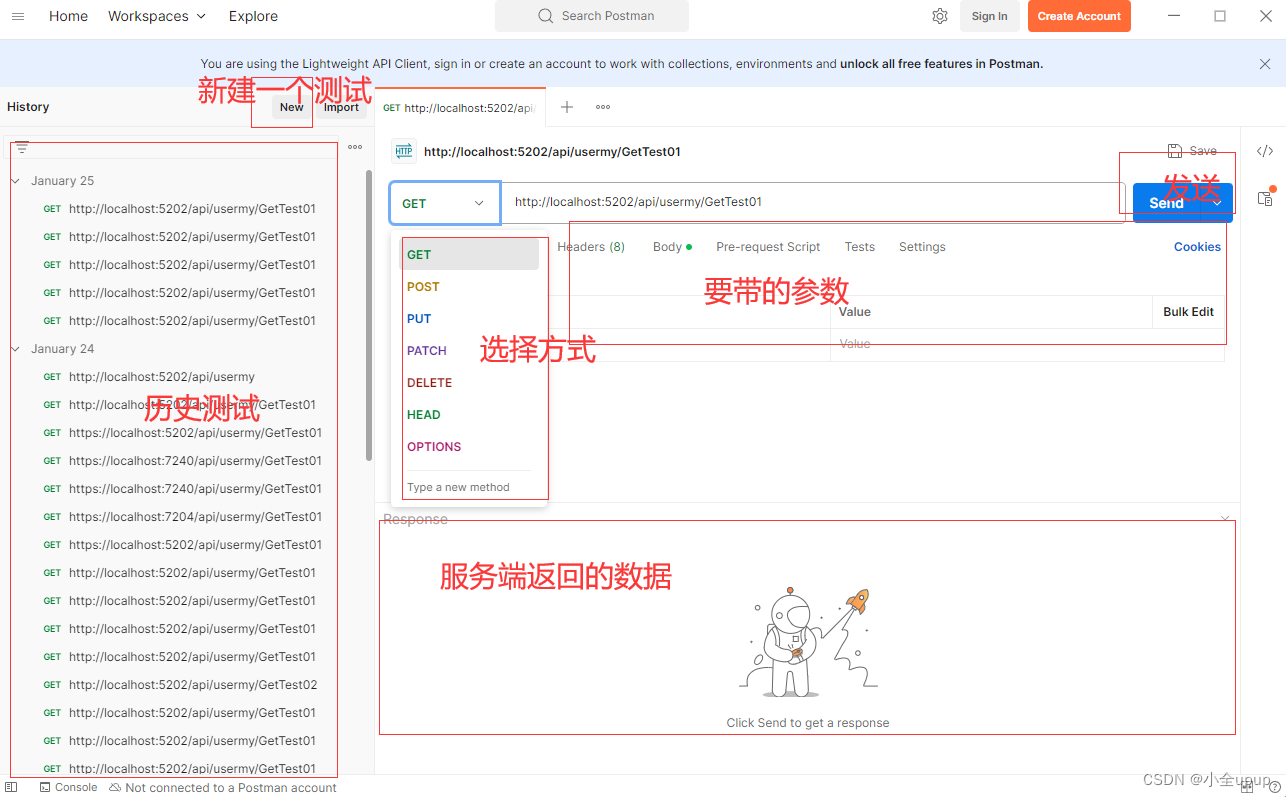

要选择并运行单个规则,请执行以下操作:

1.选择报告 → 报告DRC。

注意:或者,您可以从Flow Navigator中单击Report DRC,或者输入以下内容

Tcl控制台中的命令:report_drc-name<results_name>。

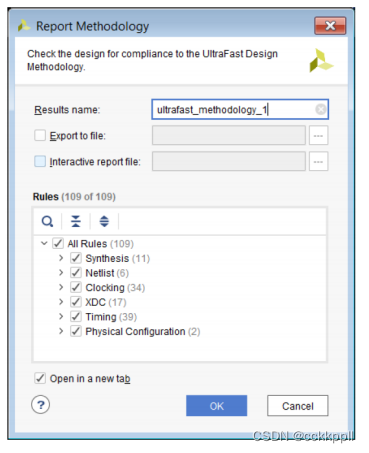

2.在“报告DRC”对话框(见下图)中,设置以下选项,然后单击好啊

•结果名称:指定DRC结果的名称,显示在DRC的选项卡中窗输入唯一的名称可以更容易地识别特定运行的结果在DRC窗口中调试期间。默认情况下,输出文件名与您进来

•输出文件:输入文件名以将DRC结果保存到文件中(可选)。选择路径除默认设置外,请使用浏览按钮。

•规则组:指定要在设计中运行的规则组。规则牌是设计的集合为方便起见,将规则检查分组。设计规则检查可以存在于多个规则中甲板例如,opt_checks和placer_checks规则中都可以存在相同的规则甲板。Vivado工具在FPGA设计的适当阶段运行规则组流,例如在合成或实现之后。

•默认:运行AMD建议的一组默认检查

•opt_checks:运行与逻辑优化相关的检查。

•placer_checks:运行与放置相关的检查。

•router_checks:运行与路由相关的检查。

•bitstream_checks:运行与位流生成相关的检查。

•timing_checks:运行与时间约束相关联的检查。

•incr_eco-checks:检查增量eco设计修改的有效性。

•eco_checks:完成后对连接和位置进行检查

修改网表的工程变更单(ECO)。例如,此检查是通常在connect_net Tcl命令用于修改网表。

•规则:指定规则组后,根据需要修改规则以运行。

提示:如果要运行一组非标准的设计规则检查,可以使用创建自定义规则组create_drc_ruledeck和add_drc_checks Tcl命令,如Tcl命令中所示定义自定义规则组的示例。创建自定义规则组后,它将显示在规则中“报告DRC”对话框的Decks区域。

注意:有关create_drc_ruledeck和相关Tcl命令的更多信息,请参阅Vivado

《设计套件Tcl命令参考指南》(UG835)。

启用或禁用交互式DRCs

在I/O规划期间,Vivado IDE运行基本检查,以确保合法的引脚输出。然而完整的签核DRC仅在Vivado实施期间运行。因此,您需要运行您的设计通过Vivado实现,以确保最终合法引脚。交互式I/O放置例程检查引脚放置过程中的常见错误情况。你可以使用“常规”选项卡中的“自动检查I/O位置”复选框打开和关闭此功能的程序包窗口设置。启用自动检查时,该工具不允许在引脚上放置I/O端口导致设计问题。在位I/O端口顺序模式,如果尝试放置I/O端口在有问题的引脚上,会出现一个工具提示,说明无法放置I/O端口的原因。默认情况下启用交互式DRC。

重要!这些DRC中的许多仅在合成或实现的设计上运行。

交互式I/O放置规则包括:

•禁止:

•放置在与GTs相关的噪声敏感引脚上或I/O封装引脚上潜在噪声敏感

•违反I/O标准

•确保:

•不支持I/O标准的银行不使用I/O标准

•银行没有分配不兼容的VCC端口

•需要VREF端口的银行有免费的VREF引脚

•正确分配全球时钟和区域时钟(仅使用导入的网表XDC文件)

•差分I/O端口设置为正确的感测引脚

•没有输出引脚放置在仅输入引脚上

建议:AMD建议您在启用DRC的情况下开始放置I/O端口。看见有关I/O端口和时钟区域规范的更多信息,请参阅设备文档。

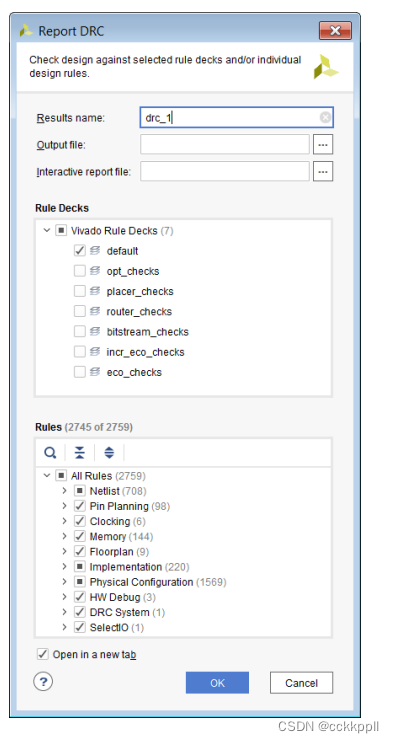

查看DRC违规

如果发现违规行为,将打开DRC窗口,如下图所示窗口显示规则冲突,分组在中定义的各种规则类别下“报告DRC”对话框。违反规则的行为也按严重程度进行分类,并用颜色编码以便快速审查如下:

•咨询:提供设计处理的一般状态和反馈。

•警告:表示由于约束或规范可能无法按预期应用。

•严重警告:表示未应用或未应用某些用户输入或约束坚持最佳实践。AMD强烈建议您检查这些问题并变化。

注意:在生成比特流期间,严重警告会升级为错误。

•错误:表示导致设计结果不可用的问题,如果没有该问题,则无法解决你的干预。设计流程停止。

提示:您可以切换“隐藏警告”和“信息消息”工具栏按钮以关闭警告和信息性消息,只查看报告的错误。

排序DRC违规

要按严重性对DRC违规进行排序,请单击严重性列标题,如下所示:

•单击列标题以递增顺序进行排序。

•再次单击列标题以按降序排序。

注:有关更多信息,请参阅Vivado Design Suite用户指南:使用Vivado IDE(UG893)VivadoDesign Suite用户指南:使用Vivado IDE(UG893)。

查看DRC冲突属性

在DRC窗口中,右键单击违规消息,然后选择违规属性。在“违规属性”窗口,单击以下视图:

•概述:提供有关DRC规则违反的高级信息,包括类型、严重性、,和描述。

•详细信息:提供有关违反规则的设计元素的信息。此外,这视图可能包括指向违反DRC的特定设计对象的链接。单击这些链接在RTL网表窗口、设备窗口、原理图窗口中查看设计对象,或者源RTL文件。

创建自定义DRC

您还可以使用Tcl命令,如create_drc_check和create_drc_violation,创建用于Vivado Design Suite的自定义DRCs。有关更多信息,请参阅一节在Vivado Design Suite用户指南中创建自定义设计规则检查链接:使用Tcl脚本(UG894)。有关create_drc_check和相关Tcl命令的更多信息,请参见Vivado Design Suite Tcl命令参考指南(UG835)。

查询DRC

要获取当前定义的drc的列表,请使用get_drc_checks-Tcl命令。了解更多有关信息,请参阅《Vivado Design Suite Tcl命令参考》中的get_drc_checks一节指南(UG835),请参阅Vivado Design Suite用户指南:使用Tcl脚本(UG894)。报告方法在2016.1中,一些检查从report_drc移到了新的report_methodology命令这些检查包括验证设计的约束和其他规则,如逻辑映射。

检查符合超快™ 设计方法并运行简化规则选中,如“报告方法”对话框中所示。

第一次合成设计时以及在中发生更改后运行report_methodology约束、时钟拓扑或大型逻辑更改,以识别常见的设计问题。对于有关运行方法检查的更多信息,请参阅运行方法一节检查《Vivado Design Suite用户指南:系统级设计条目》(UG895)。

![[R] Merging and adding info from paper based survey](https://img-blog.csdnimg.cn/direct/d8e6548e7bd2423da4e4e3b92cd1e760.png)