一、前言

MMCM和PLL是在FPGA设计中不可避免需要使用到的时钟资源,对于其功能及使用方法的理解是正确进行FPGA设计的前提。

二、Xilinx 时钟 IP配置

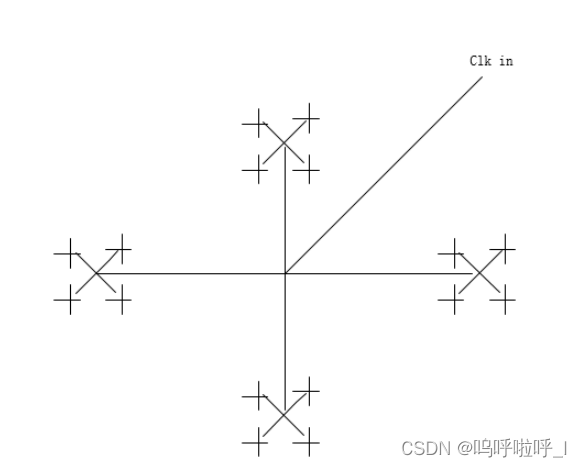

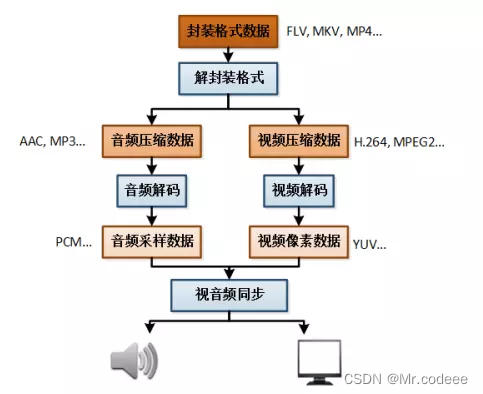

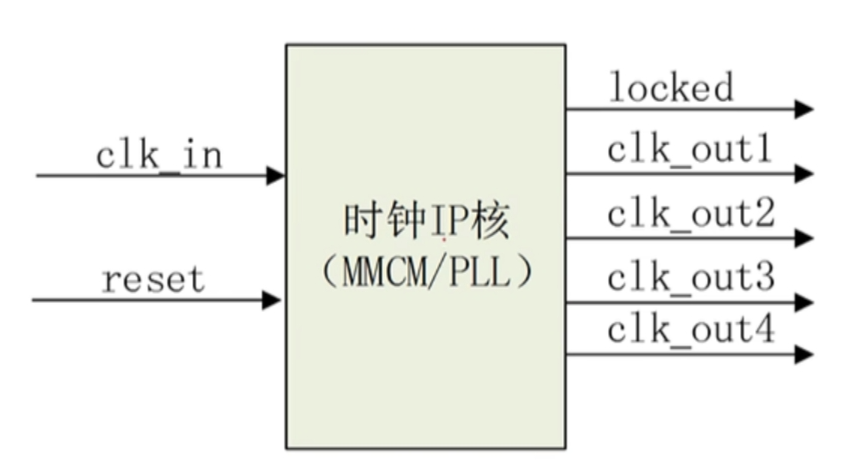

vivado中使用时钟向导(Clocking Wizard)配置时钟IP核,其框图如下:

clk_in 输入时钟,一般为班上晶振引入时钟或者serdes恢复时钟以及其他专用时钟引脚输入时钟;

复位信号RST需要连接到用户逻辑——如果在没有时钟的情况下RST直接接地会导致clk_wiz无法工作;

locked信号,从 0 变为1 ,表示输出的时钟达到稳定。

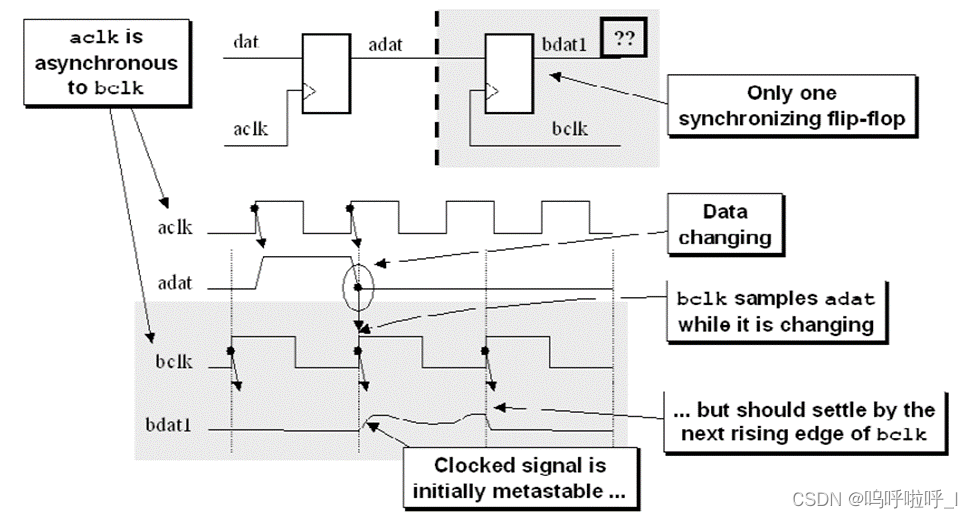

三、locked信号

MMCM或PLL的输出LOCKED信号一般用来作为复位完成的状态标志位。原因如下:与PLL输出时钟驱动的逻辑单元需要保持复位状态,直到PLL的LOCKED信号输出拉高为时,此刻表明时钟被锁定,PLL处于稳定的状态,因此LOCKED在设计常会用作复位信号。

四、约束

时钟IP会自动在综合实现中生成相应的时钟约束,因此不需要在约束文件中在对相关时钟进行时钟约束。