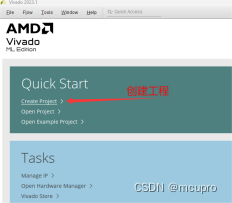

打开VIVADO2023.1

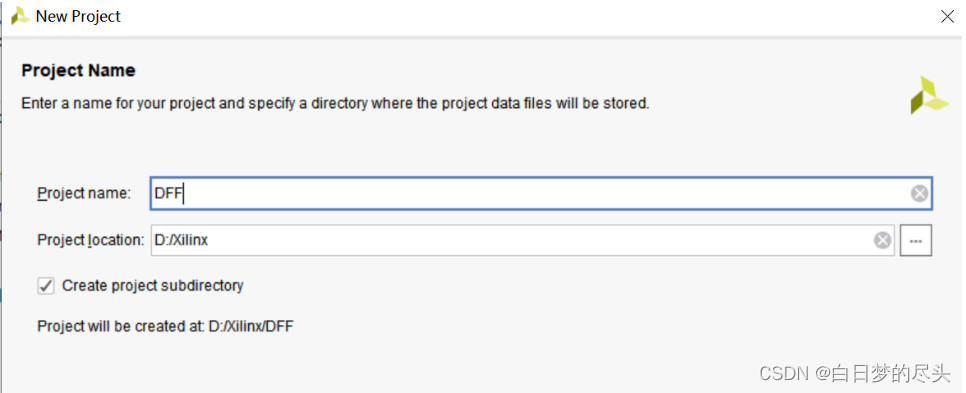

创建一个新的工程,设置工程名称和地址

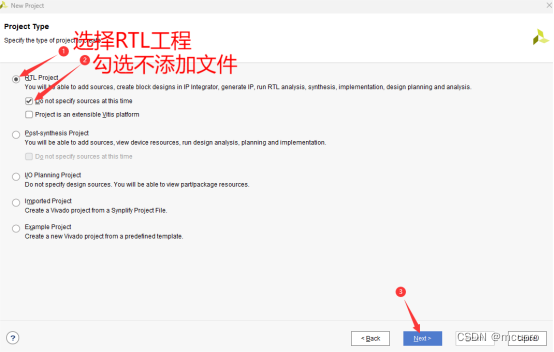

选择RTL工程,勾选不添加文件

搜索15eg,选择xqzu15eg-ffrb1156-2-i

完成创建工程

添加设计模块

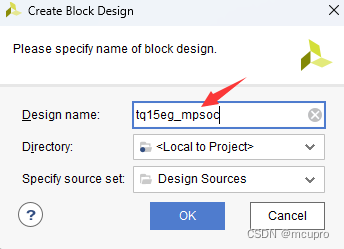

设置模块名称

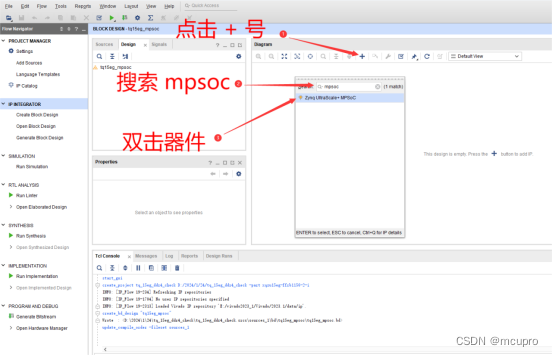

在模块中添加mpsoc器件

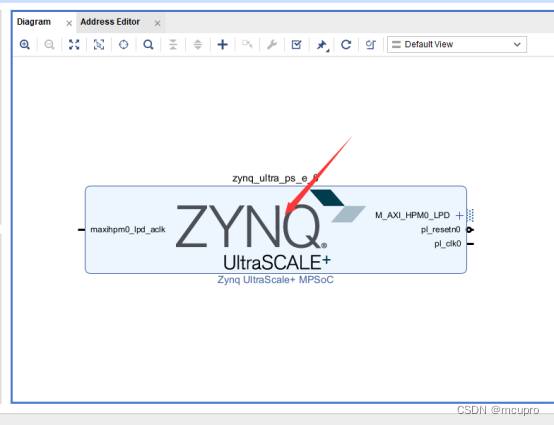

双击器件进行配置

若有配置文件预设可以直接导入配置

选择 .tcl 预设文件导入即可

具体配置内容如下

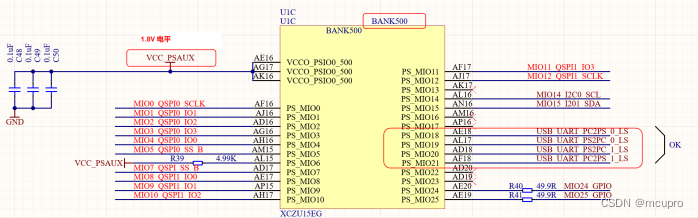

串口配置,设置MIO电压为1.8V,打开两个串口

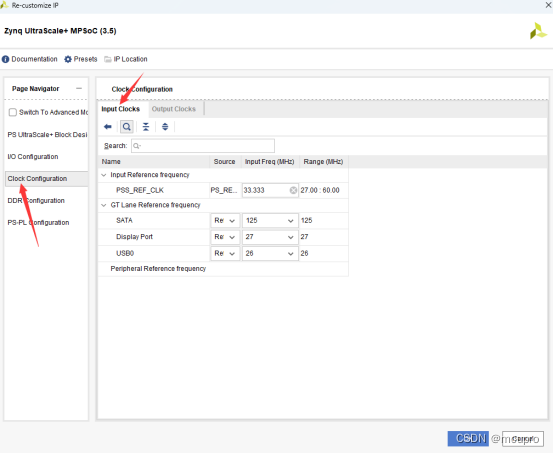

输入时钟配置

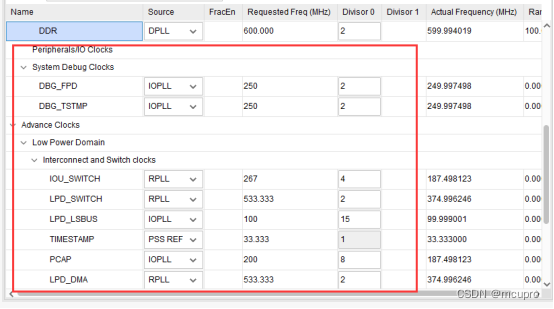

输出时钟配置

DDR配置

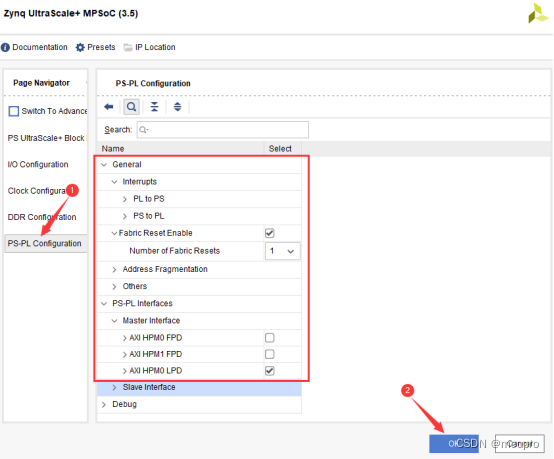

Ps-Pl 设置,设置完成后点击确认

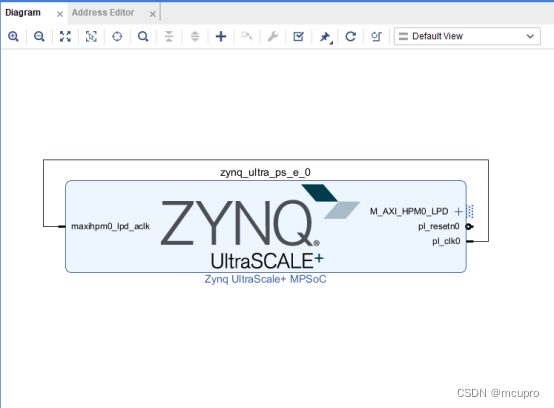

把mpsoc模块的时钟线连接起来

右键设计模块,点击Generate Output ...

默认设置点击生成

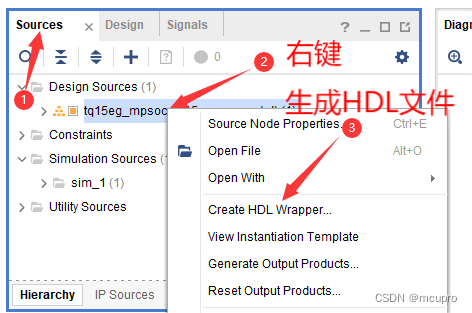

右键设计模块生成HDL文件

第一个选项是生成可编辑的HDL文件,第二个选项则不可编辑,这里默认即可

点击Generate Bitstream 生成bit流文件

默认设置点击OK

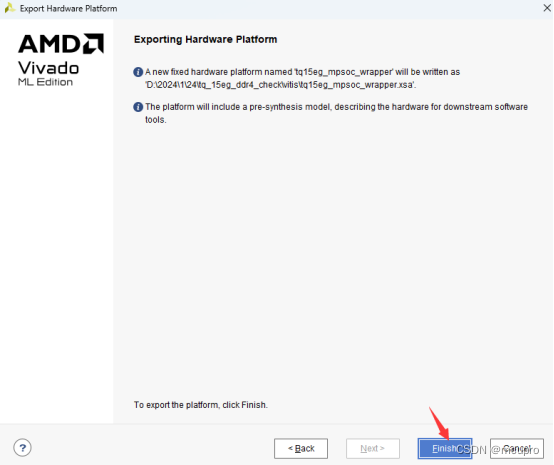

在生成bit流的时候可以打开vitis,首先需要在vivado中导出硬件平台

设置名称与选择保存地址

完成导出硬件平台

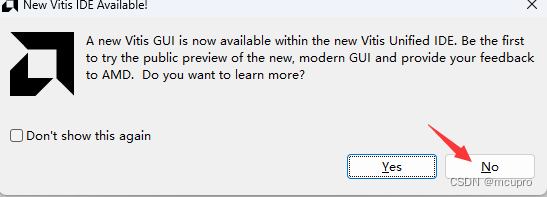

打开vitis

选择vitis项目保存的地址

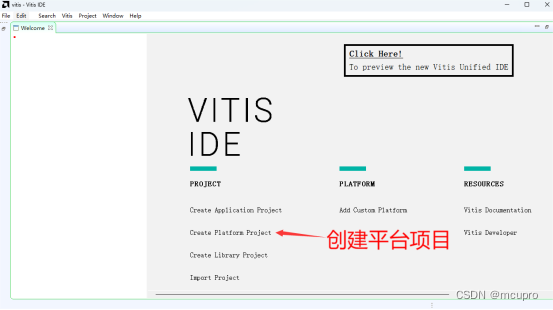

打开vitis后创建平台项目

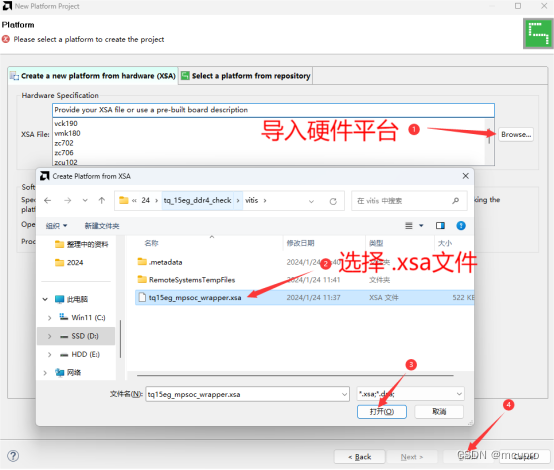

设置项目名称

导入在vivado中创建的硬件平台

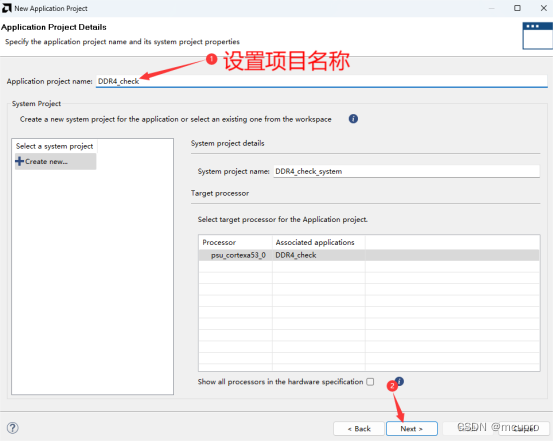

创建应用程序项目

设置项目名称

选择DDR测试项目

选择项目右键编译项目

插好板子上的电源,JTAG和UART线,把启动模式设置为JTAG模式0000,开启电源开关

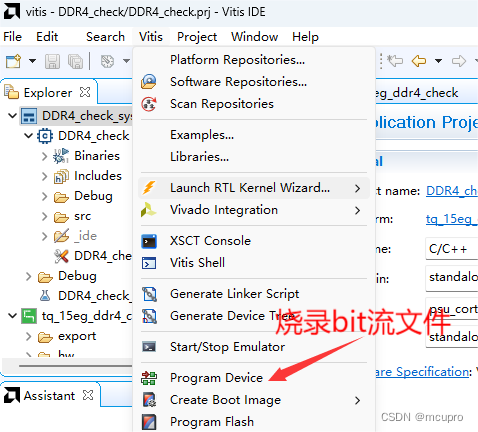

把bit流文件烧录进去

选择bit流文件的地址,一般在工程目录中的 ***.runs 文件夹,下的impl_1文件夹中

烧录成功,板子上的DL7,DL11和DL12都会亮起来

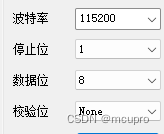

打开串口助手波特率设置为115200,停止位1,数据位8,无校验。

右键项目点击1 Launch Hardware把程序烧录进去

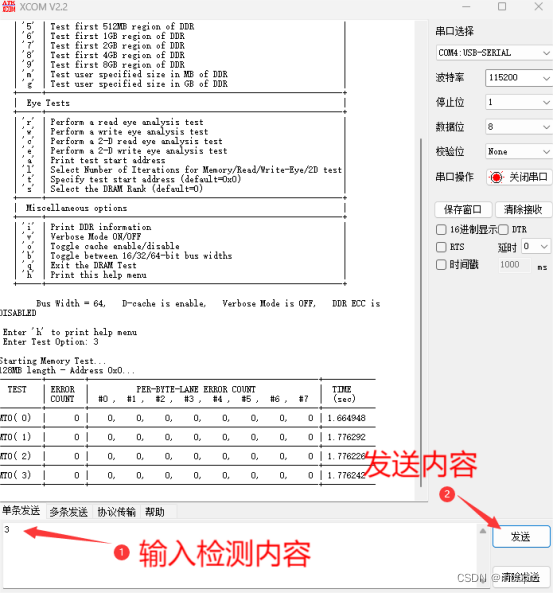

在串口助手中可以看到测试内容

发送内容选择检测项

![[N-135]基于springboot,vue高校图书馆管理系统](https://img-blog.csdnimg.cn/img_convert/dadae2e431b2a7cd0e9c052c40355787.png)