FPGA时序分析与时序约束(Vivado)

- 开发

- 35

-

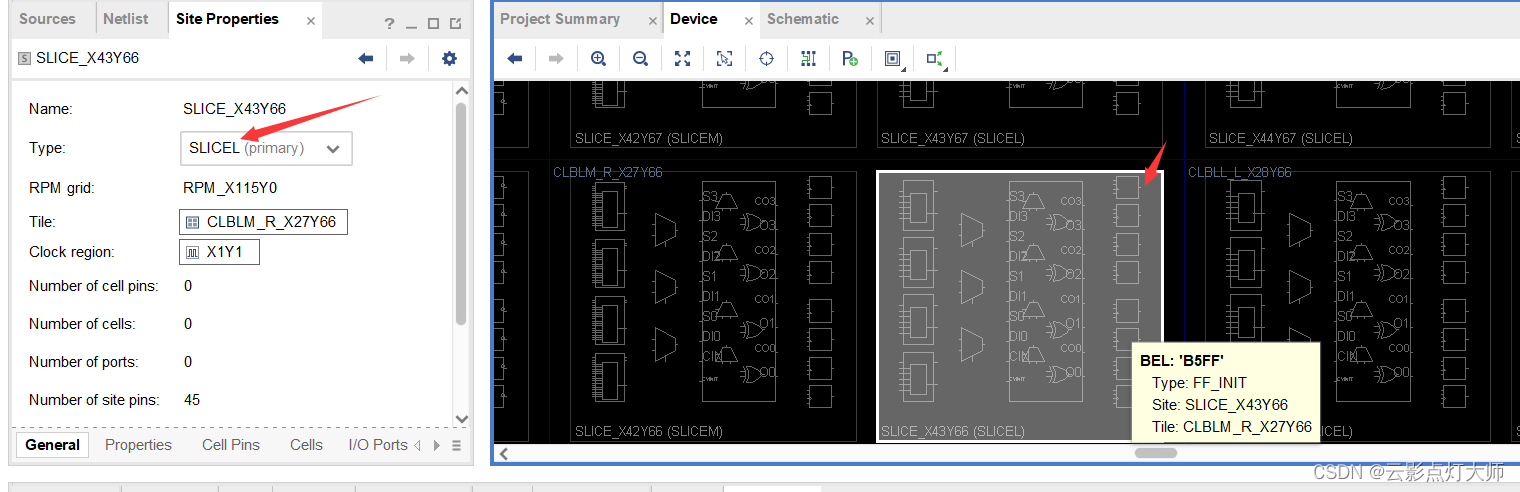

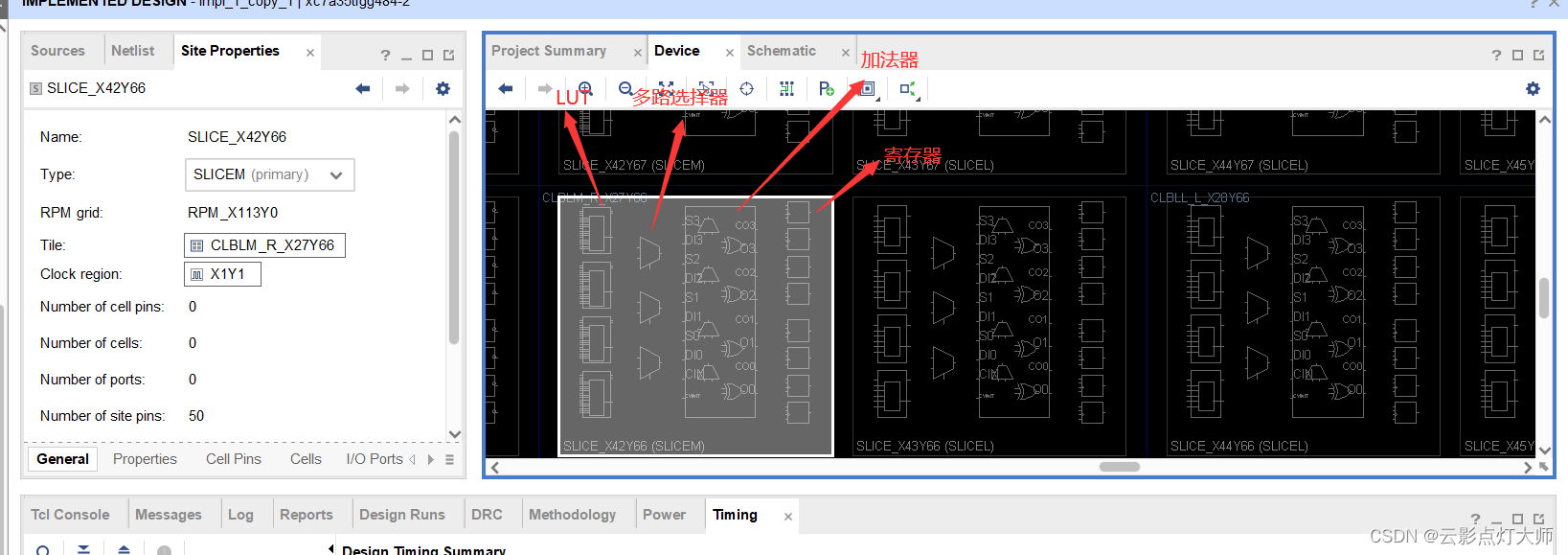

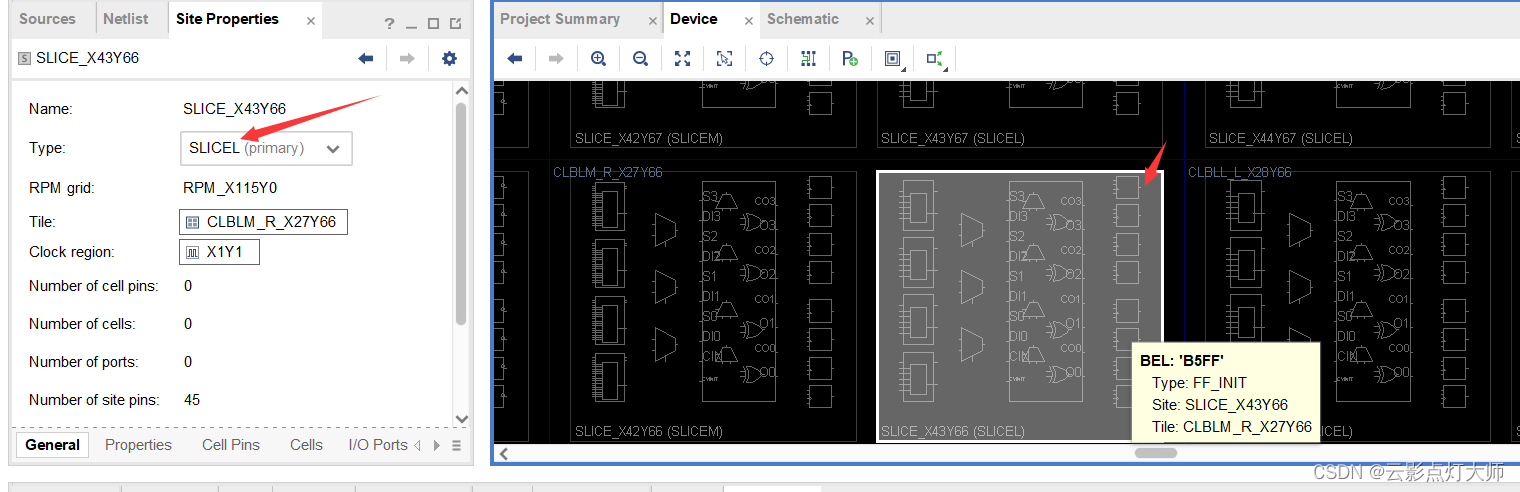

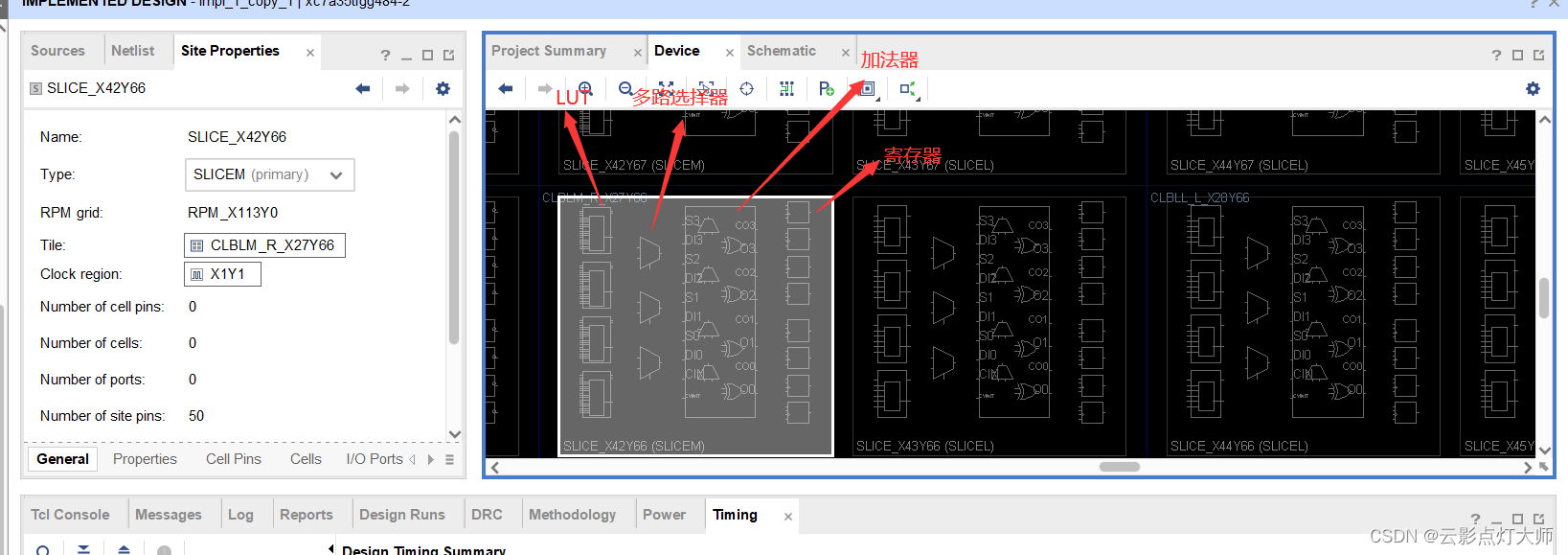

(1)内部资源

后缀L的这个单元中,会生成锁存器

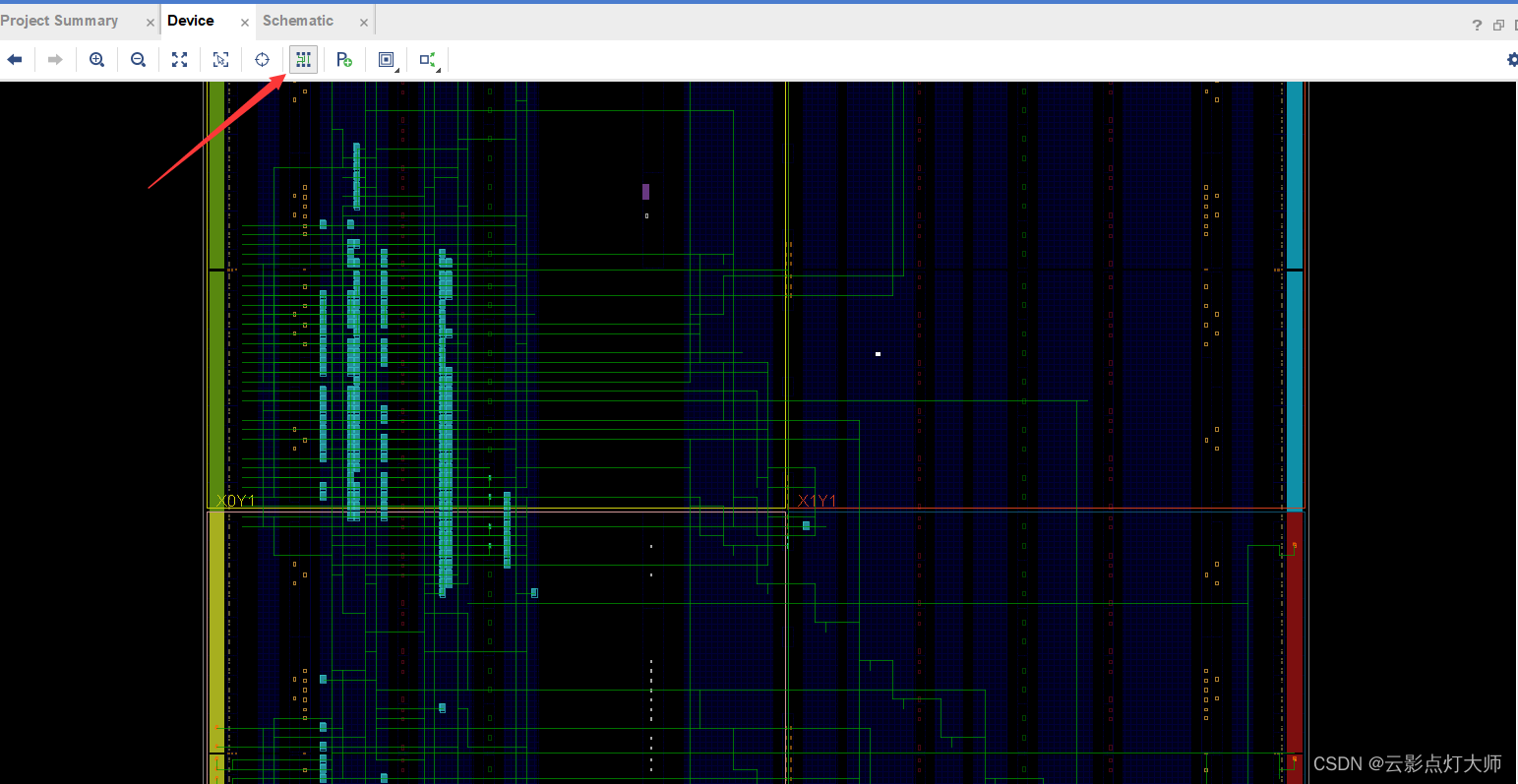

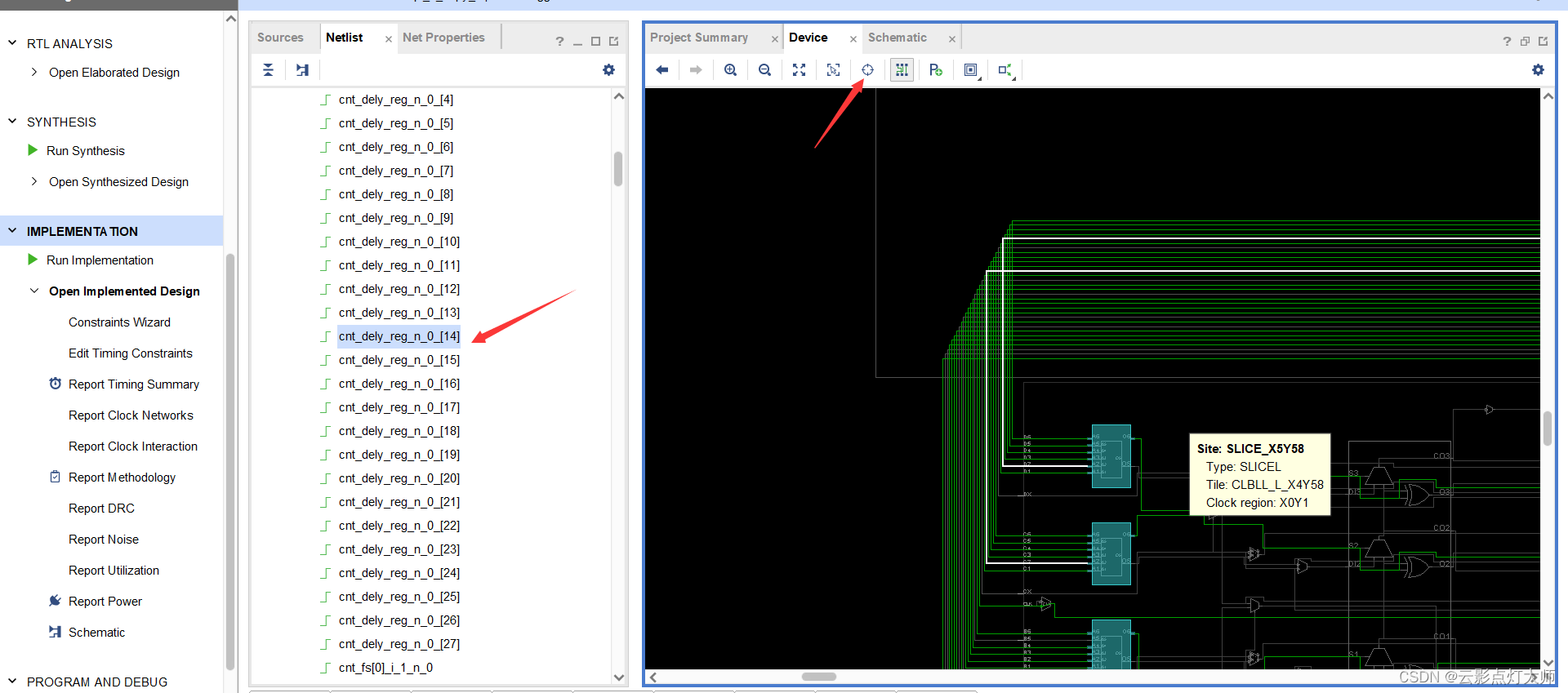

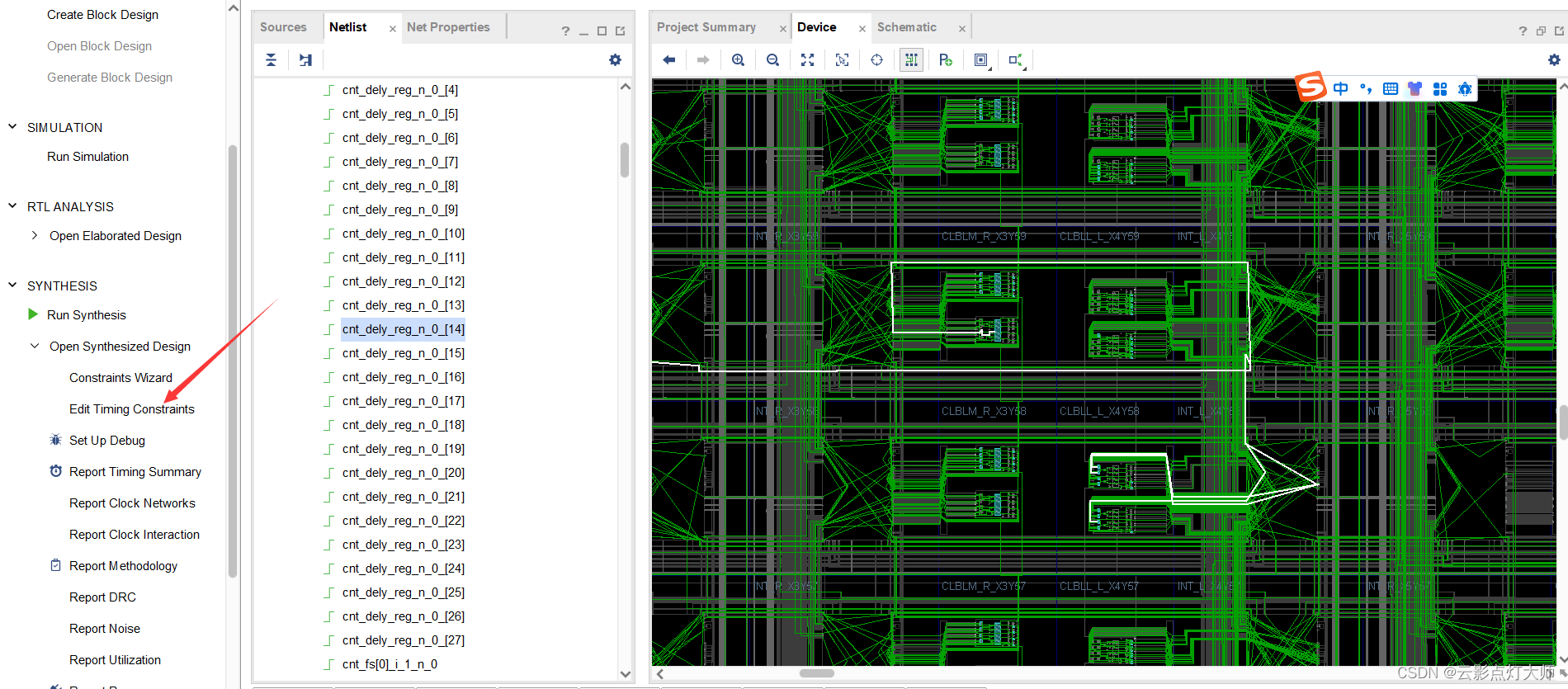

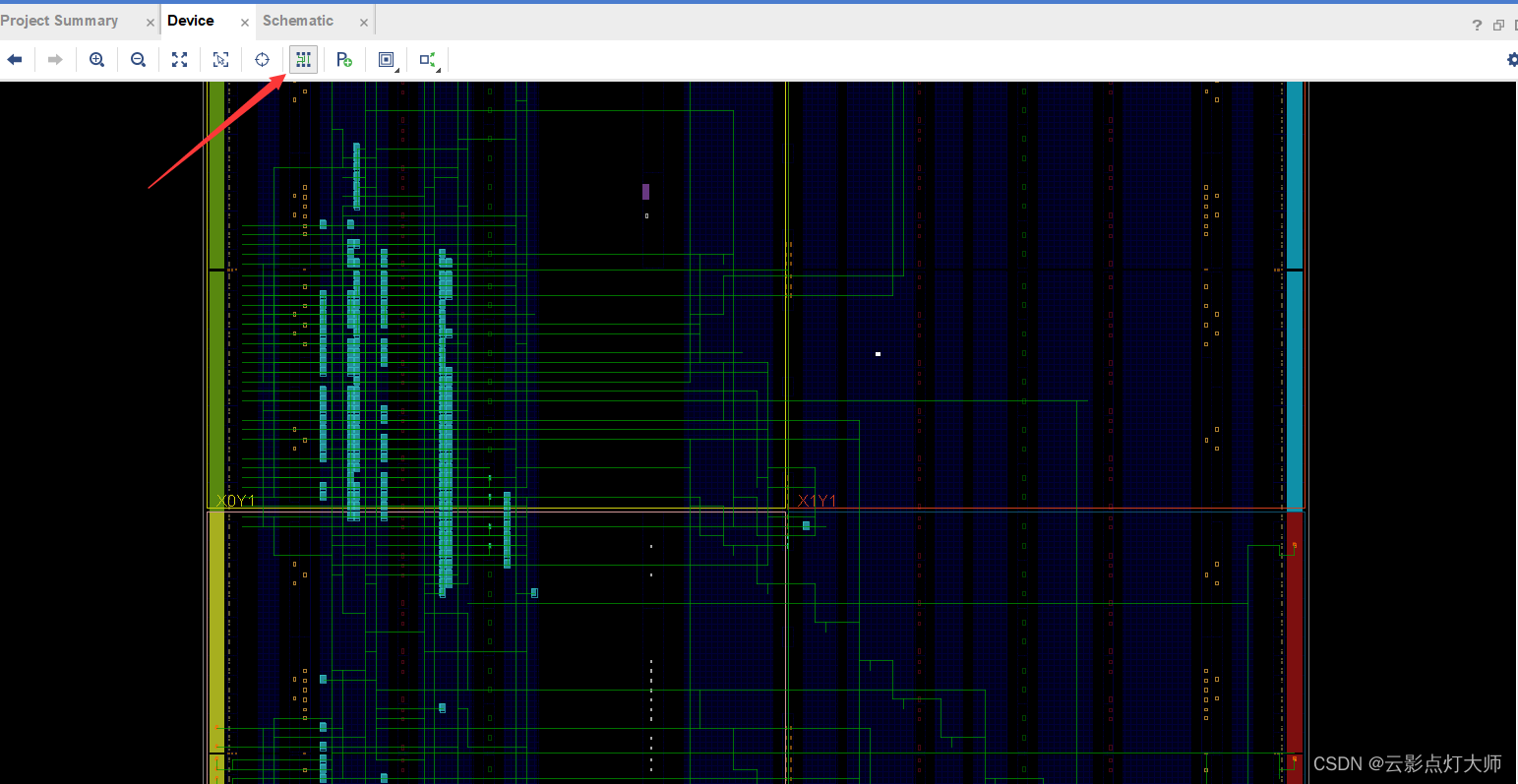

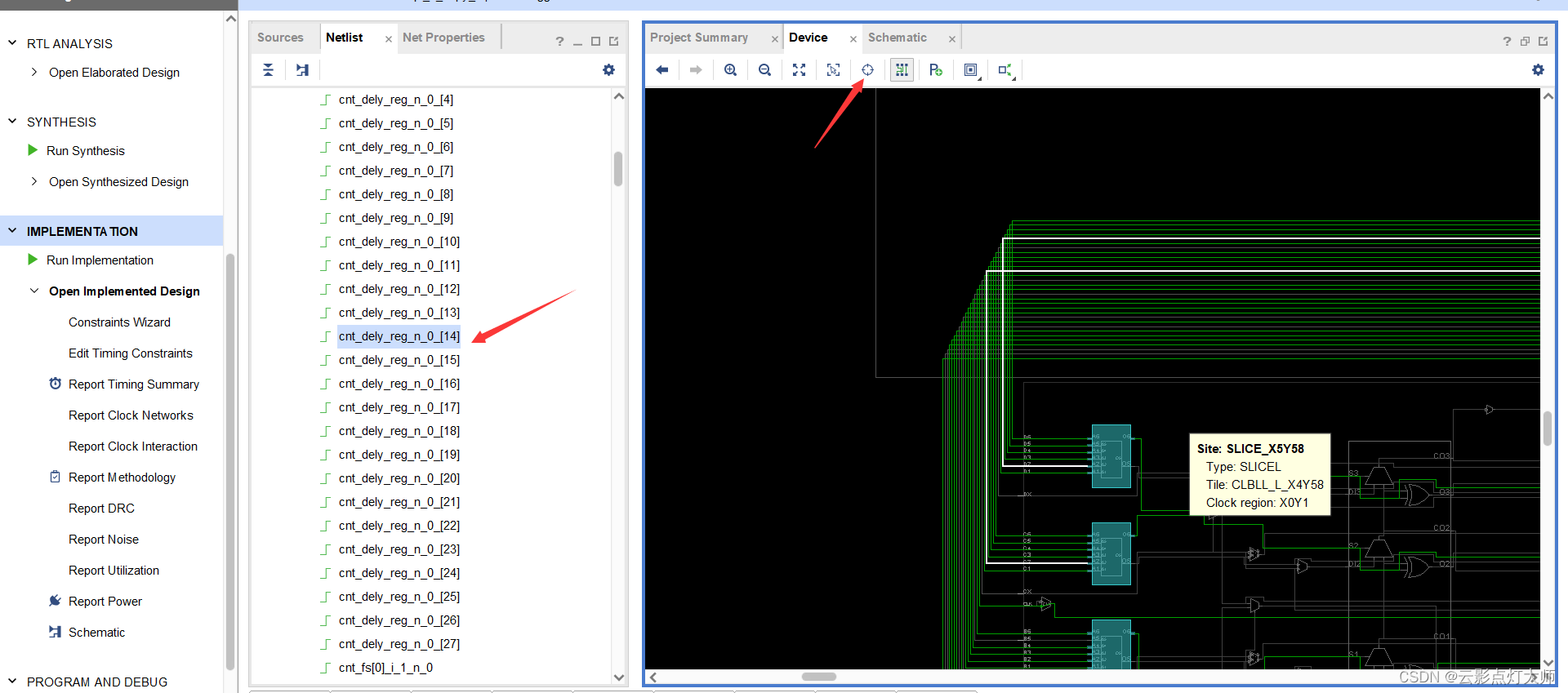

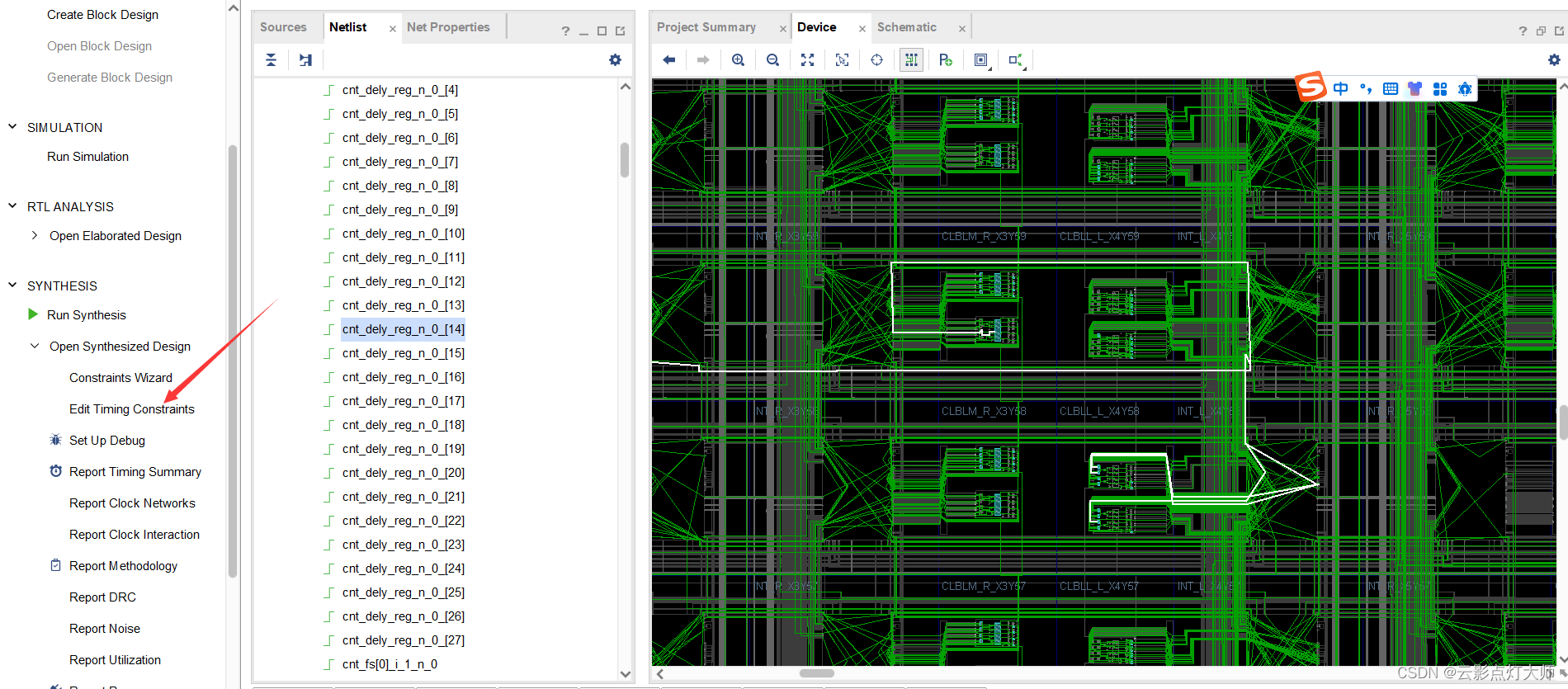

查看布线

定位线路

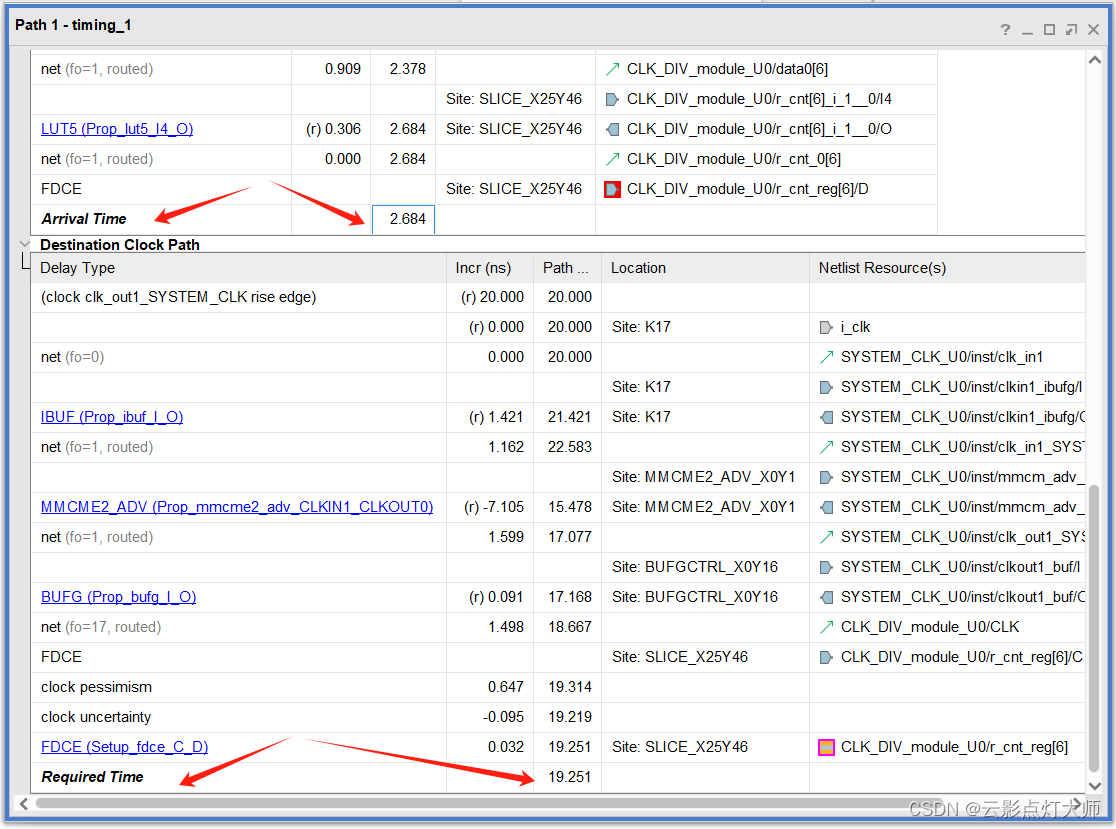

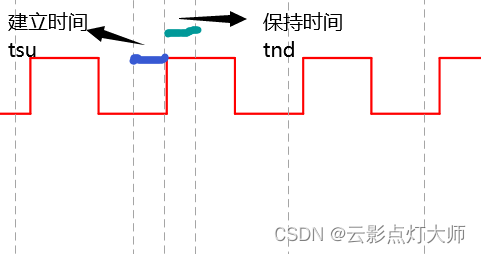

(2)传输模型分析(寄存器到寄存器)

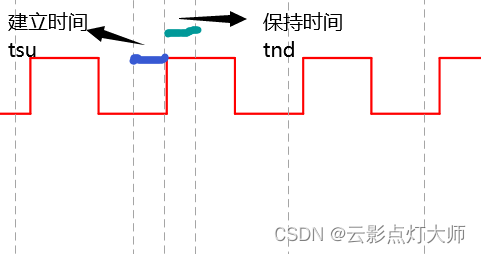

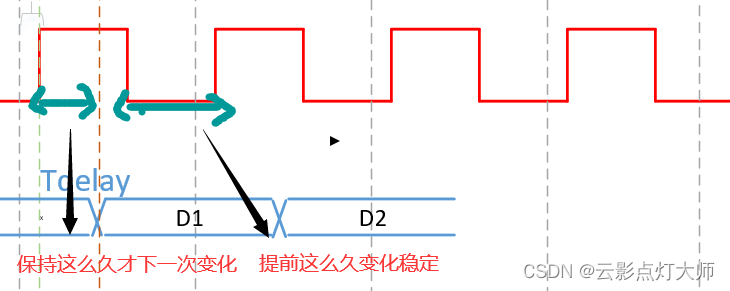

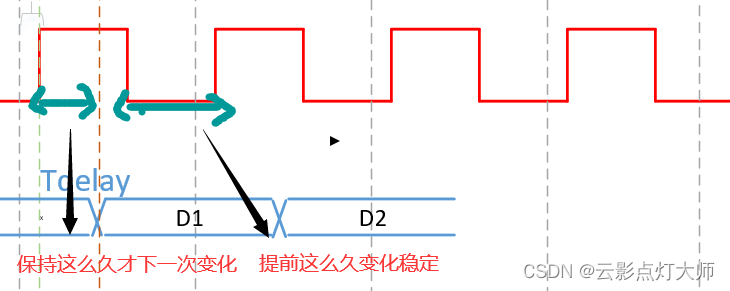

时间分析,还要考虑数据变化的建立时间与保持时间

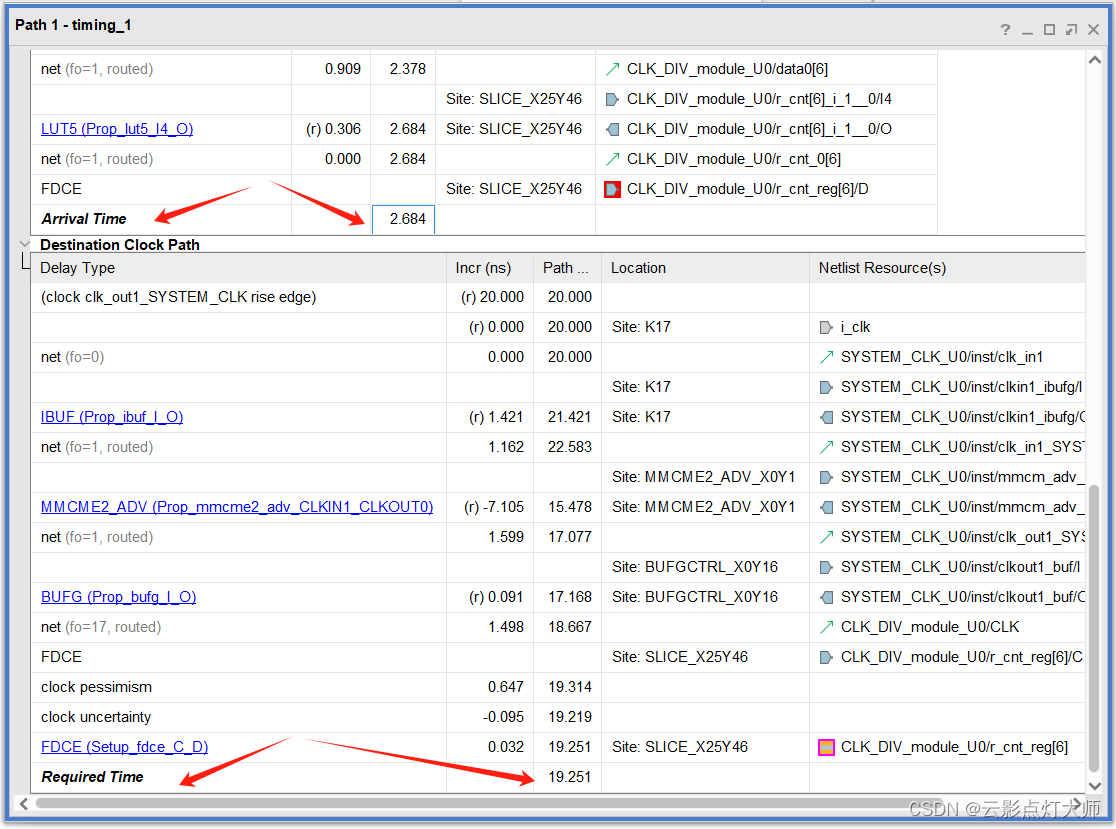

经过图上计算可得公式 :

Tsu裕量 = (Tskew + 时钟周期 - Tsu) - (Tco + Tdelay)

Thd裕量 = Tco + Tdelay - Thd

两个时间都大于0,才能保证系统不产生亚稳态。

建立时间裕量、组合逻辑延时决定时钟最高频率

一级逻辑级数延迟约为0.4ns

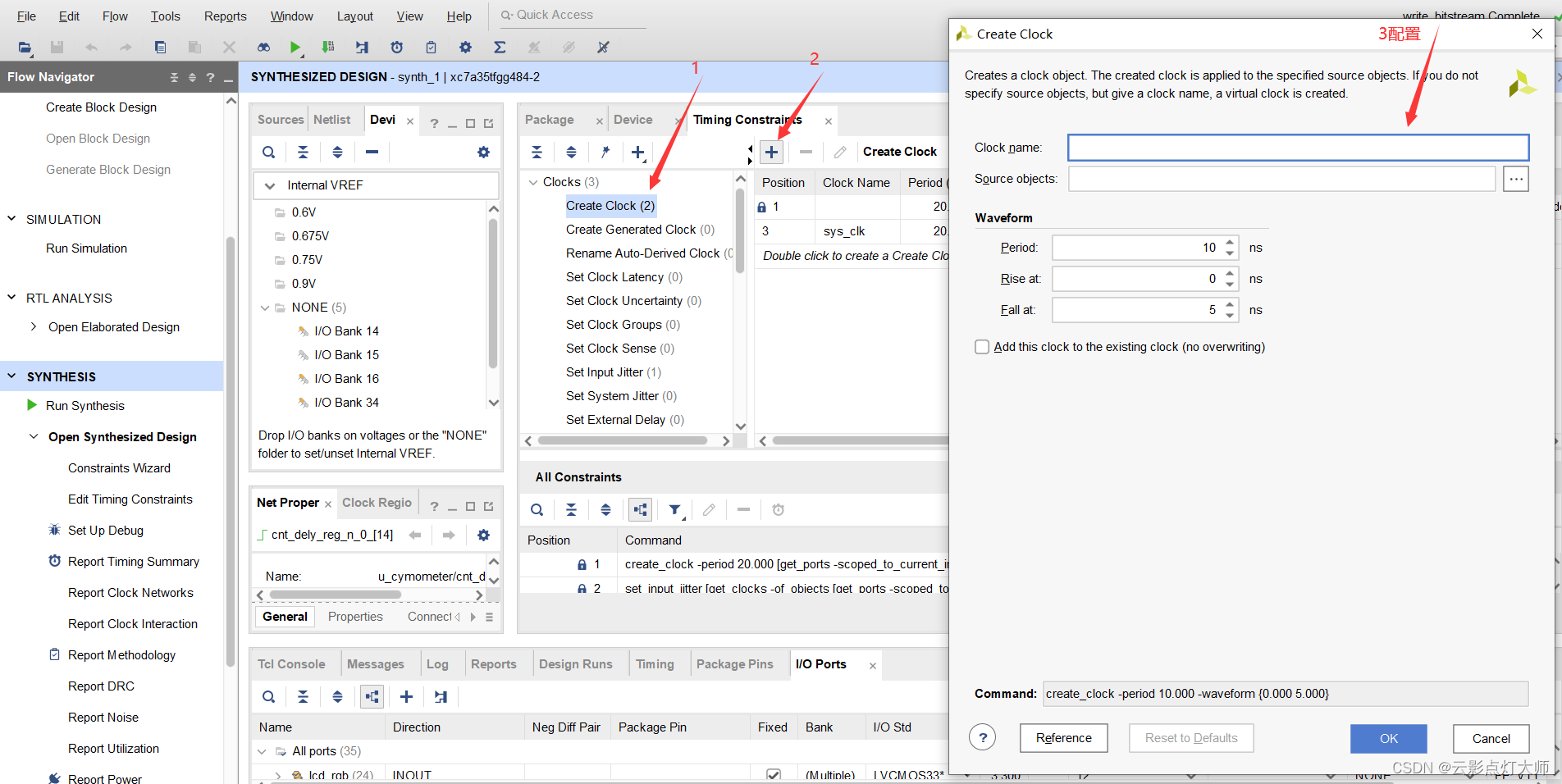

(3)时序约束操作

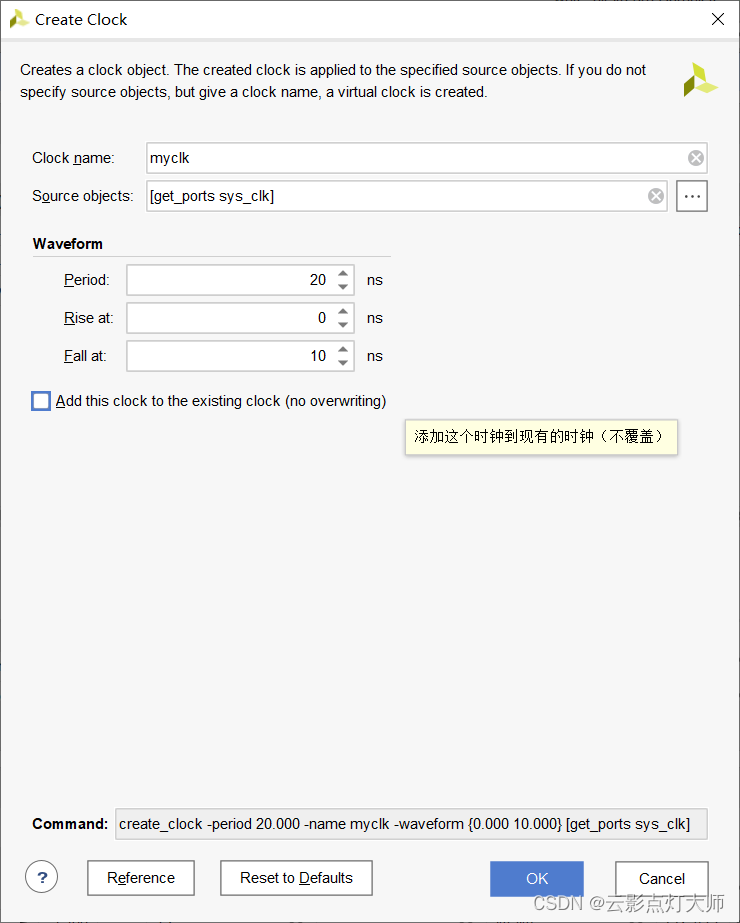

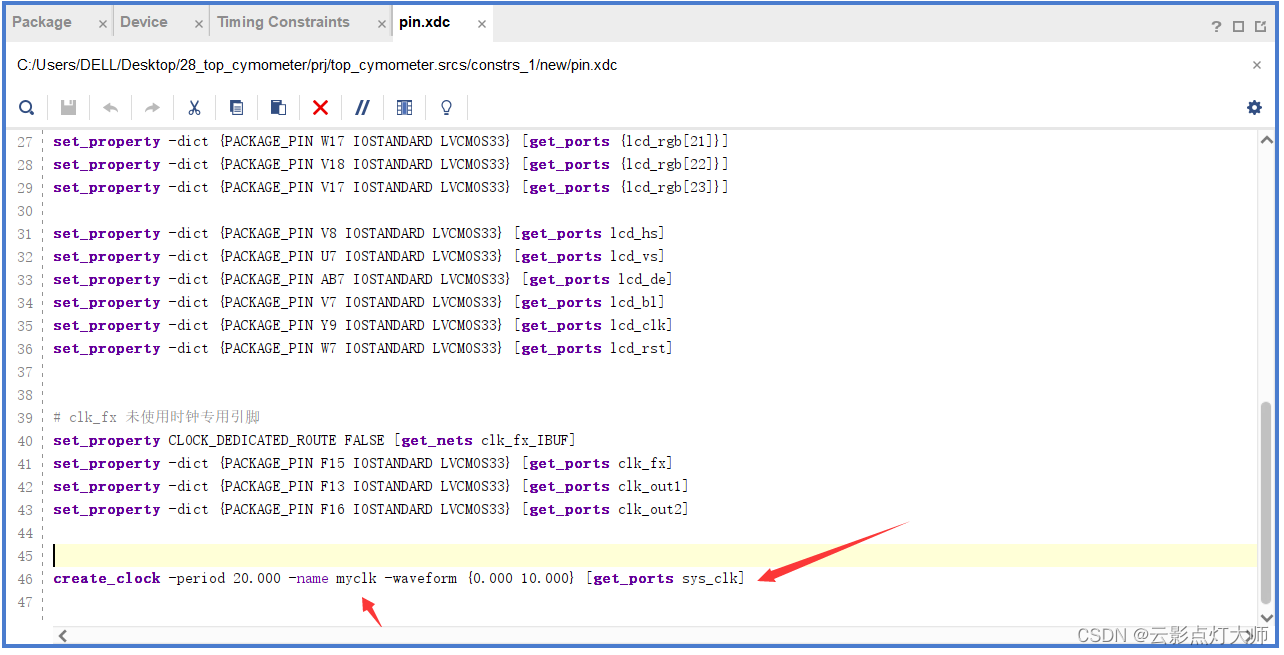

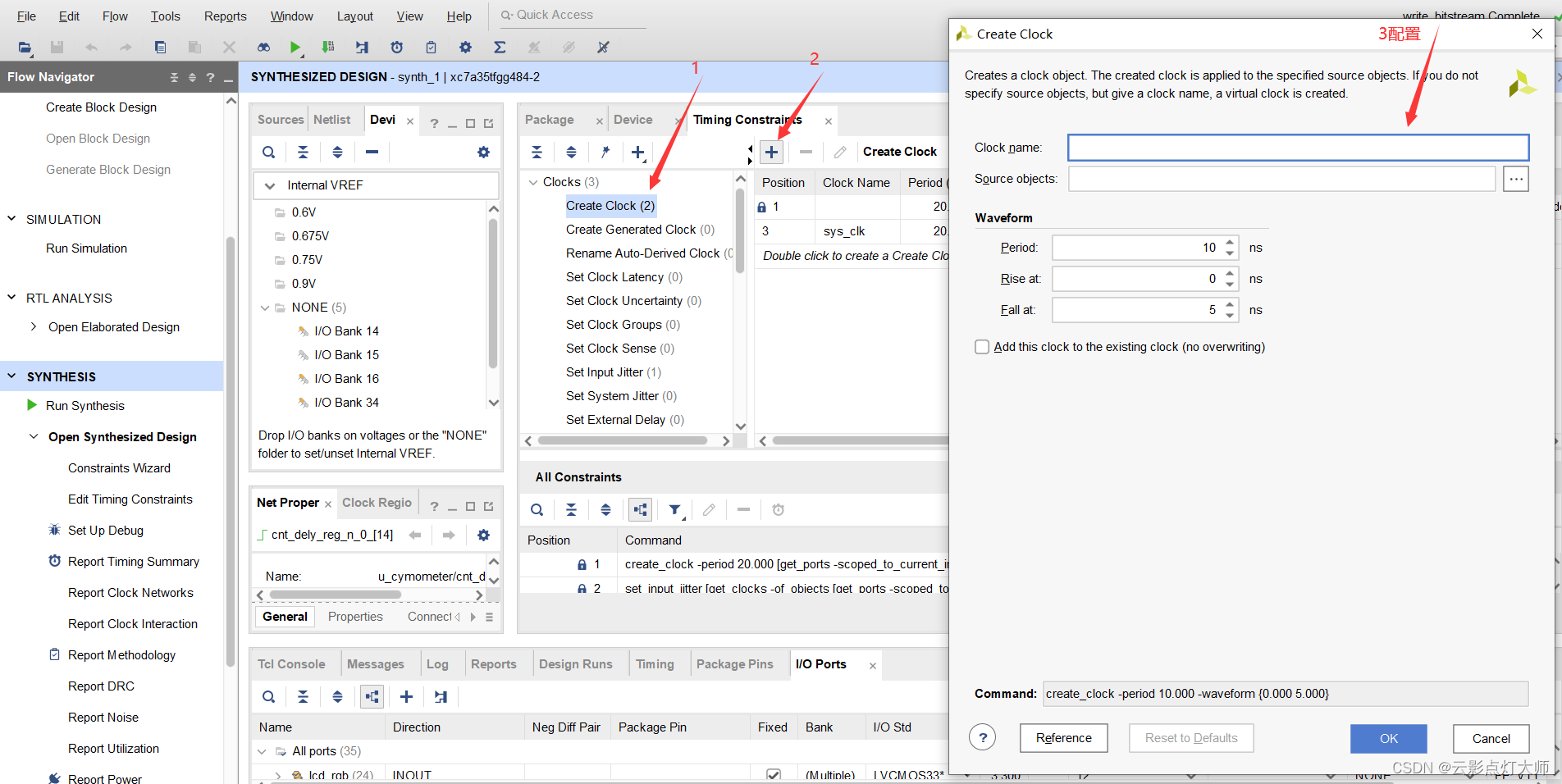

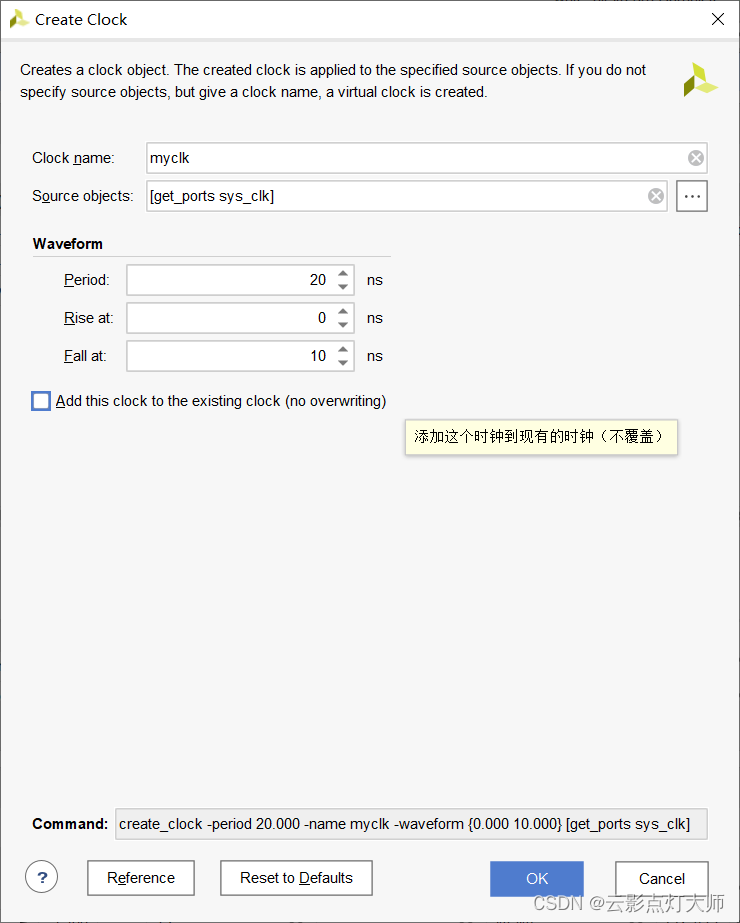

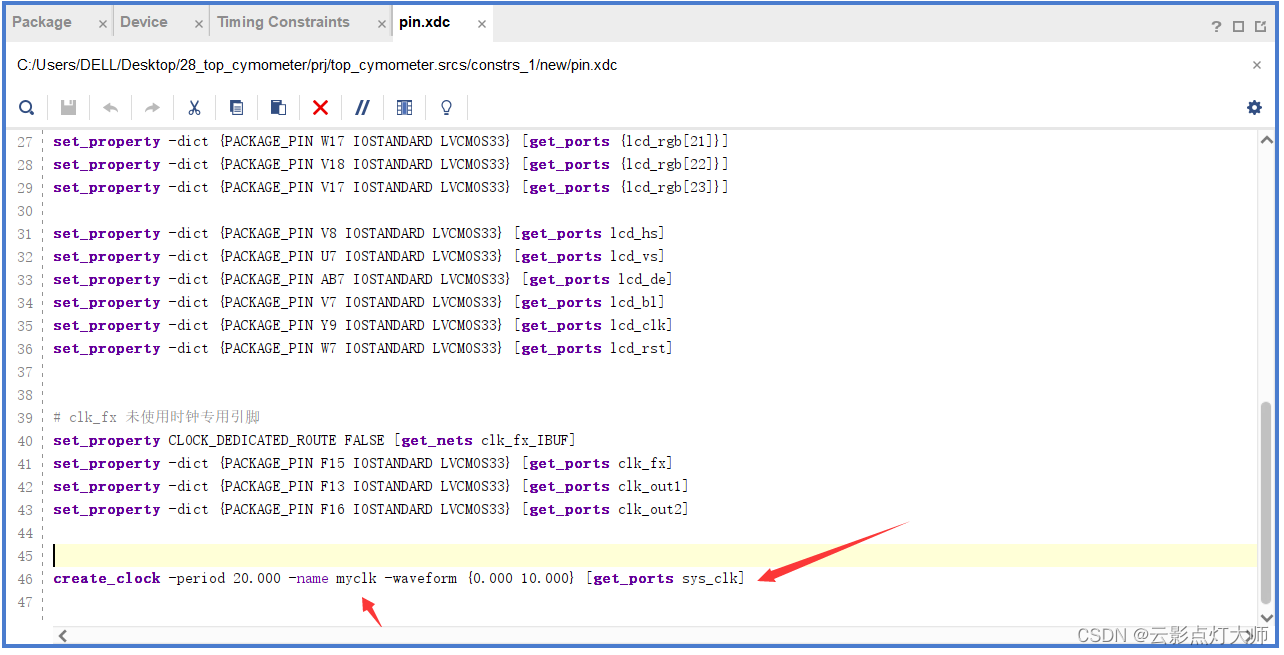

1 约束主时钟

结果

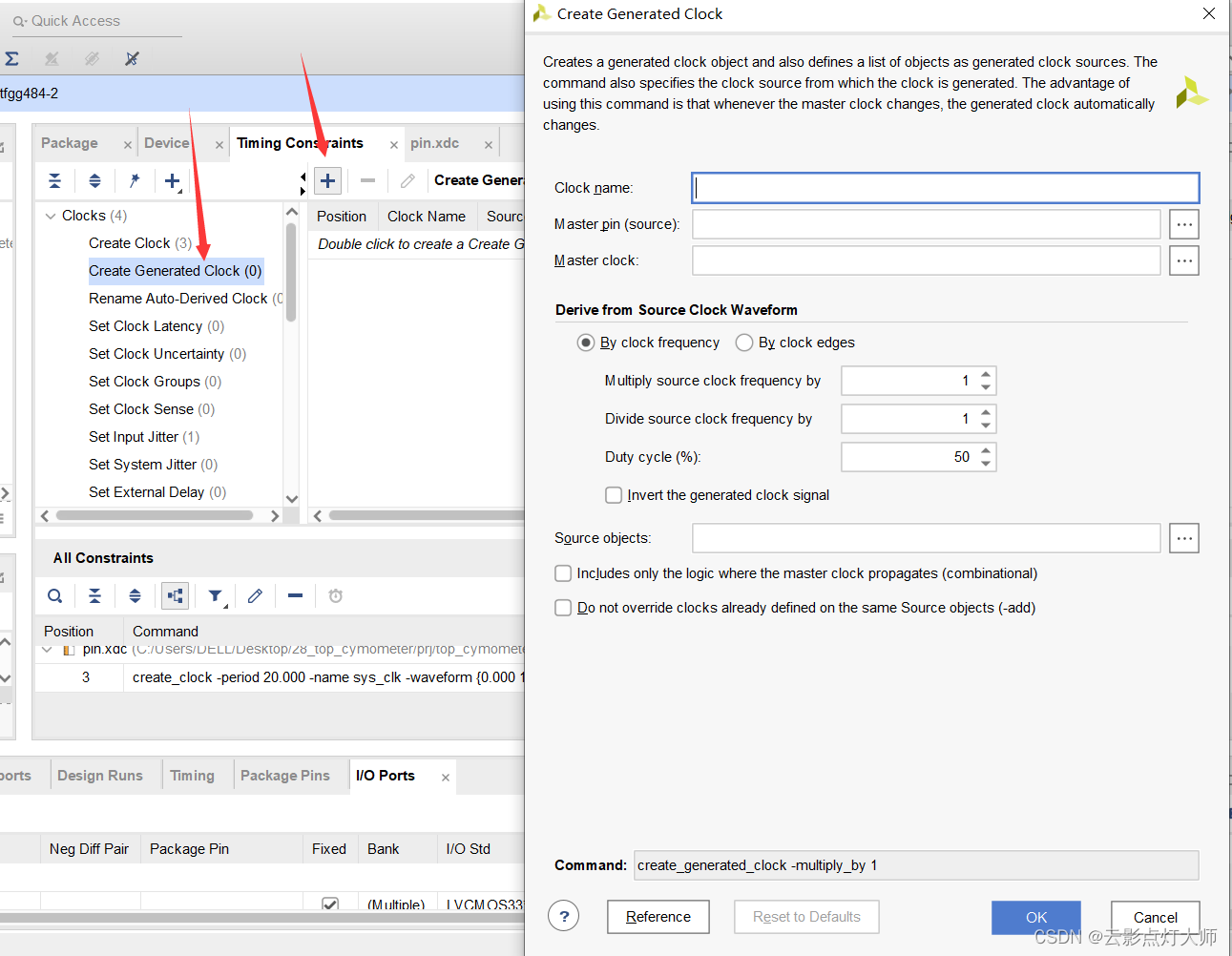

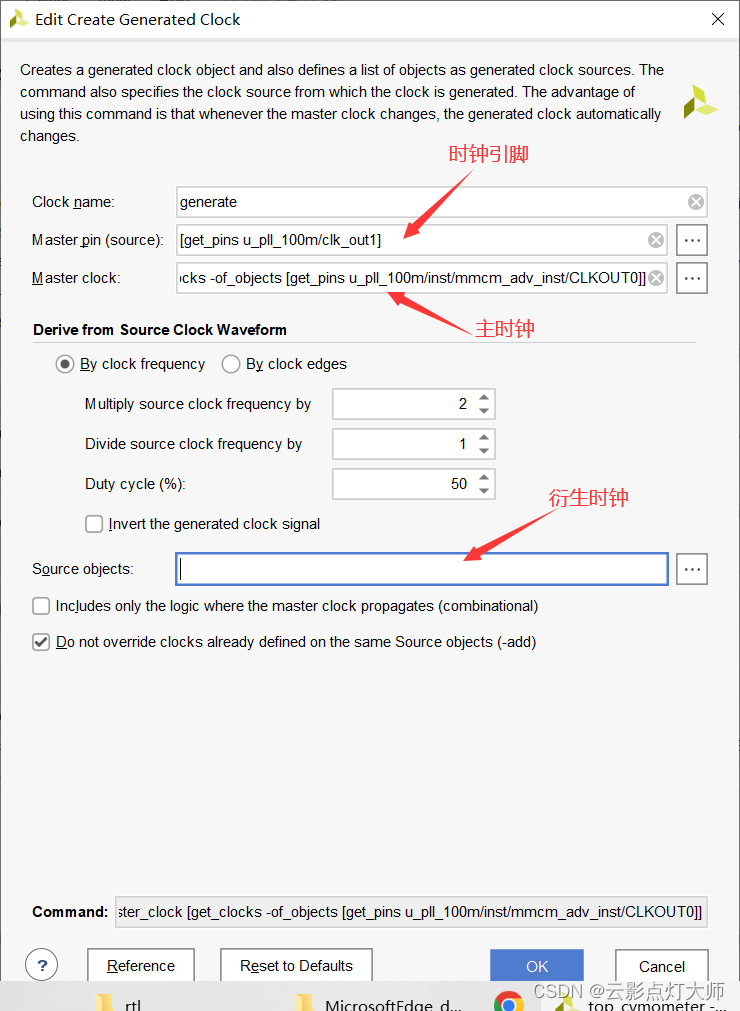

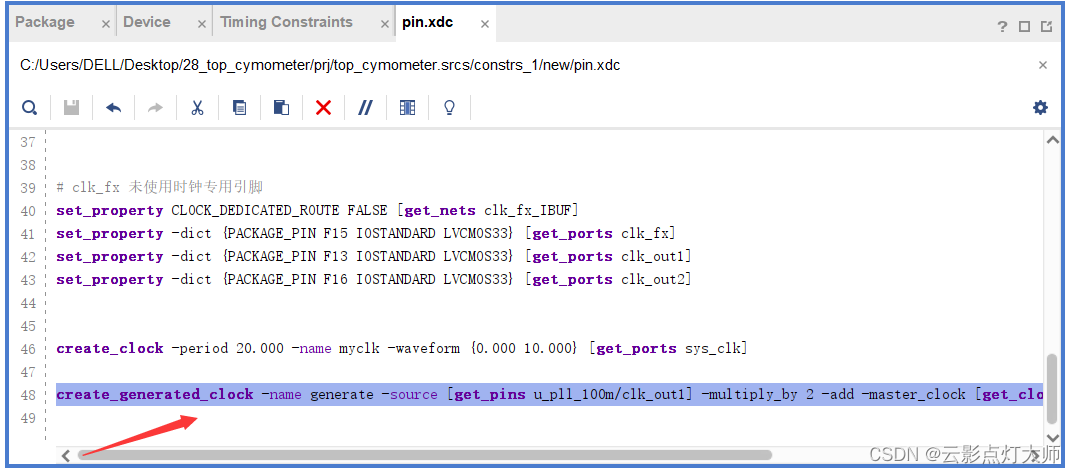

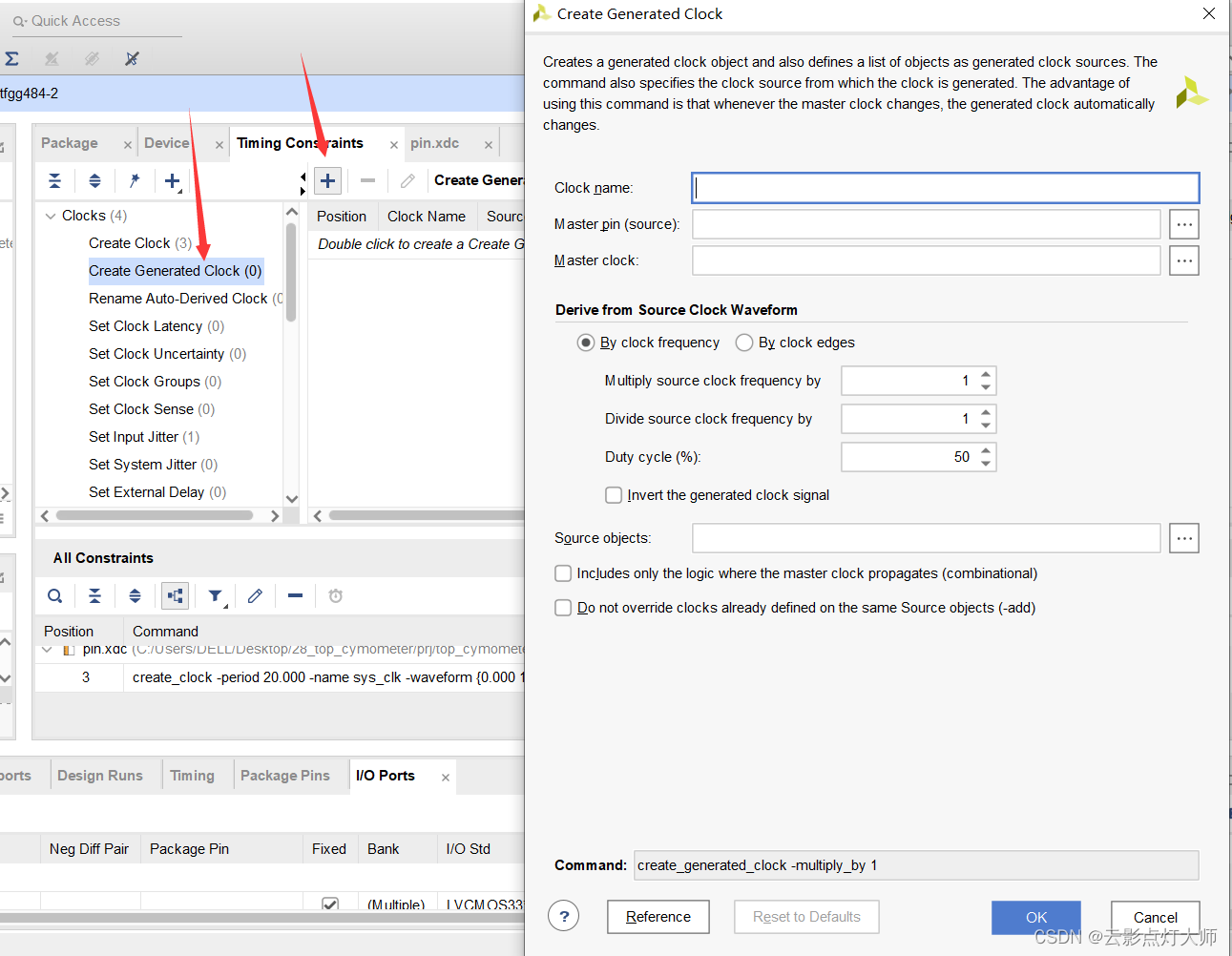

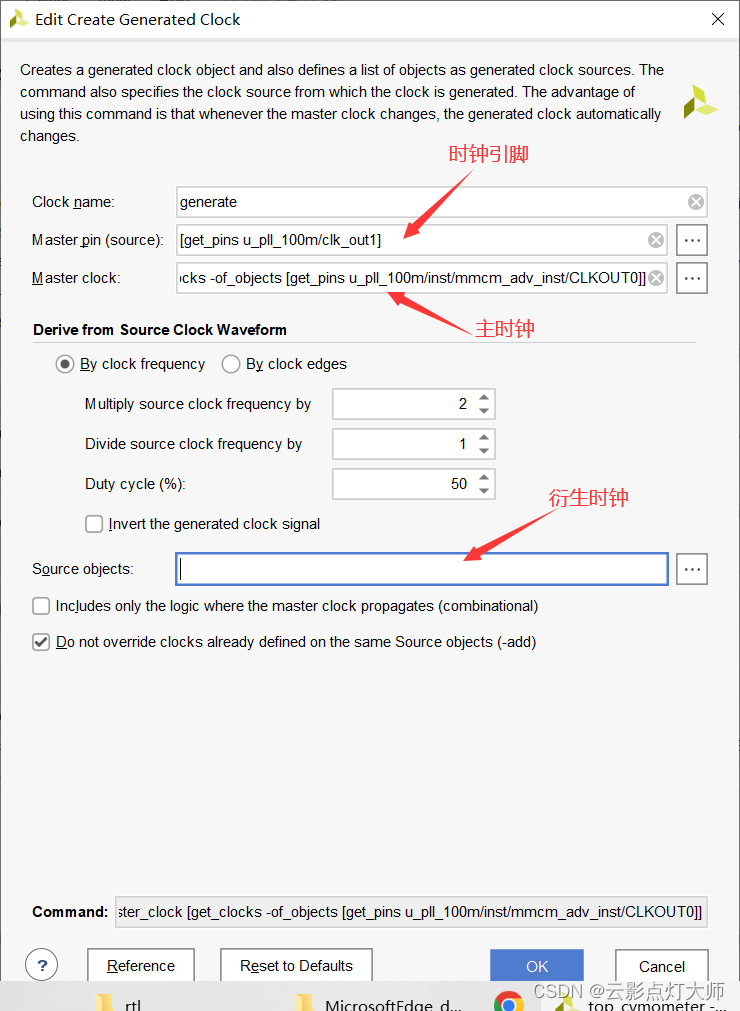

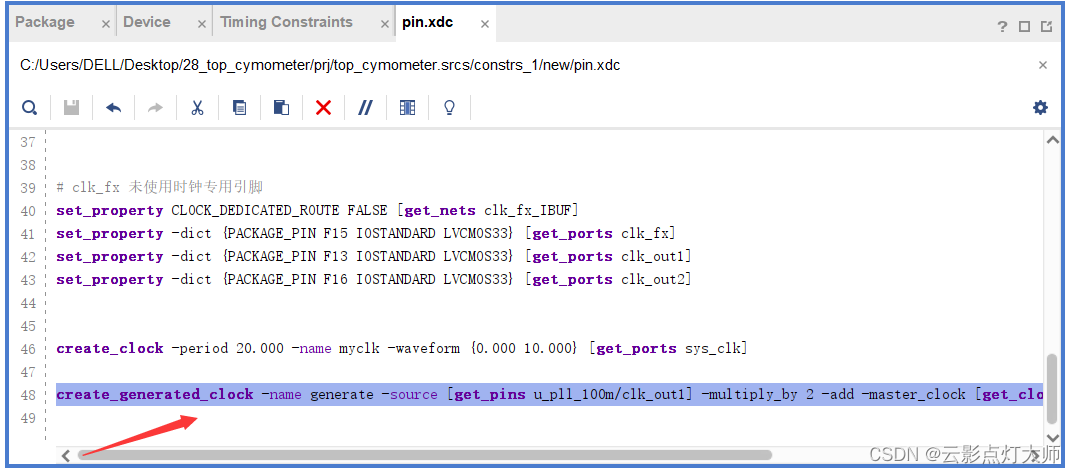

2 约束衍生时钟

结果

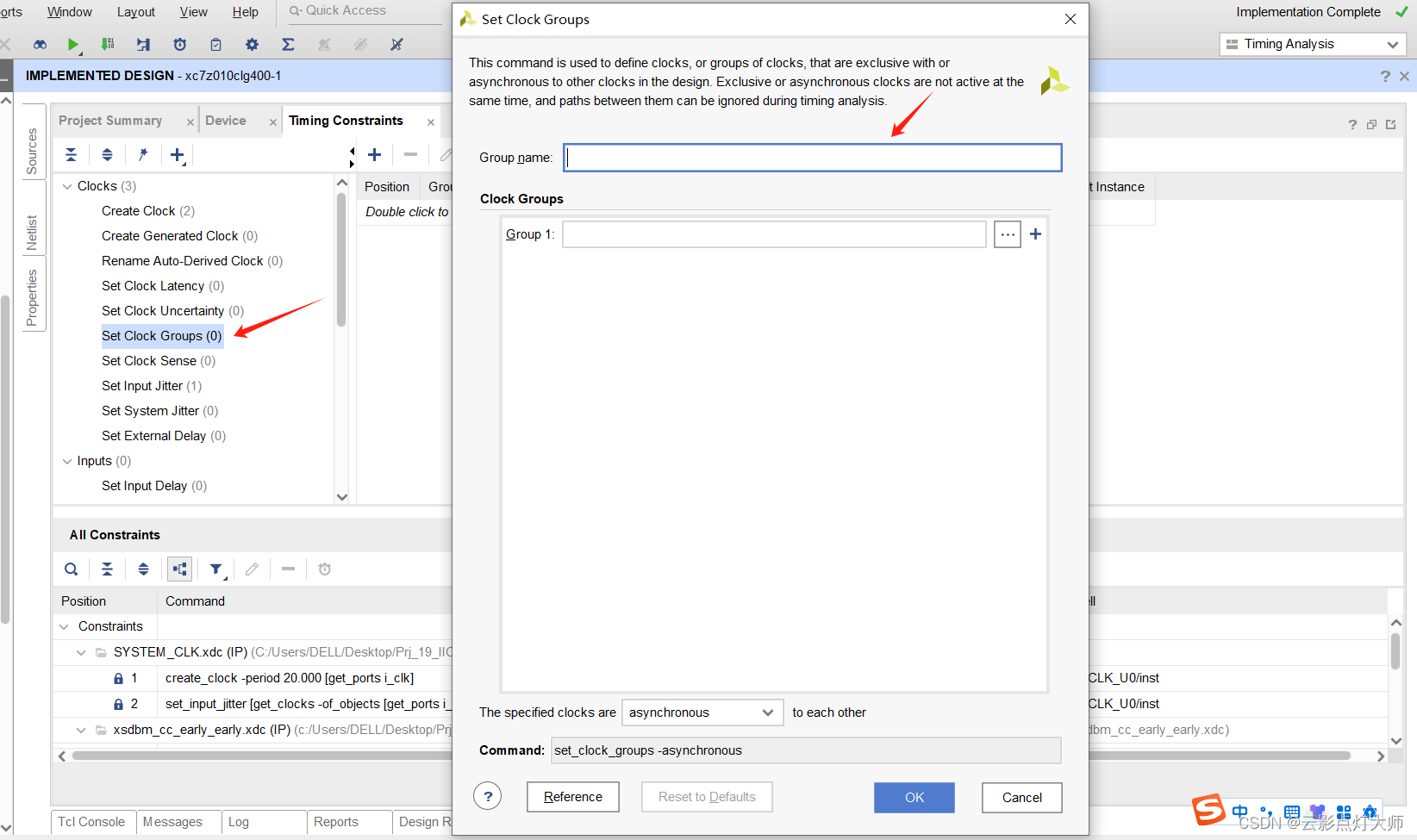

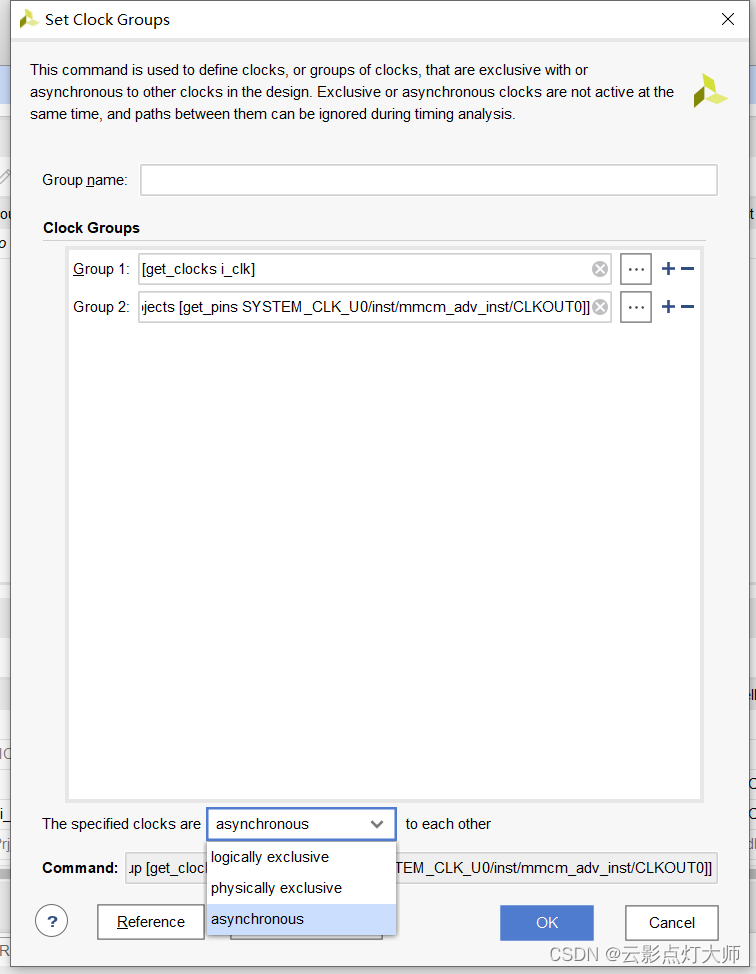

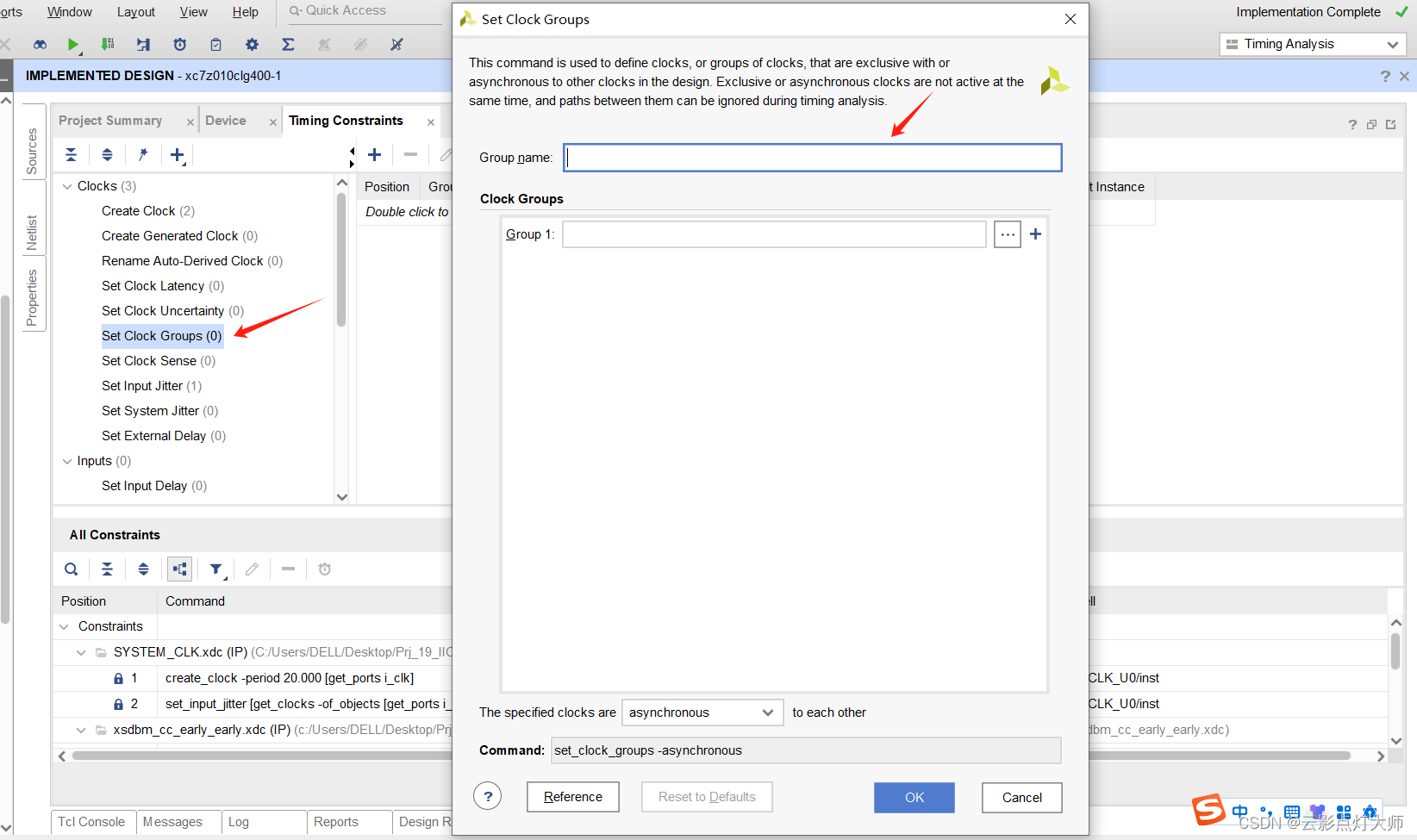

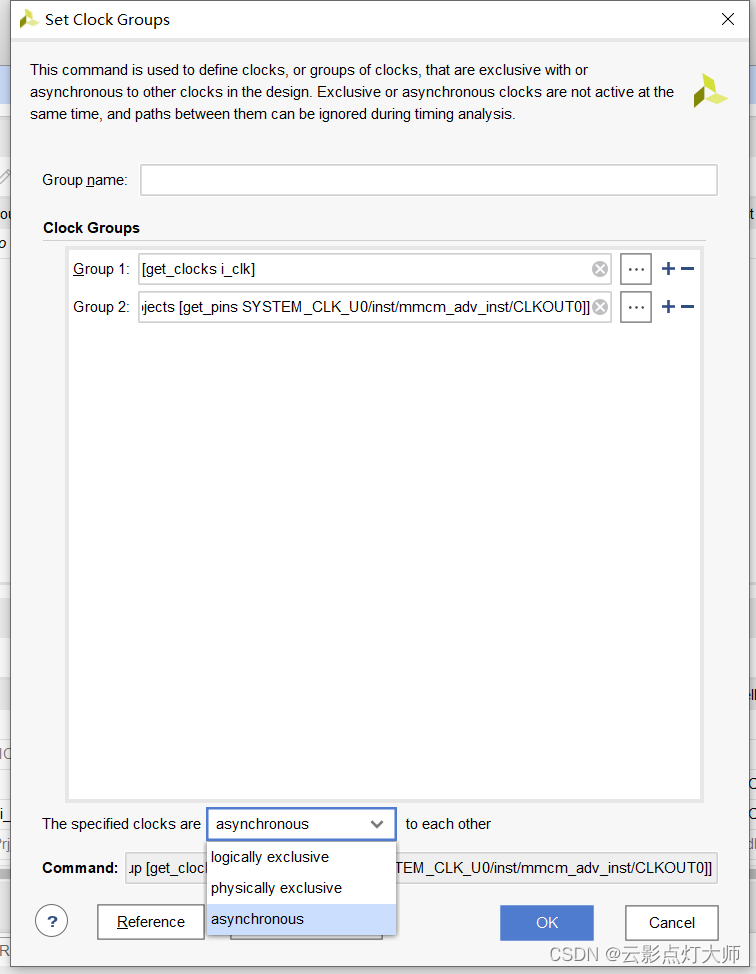

3 设置时钟组

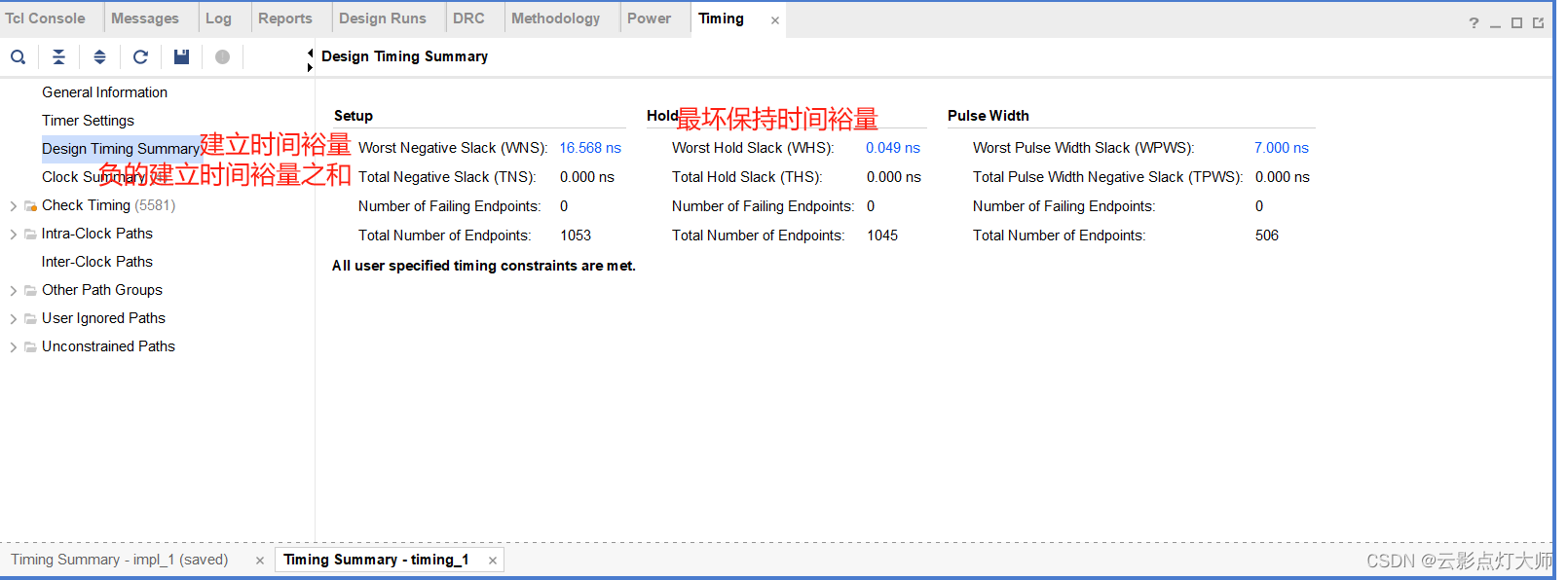

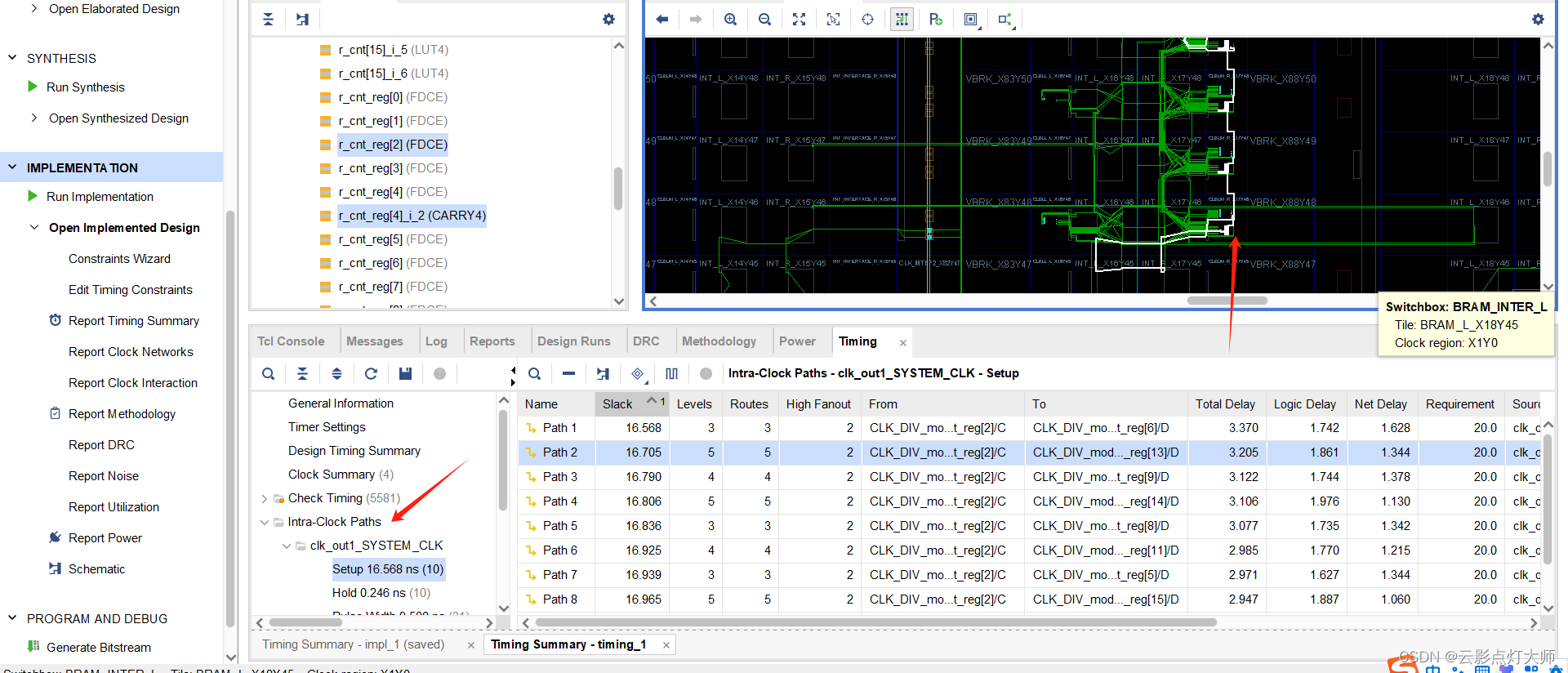

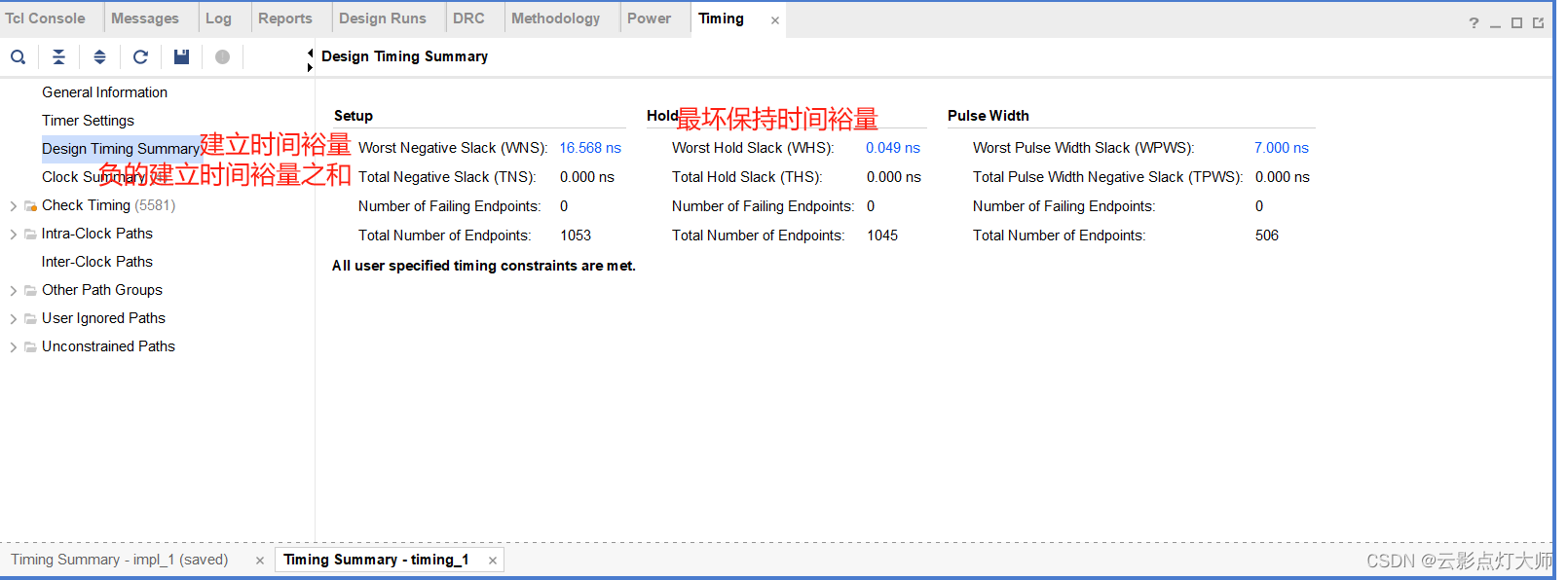

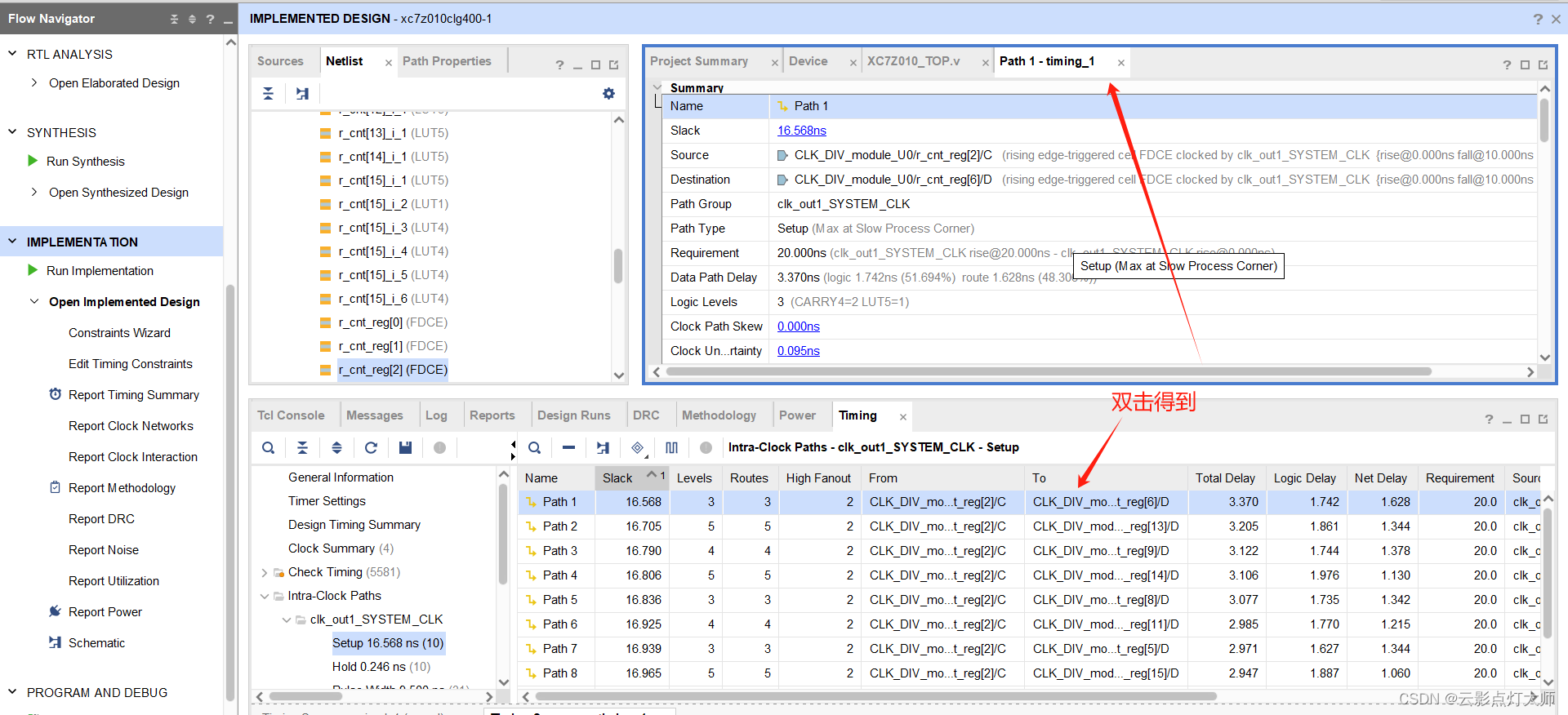

(4)查看报告

查看统计

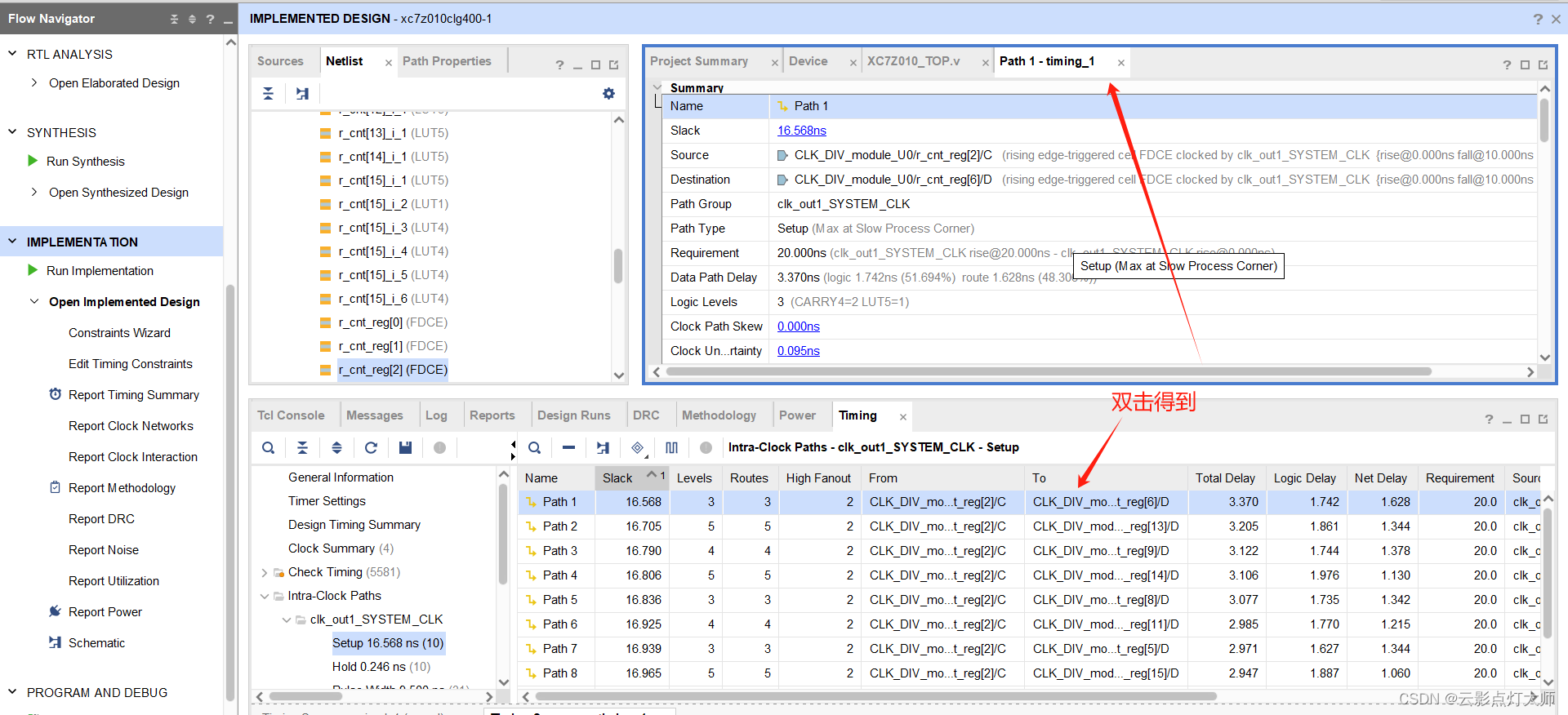

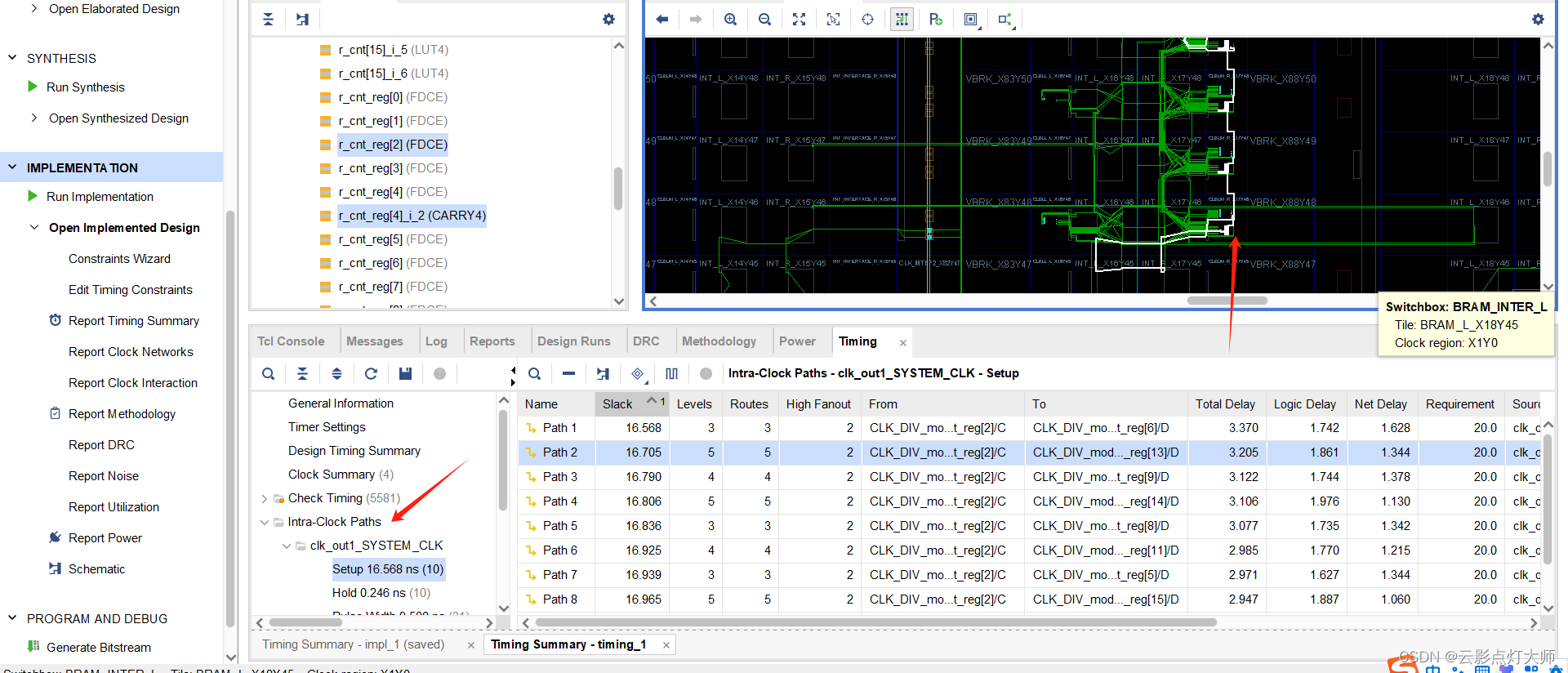

有问题分析路径

3.查看详细计算过程

原文地址:https://blog.csdn.net/Treasureljc/article/details/135531593

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。

本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。

如若转载,请注明出处:https://www.suanlizi.com/kf/1748201638188945408.html

如若内容造成侵权/违法违规/事实不符,请联系《酸梨子》网邮箱:1419361763@qq.com进行投诉反馈,一经查实,立即删除!