一、实验目的

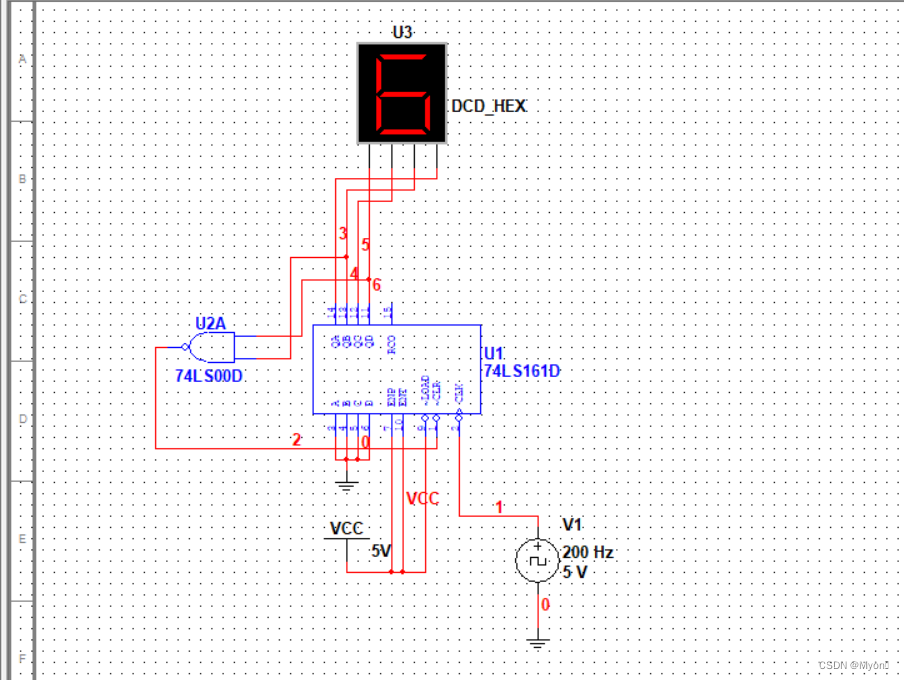

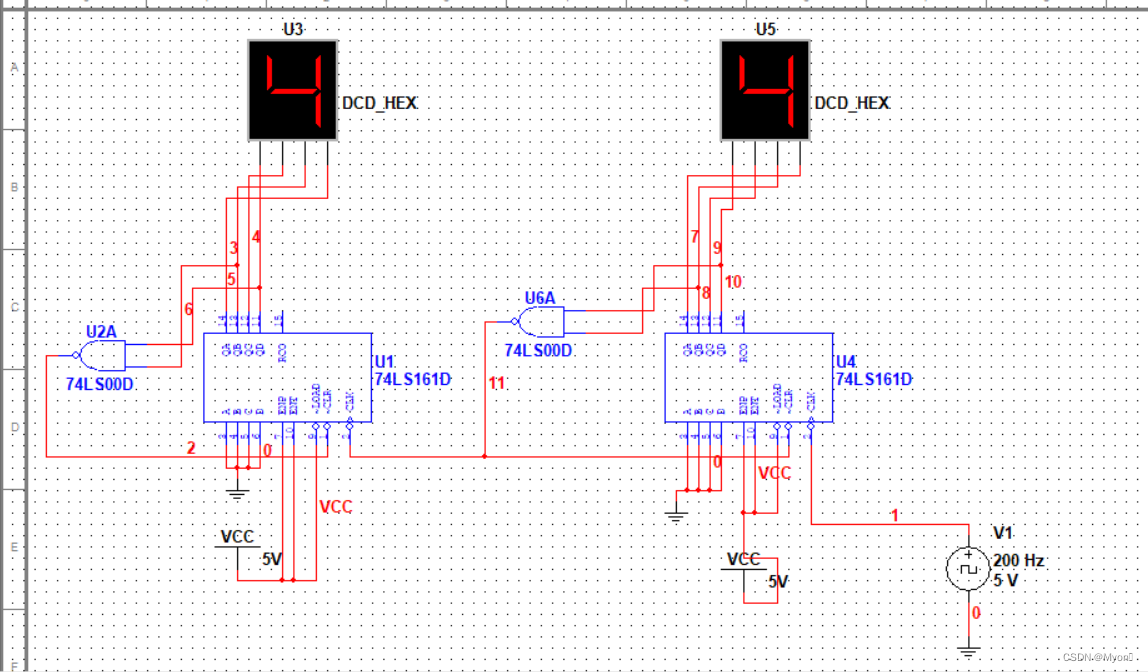

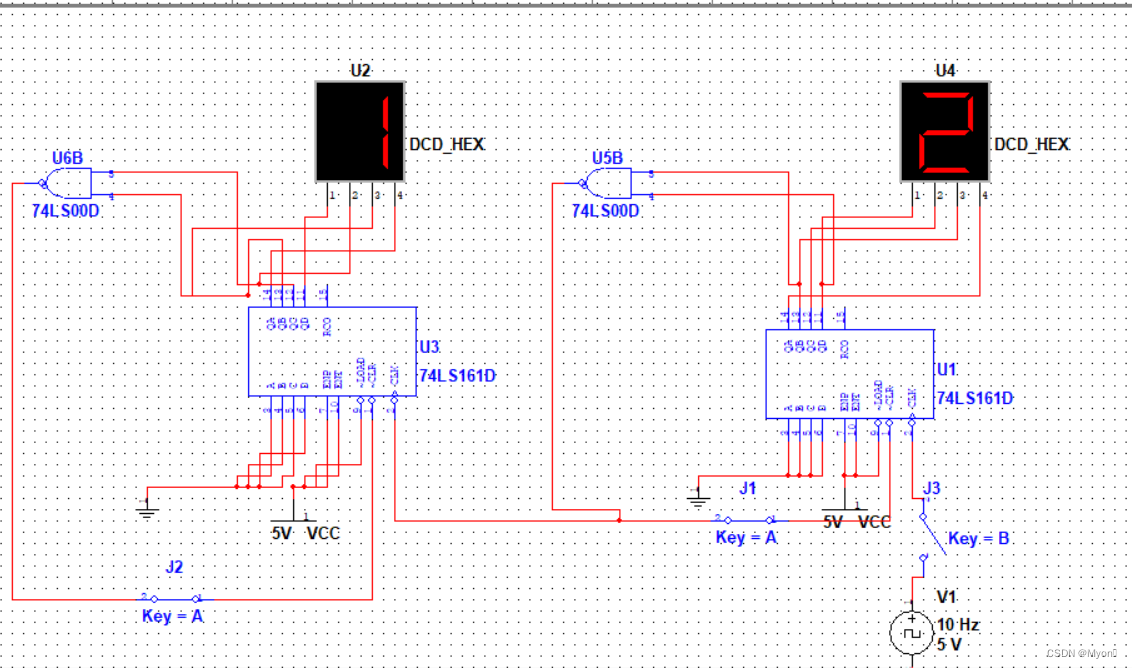

1.进一步理解用中规模集成计数器构成任意进制计数器的原理。

2.了解计数器的简单应用。

3.进一步学习与非门和译码显示器的使用方法。

4.学会用FPGA实现本实验内容。

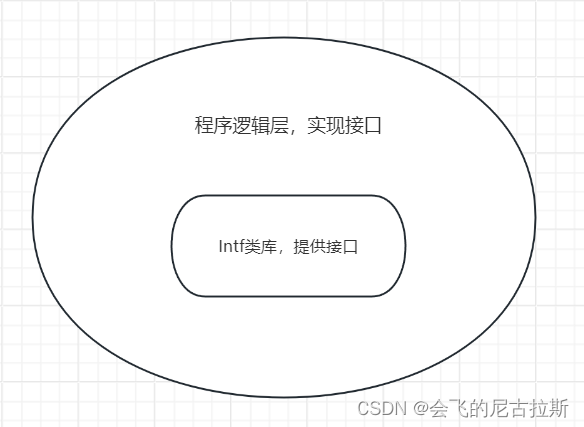

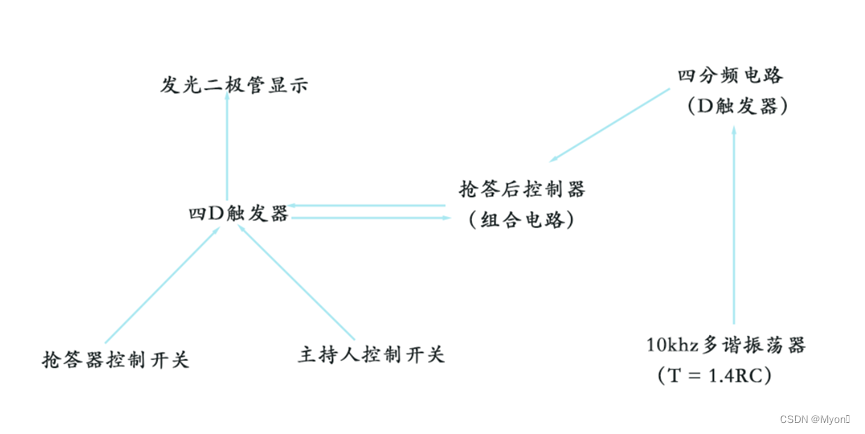

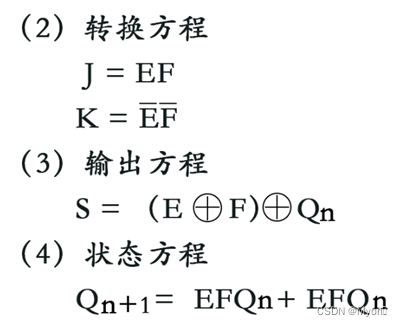

二、实验原理

简单秒表

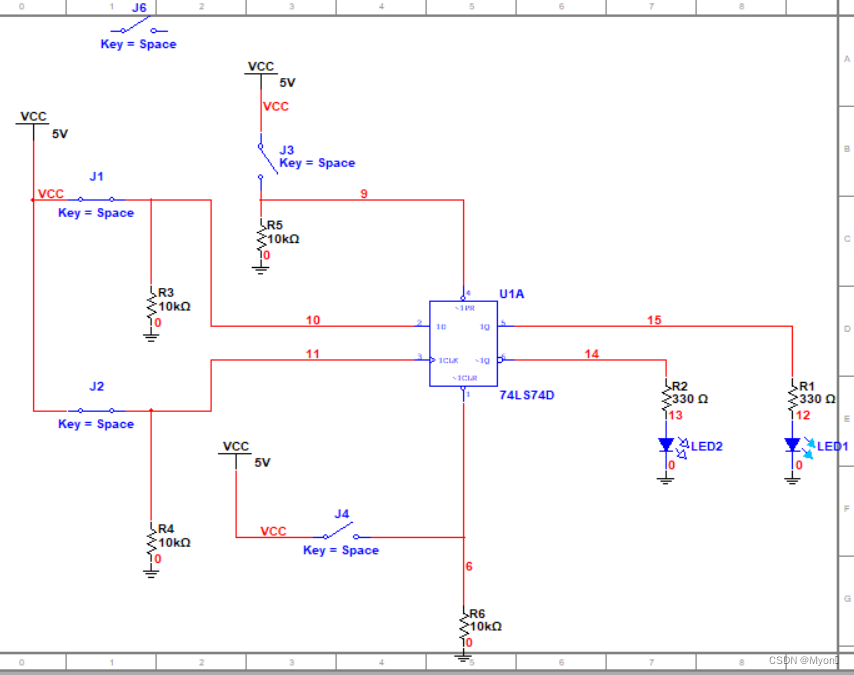

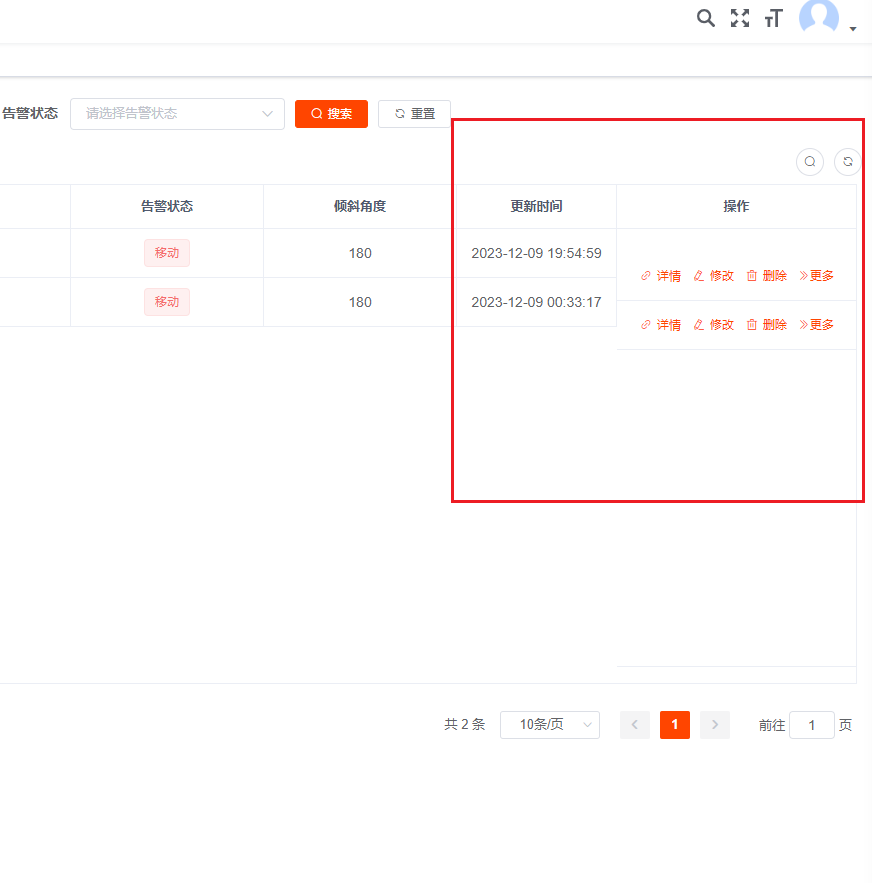

可暂停、复位秒表

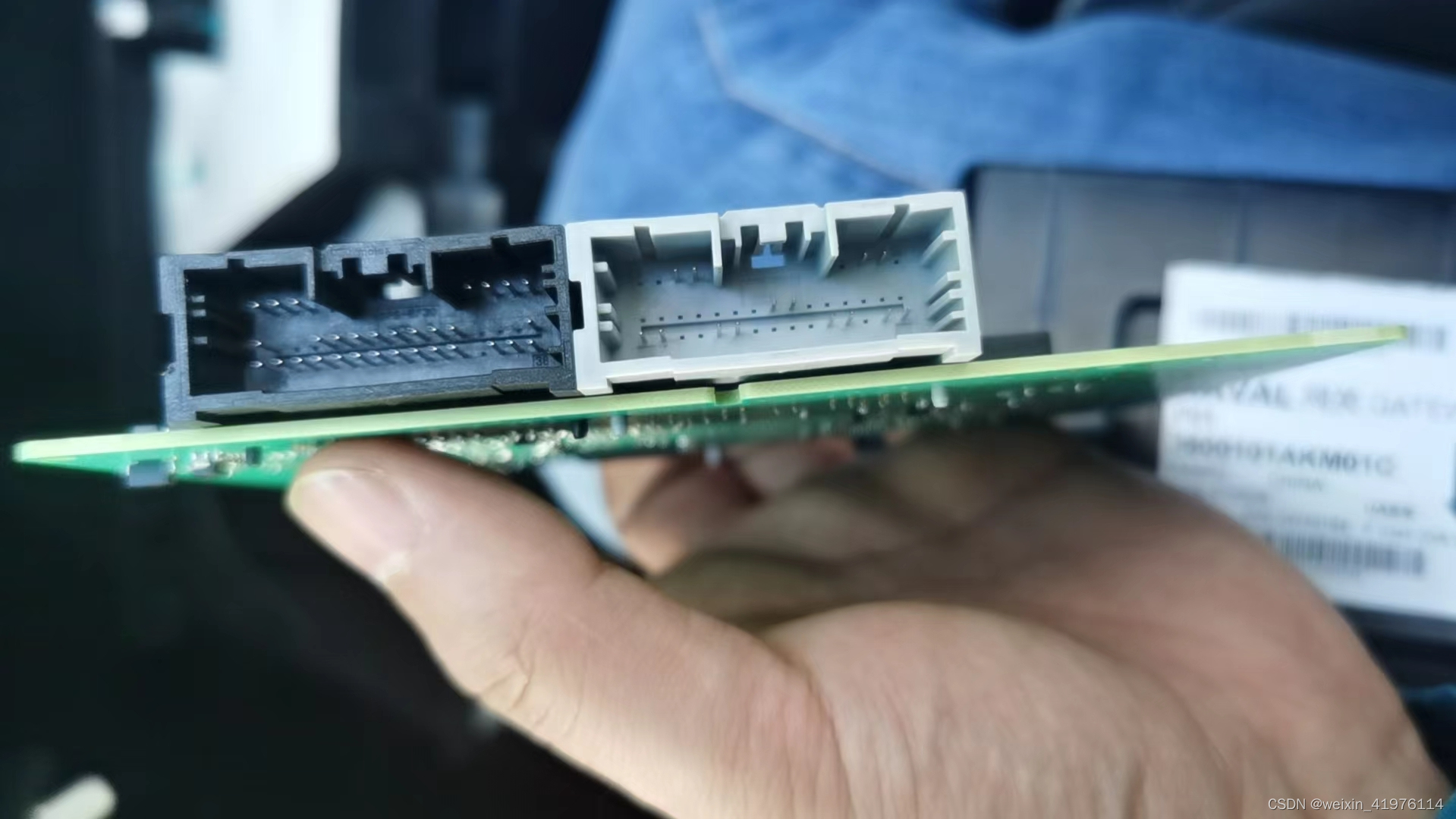

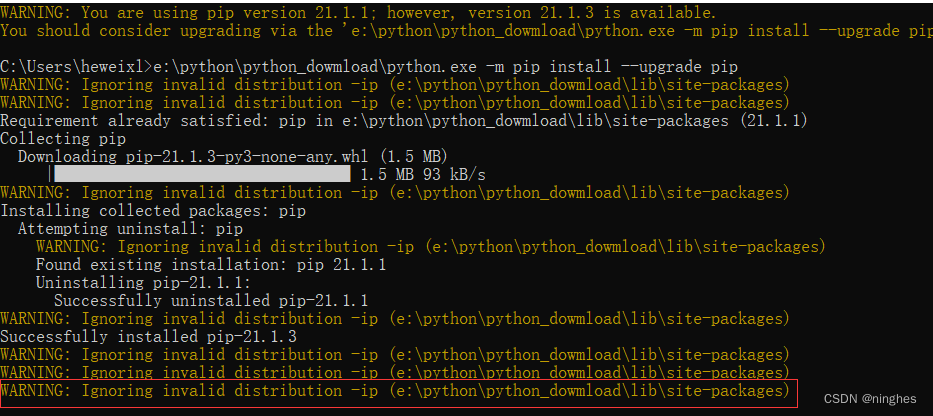

三、程序清单(每条语句必须包括注释或在开发窗口注释后截图)

原理代码

module clock_y#

(

parameter WIDTH = 24,

parameter N = 12000000

)

(

input wire clk,rst,

input wire key,

output wire [8:0]segment_led_1,segment_led_2

);

reg [7:0]cnt;

reg flag;

![[Linux] Tomcat](https://img-blog.csdnimg.cn/direct/fd5170707a724147988438c813854217.png)