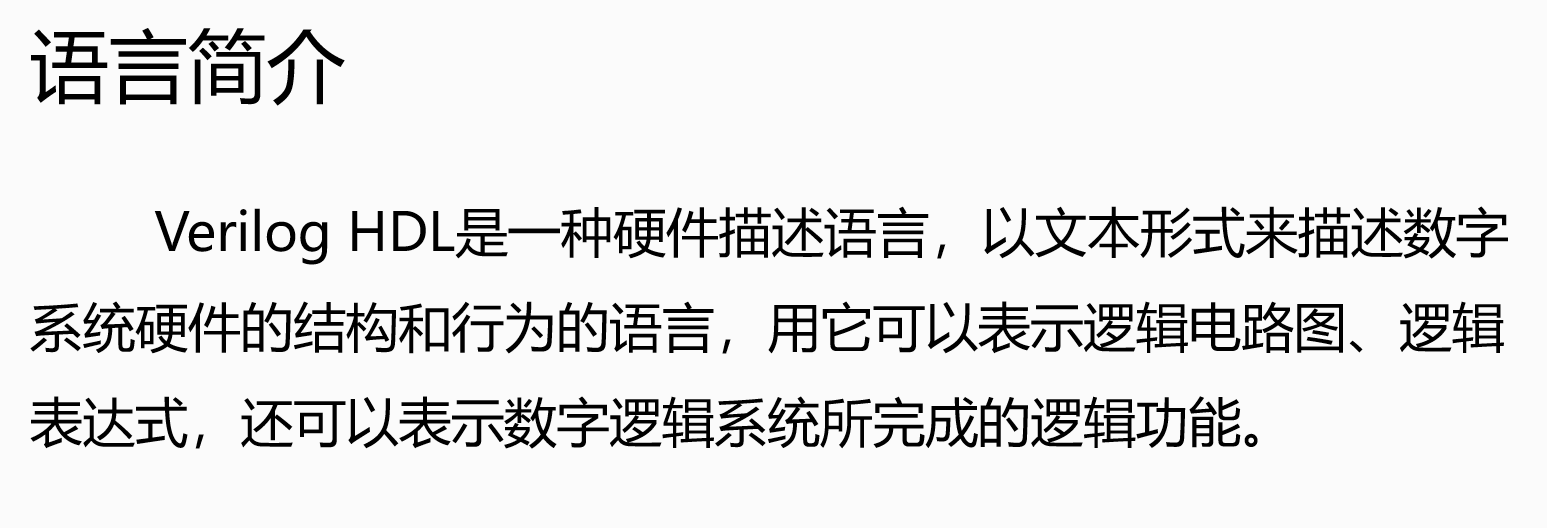

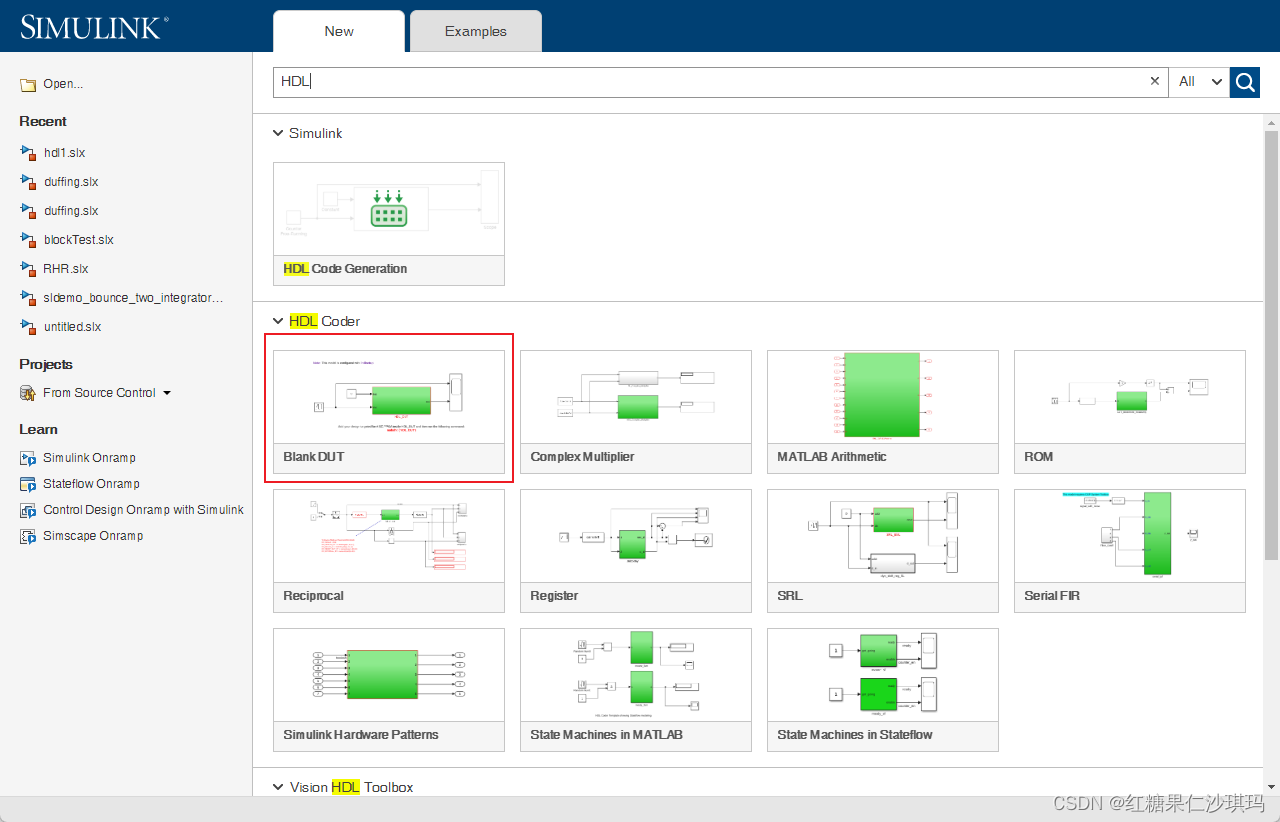

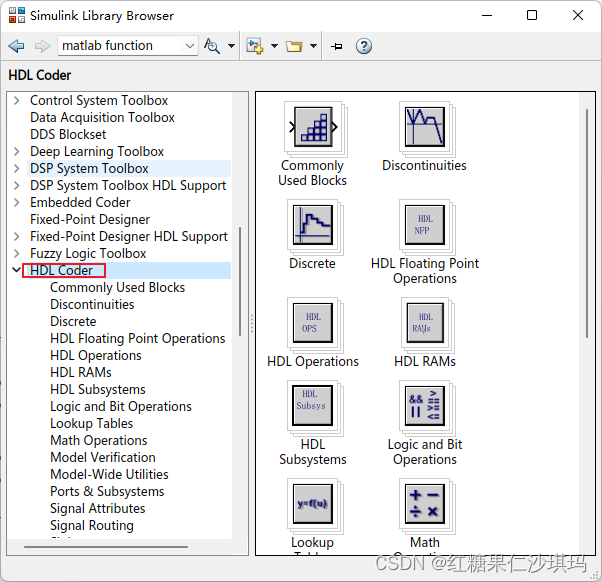

首先在simlink中找到HDL CODER

打开红色Blank DUT,进入里面绿色的子系统开始设计系统

打开红色Blank DUT,进入里面绿色的子系统开始设计系统

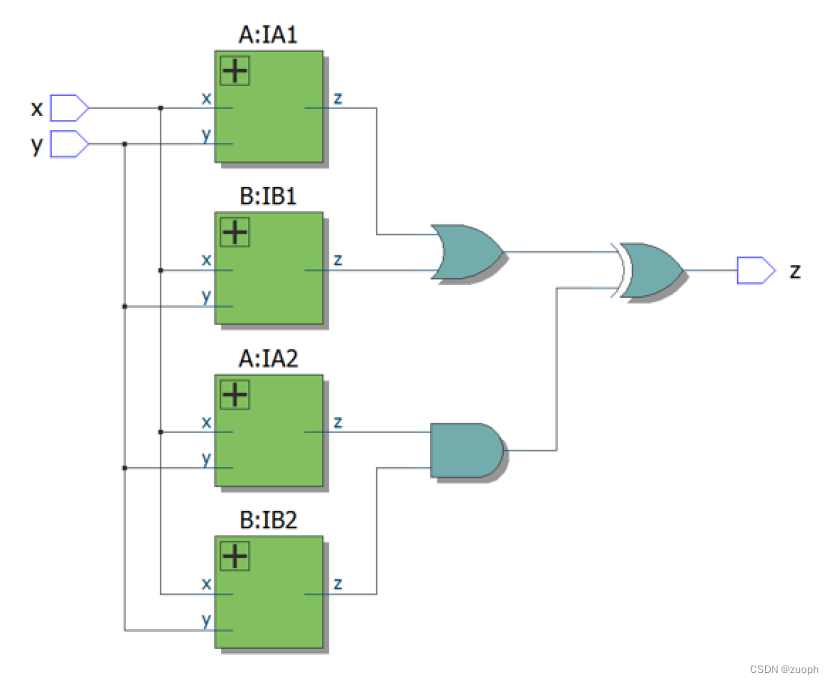

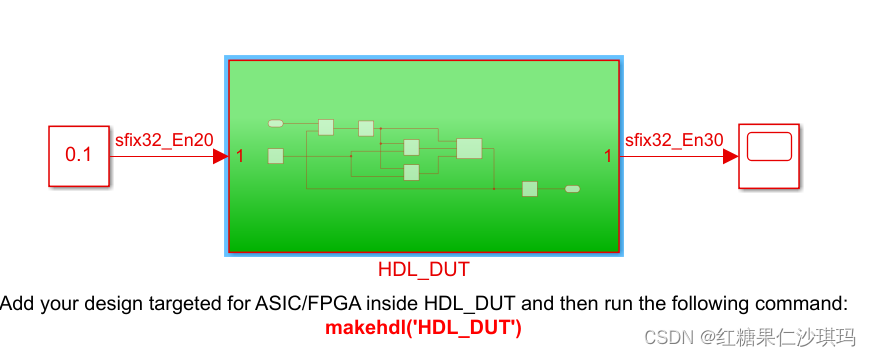

例如设计一个正弦信号发生器,里面用到了add、memory、relation operator、switch、constant、cos模块,cos模块选择了cordic算法,使用cordic那么输入值的范围为【-2pi,2pi】,超过则错误,memory起到累加的效果,in1是每次累加的值,当累加值大于2pi则将其变为in1-2pi,这是因为cosx=cos(x-2pi)

之后记得将constant这些模块设置为定点数,如果是浮点数则需进行额外设置,暂时没学

这些所用的模块都在HDL里面选择

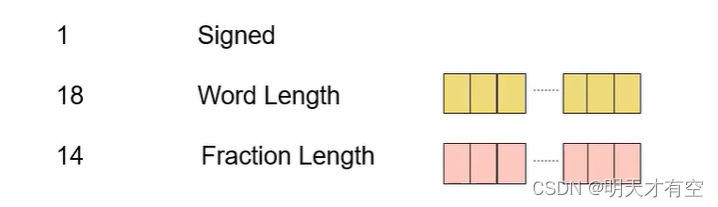

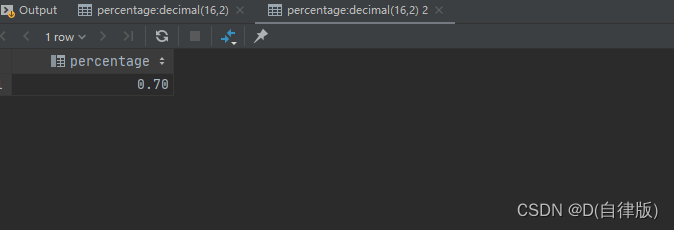

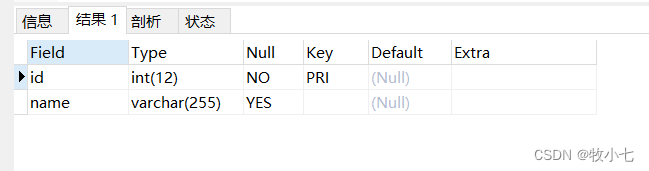

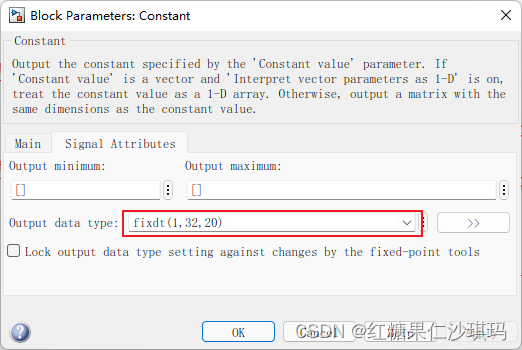

设置定点小数这里选择了有符号32位,20位小数,表示为sfix32_en20,例如对模块2*pi设置,如下

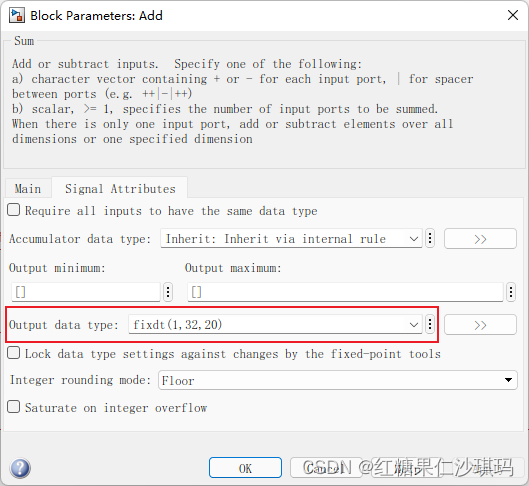

fixdt(1,32,20)中,1就是有符号,0是无符号,32是所用比特数,20就是小数用了多少比特数,其中在使用乘法器、除法器、减法器等,根据定点小数运算,输出的定点小数位数会变化,例如例子中的加法器输出会变成sfix33_en20,可以点击加法器调整

想其他模块的data type选择inherit via internal rule就行了,系统根据输入自动分配数据类型。采样率也许设置,否则仿真会不对,如果采样率是inf转hdl会报错:Delay balancing unsuccessful because Signal rate of value inf foun

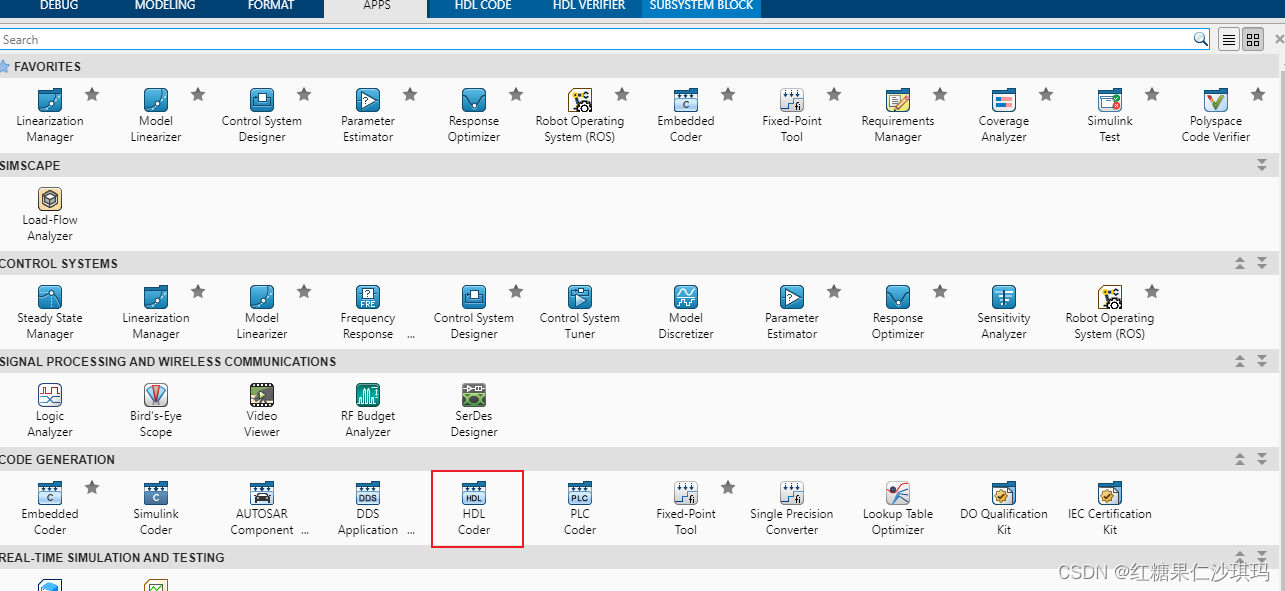

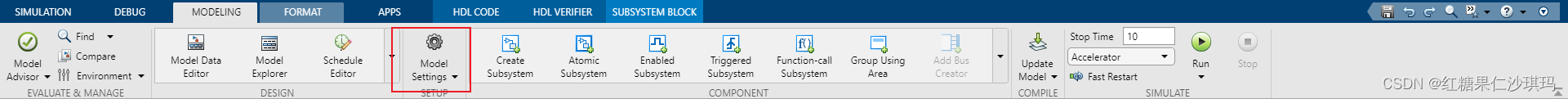

之后进行转化

或者

选择verilog并选择你hdl转化到那个文件夹(folder)

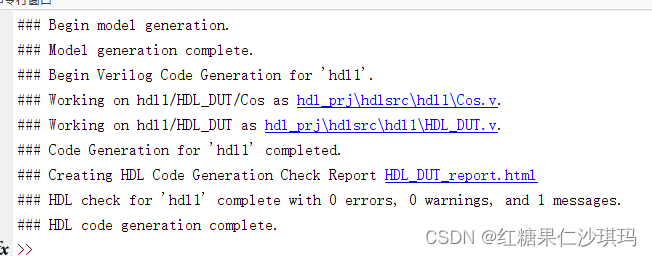

转化成功后会输出如下

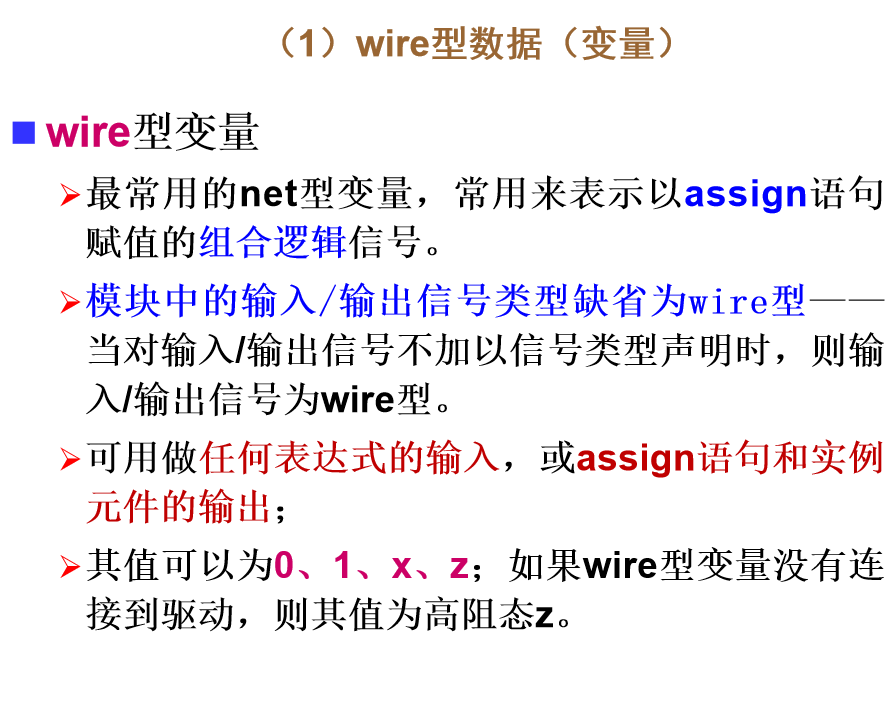

点击蓝色链接便可以看到Verilog程序,将其代入vivado进行测试,其中tb文件如下

module tb;

reg clk;

reg reset;

reg clk_enable;

reg signed [31:0] In2;

wire ce_out;

wire signed [31:0] Out1;

HDL_DUT M

(clk,

reset,

clk_enable,

In2,

ce_out,

Out1);

initial clk=1;

always #10 clk=~clk;

initial begin

reset=1;

clk_enable=1;

In2=32'h19999;

#100;

reset=0;

end

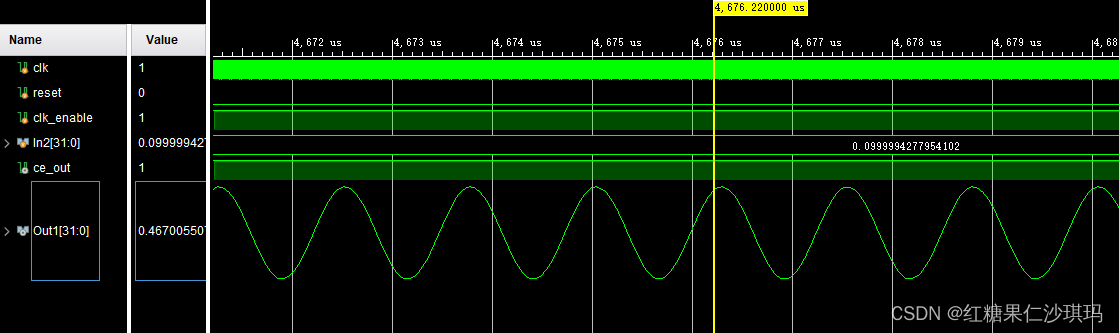

endmodule输出仿真结果正确如下