本文介绍一下常用的存储芯片DDR3,包括DDR3的芯片型号识别、DDR3芯片命名、DDR3的基本结构等知识,为后续掌握FPGA DDR3的读写控制打下坚实基础。

一、DDR3芯片型号

电路板上的镁光DDR3芯片上没有具体的型号名。

如果想知道具体的DDR3芯片型号,那怎么办?

这里我们首先要知道DDR3芯片信号丝印的信息含义:

第一行数字字母表示产地等信息。

第二行数字字母表示FBGA Code。

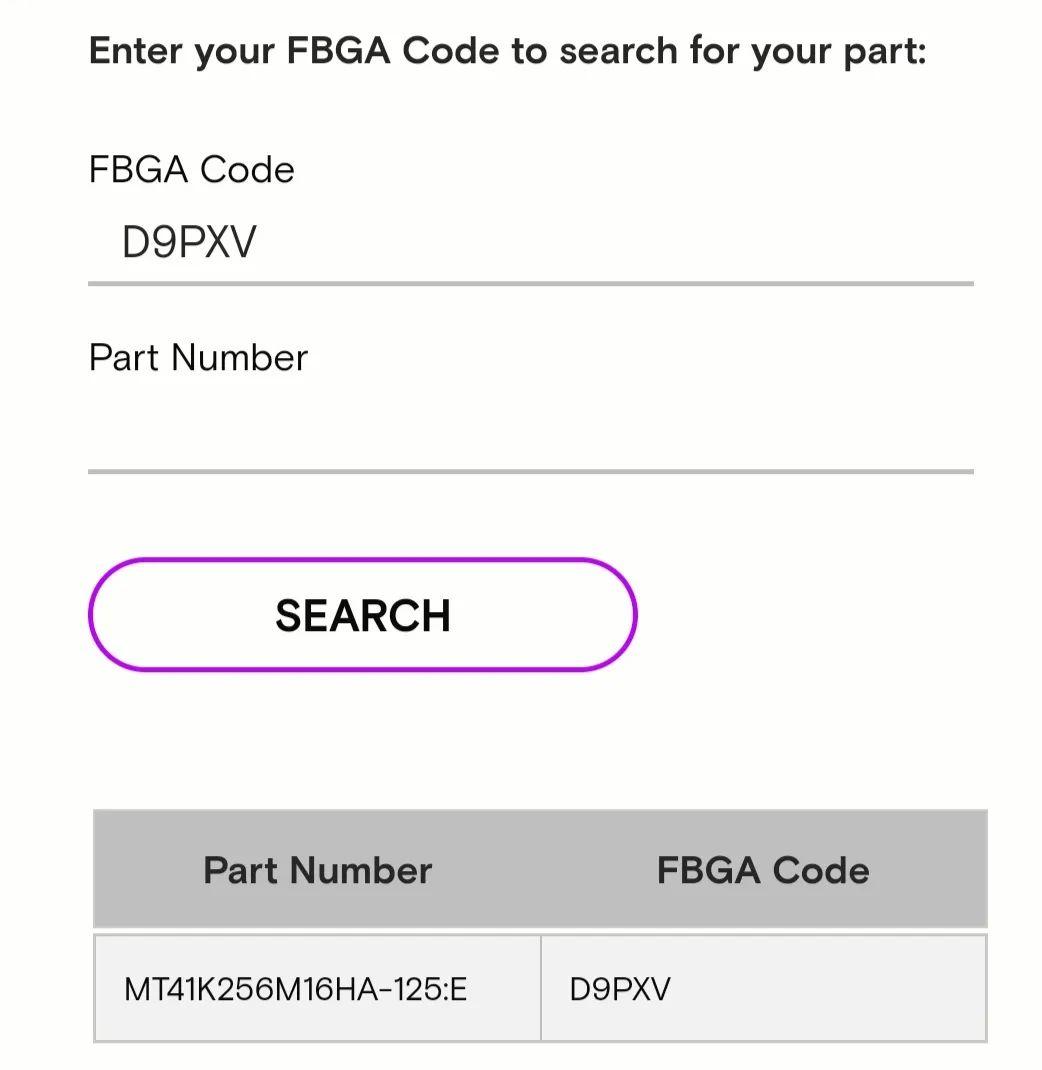

将FBGA Code这串数字,输入下面这个镁光的官网网址,即可查询:

https://www.micron.com/support/tools-and-utilities/fbga

这里我们来试一下:

二、DDR3芯片命名

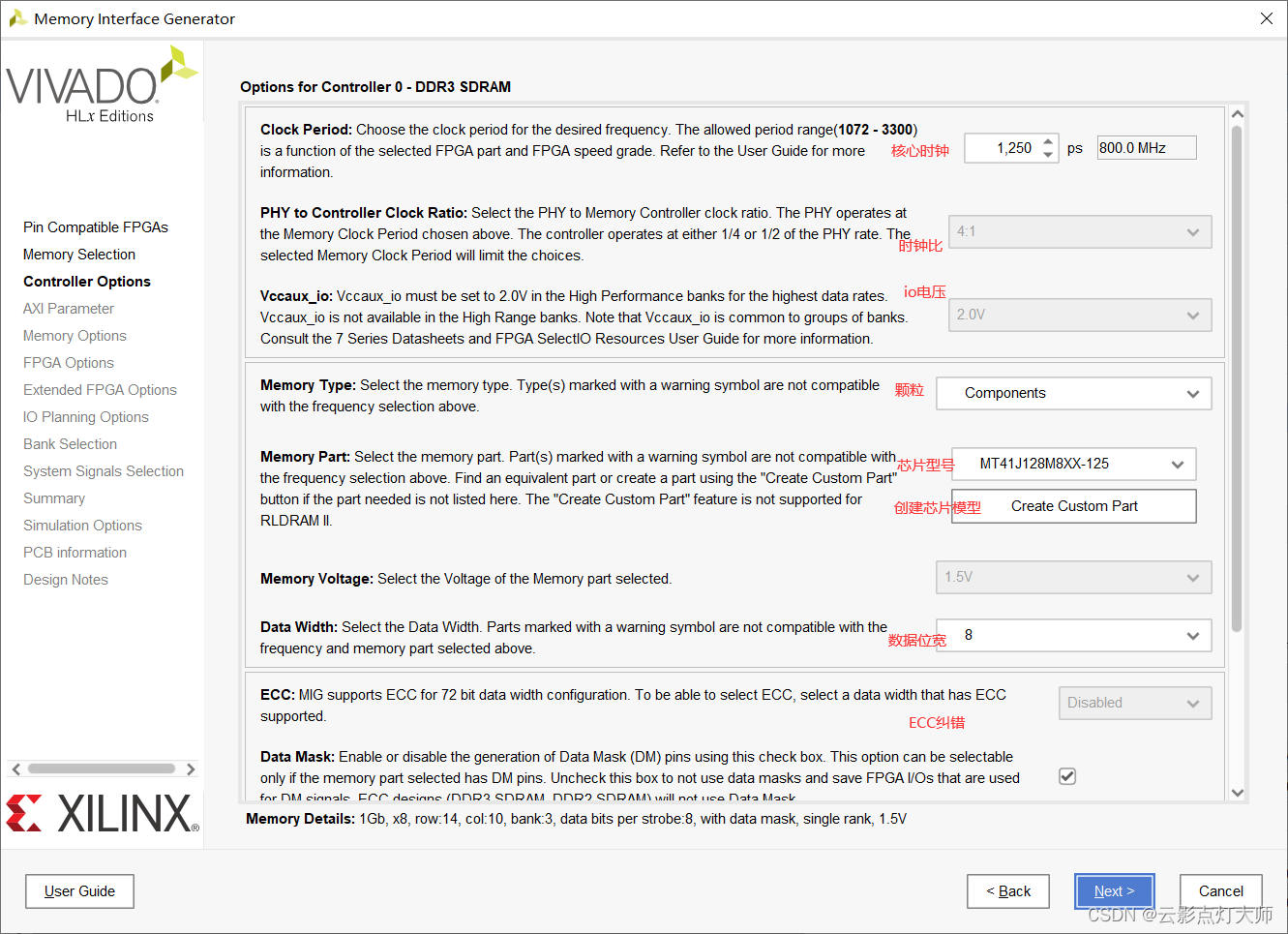

这里以镁光的DDR3芯片为例,不同系列的镁光芯片命名略有差异,基本大同小异,使用的是MT41J256M16HA-125。

MT——Micron的厂商名称。

41J——内存的类型。

256M16——内存颗粒容量为256M*16bits。

HA——封装方式。

-125——速度等级1600MHz,其tCK参数1.25ns,CL为11ns。

我们通过 Configuration,Package,Speed..等 DDR3的命名可知道 DDR3的容量,封装,这度等级等信息。

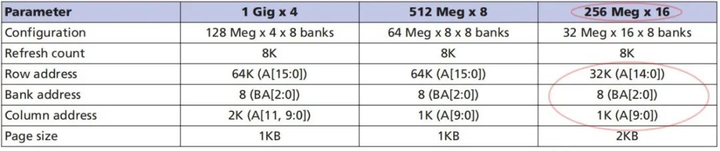

通过以上信息我们即可知道 DDR3的内存容量,Row,Column和 Bank的地址位宽。

更多的信息,请查看官方芯片手册。

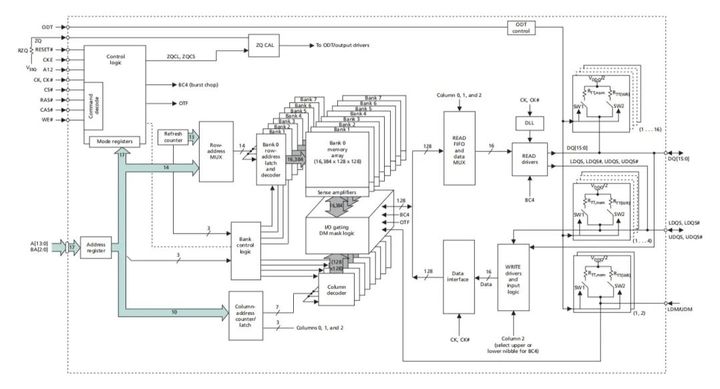

三、DDR3芯片基本结构

四、DDR 引脚说明

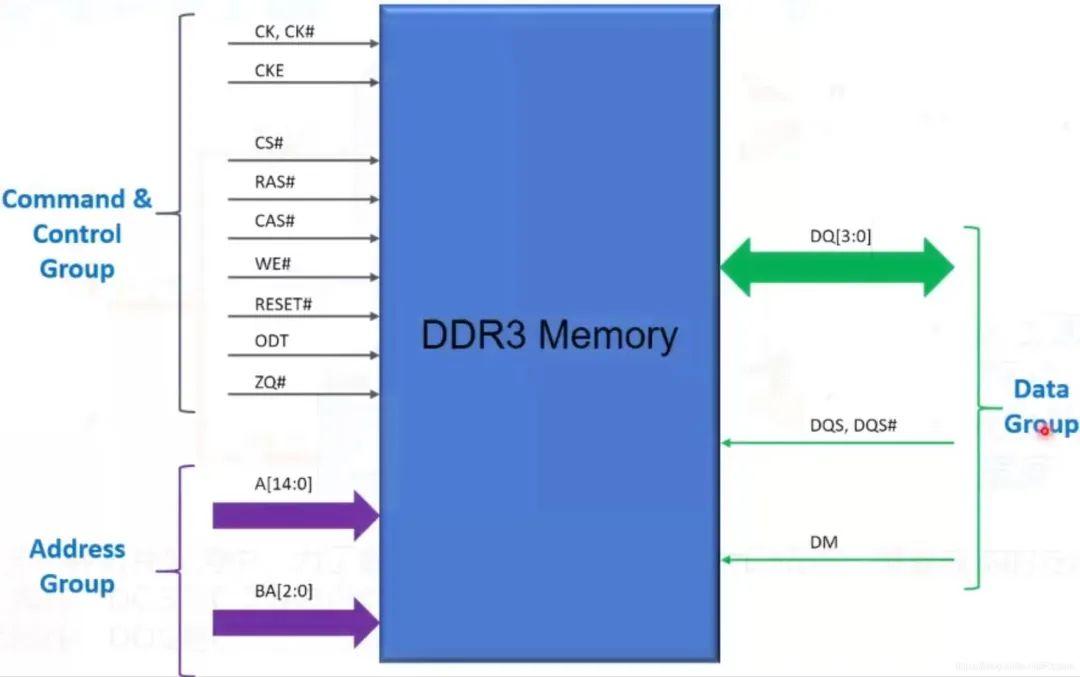

DDR3不同的功能引脚有不同的要求,可划分为:控制总线、地址总线、数据总线、电源与参考电压。

1、控制总总线

ODT:片上终端使能,ODT使能和禁止片内终端电阻。

ZQ:输出驱动较准的外部参考引脚,应外接一个RZQ电阻到VSSQ,一般接到地。

RESET:芯片复位引脚,低电平有效。

CKE:时钟使能引脚。

A12:A12为地址引脚,叫做BC引脚,有另外一个功能,A12会在READ和WRITE命令期间被采样,决定burst chop是否会被执行。

CK,CK#:时钟信号线,DDR3的时钟线是差分时钟线,控制信号和地址信号都会在CK的上升沿和CK#的下降沿交叉处采集。

CS#:片选信号,低电平有效。

RAS#:行地址选通信号。

CAS#:列地址选通信号。

WE#:写使能信号。

2、地址线

A[14:0]:15根行地址线A0~A14和10根列地址线A0~A9,行地址线和列地址线进行复用。

BA[2:0]:BA0~BA2为Bank的选择线,由2^3=8,可以总共有8个Bank。

8个Bank区域,DDR3一般有8个Bank区域。

3、数据总线

DQ[15:0]:DQ0~DQ15为16根数据线,该DDR3L的宽度为16位。

LDQS,LDQS#:数据选通引脚,对应低字节DQ0~DQ7,读的时候是输出,写的时候为输入;

UDQS,UDQS#:数据选通引脚,对应高字节DQ8~DQ15,读的时候是输出,写的时候为输入。 LDM/UDM:写数据输入屏蔽引脚。

五、DDR关键时间参数

1、传输速率

比如1066MT/S、1600MT/S等,这个参数决定了DDR的最高数据传输速率。

2、tRCD

tRCD的全称为RAS-to-CAS Delay,行寻址到列寻址之间的延迟。

DDR的寻址流程为先输入Bank地址和行地址,再输入列地址,确定最终要寻址的存储单元,该命令叫"行激活"。

在行激活到读写命令发出的这段时间时隔就是tRCD。

3、CL

CL(CAS Latency)即列地址选通潜伏期,当列地址发出以后就会触发数据传输,从数据从存储单元到内存芯片IO接口上需要的这一段时间。

4、AL

AL(Additive Latency)参数是为了保证足够的延迟潜伏期,单位为时钟周期,AL+CL组成了RL(Read Latency)。

5、tRC

tRC是两个ACTIVE命令,或者ACTIVE命令到REFRESH命令之前的周期,DDR的数据手册会给出该值。

6、tRAS

tRAS是ACTIVE命令到PRECHARGE命令之间的最小时间。

本文将不断定期更新中,码字不易,点⭐️赞,收⭐️藏一下,不走丢哦

本文由FPGA入门到精通原创,有任何问题,都可以在评论区和我交流哦

您的支持是我持续创作的最大动力!如果本文对您有帮助,请给一个鼓励,谢谢。