(1)BCD8421码:十进制数字转换成BCD8421码的方法

- 补零:你需要显示多少位数字,就在前面补上四倍的位宽。比如你要显示一个十进制8位的数字,就在前面补上8*4=32个零。

- 判断:判断补零部分显示的十进制数字,每位是否大于4,如果大于,则执行加3的操作。

- 判断完成后,向左移位一位。

- 最终位移次数与十进制数字位宽相同

(2)Verilog代码实现:

(3)仿真代码:

`timescale 1ns/1ns

module BCD_8421_32_tb;

reg clk ;

reg [31:0] data ;

reg reset_n ;

wire [3:0] unit ;

wire [3:0] ten ;

wire [3:0] hun ;

wire [3:0] tho ;

wire [3:0] t_tho ;

wire [3:0] h_tho ;

wire [3:0] o_tho ;

wire [3:0] t_o_tho ;

initial clk = 1'd1 ;

always #10 clk= ~clk ;

initial begin

reset_n <= 1'd0;

#15;

reset_n <= 1'd1;

data <= 32'd1234_5678;

#30000;

data <= 32'd9874_5612;

#30000;

$stop;

end

BCD_8421_32 BCD_8421_32_inst

(

.clk (clk ),

.data (data ),

.reset_n (reset_n ),

.unit (unit ),

.ten (ten ),

.hun (hun ),

.tho (tho ),

.t_tho (t_tho ),

.h_tho (h_tho ),

.o_tho (o_tho ),

.t_o_tho (t_o_tho )

);

endmodule

(4)仿真波形:

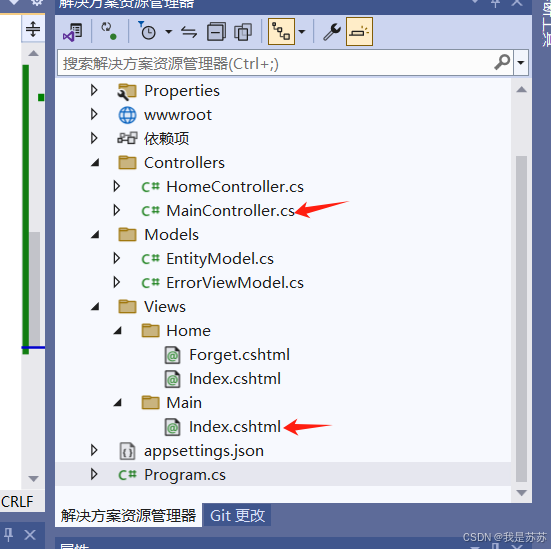

(5)顶层设计:

module freq_meter_top

(

input clk ,

input reset_n ,

input clk_test ,

output DIO ,

output SCLK ,

output RCLK

);

wire [31:0] freq ;

wire [31:0] data ;

wire [3:0] unit ;

wire [3:0] ten ;

wire [3:0] hun ;

wire [3:0] tho ;

wire [3:0] t_tho ;

wire [3:0] h_tho ;

wire [3:0] o_tho ;

wire [3:0] t_o_tho ;

freq_meter_calc freq_meter_calc_inst0

(

.clk (clk ) ,

.reset_n (reset_n ) ,

.clk_test (clk_test) ,

.freq (freq )

);

BCD_8421_32 BCD_8421_32_inst0

(

.clk (clk ),

.data (freq ),

.reset_n (reset_n ),

.unit (unit ),

.ten (ten ),

.hun (hun ),

.tho (tho ),

.t_tho (t_tho ),

.h_tho (h_tho ),

.o_tho (o_tho ),

.t_o_tho (t_o_tho )

);

assign data = {t_o_tho,o_tho,h_tho,t_tho,tho,hun,ten,unit};

hex_top hex_top_inst

(

.clk (clk ),

.reset_n (reset_n ),

.data (data ),

.DIO (DIO ),

.SCLK (SCLK ),

.RCLK (RCLK )

);

endmodule

(6)顶层仿真代码:

`timescale 1ns/1ns

module freq_meter_top_tb;

reg clk ;

reg reset_n ;

reg clk_test ;

wire DIO ;

wire SCLK ;

wire RCLK ;

initial clk = 1'd1;

always#10 clk = ~clk;

initial clk_test = 1'd1;

always#100 clk_test = ~clk_test;

initial begin

reset_n <= 1'd0;

#15;

reset_n <= 1'd1;

#2_000_000;

$stop;

end

freq_meter_top freq_meter_top_inst

(

.clk (clk ),

.reset_n (reset_n ),

.clk_test (clk_test),

.DIO (DIO ),

.SCLK (SCLK ),

.RCLK (RCLK )

);

defparam freq_meter_top_inst.freq_meter_calc_inst0.MCNT0 = 27'd74_999;

defparam freq_meter_top_inst.freq_meter_calc_inst0.MCNT1 = 27'd12_499;

endmodule

(7)仿真波形:

(8)引脚分配:

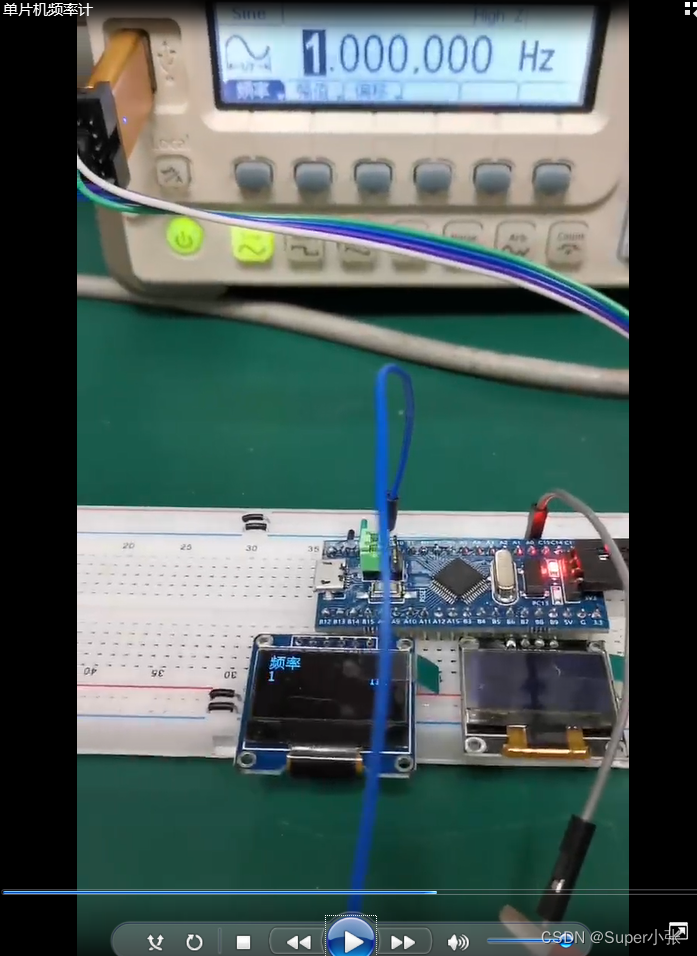

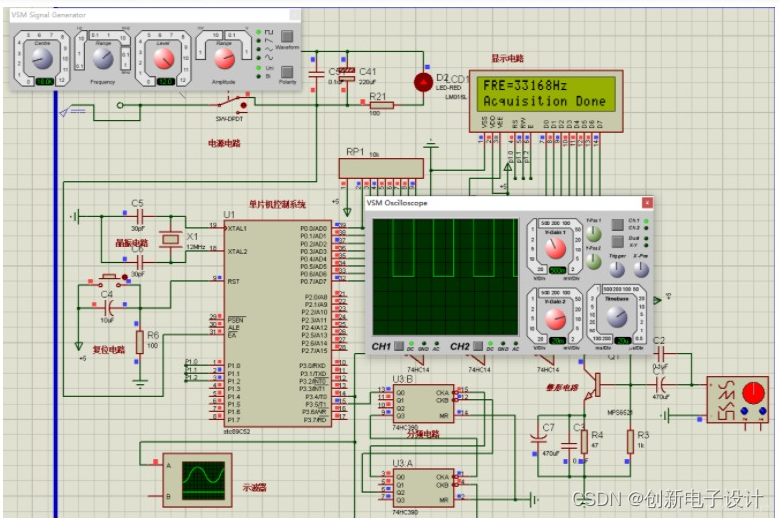

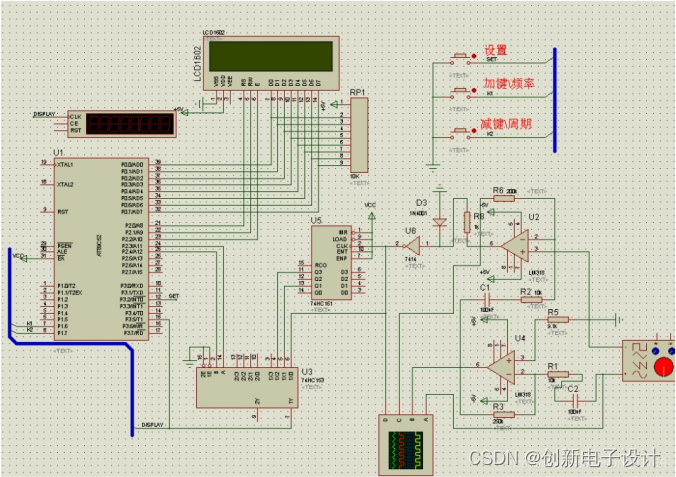

(9)实验现象: