近日,全球半导体行业的标准制定权威机构JEDEC发布了下一代高带宽内存(HBM)技术——HBM4的初步规范,此举预示着内存巨头与AI芯片企业即将围绕新一代高性能存储解决方案展开激烈竞争。此消息来源于JEDEC的官方新闻稿及科技资讯网站Wccftech的报道。

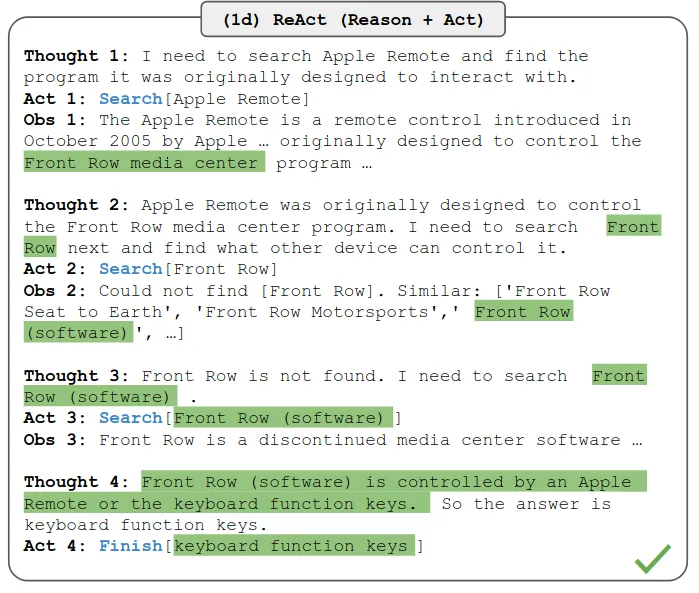

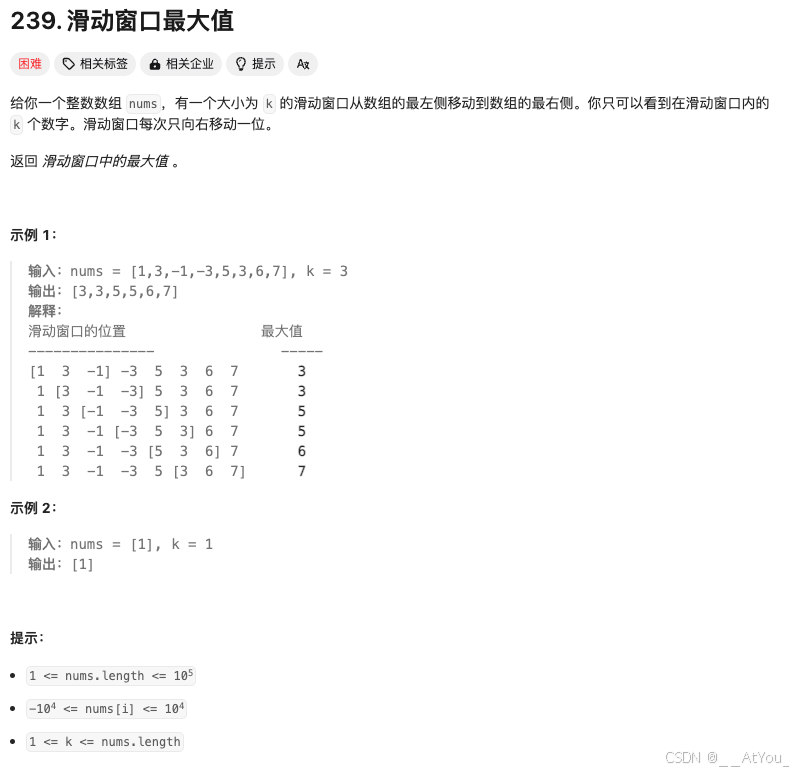

HBM4的设计目标在于进一步提升数据处理速度,同时保持高带宽、低功耗和单位面积或堆叠的高容量等关键特性,这对于处理大型数据集和执行复杂计算的应用至关重要,如生成式人工智能、高性能计算、高端显卡及服务器等领域。相较于前代HBM3,HBM4的每堆栈通道数量翻倍,意味着更高的空间利用率和显著增强的性能表现。同时,为了确保兼容性,新标准允许单一控制器同时支持HBM3与HBM4。

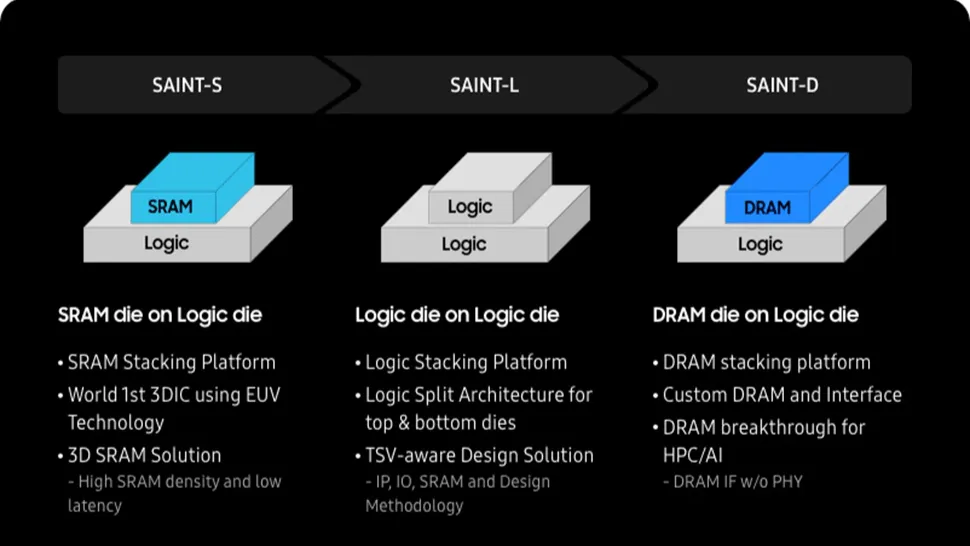

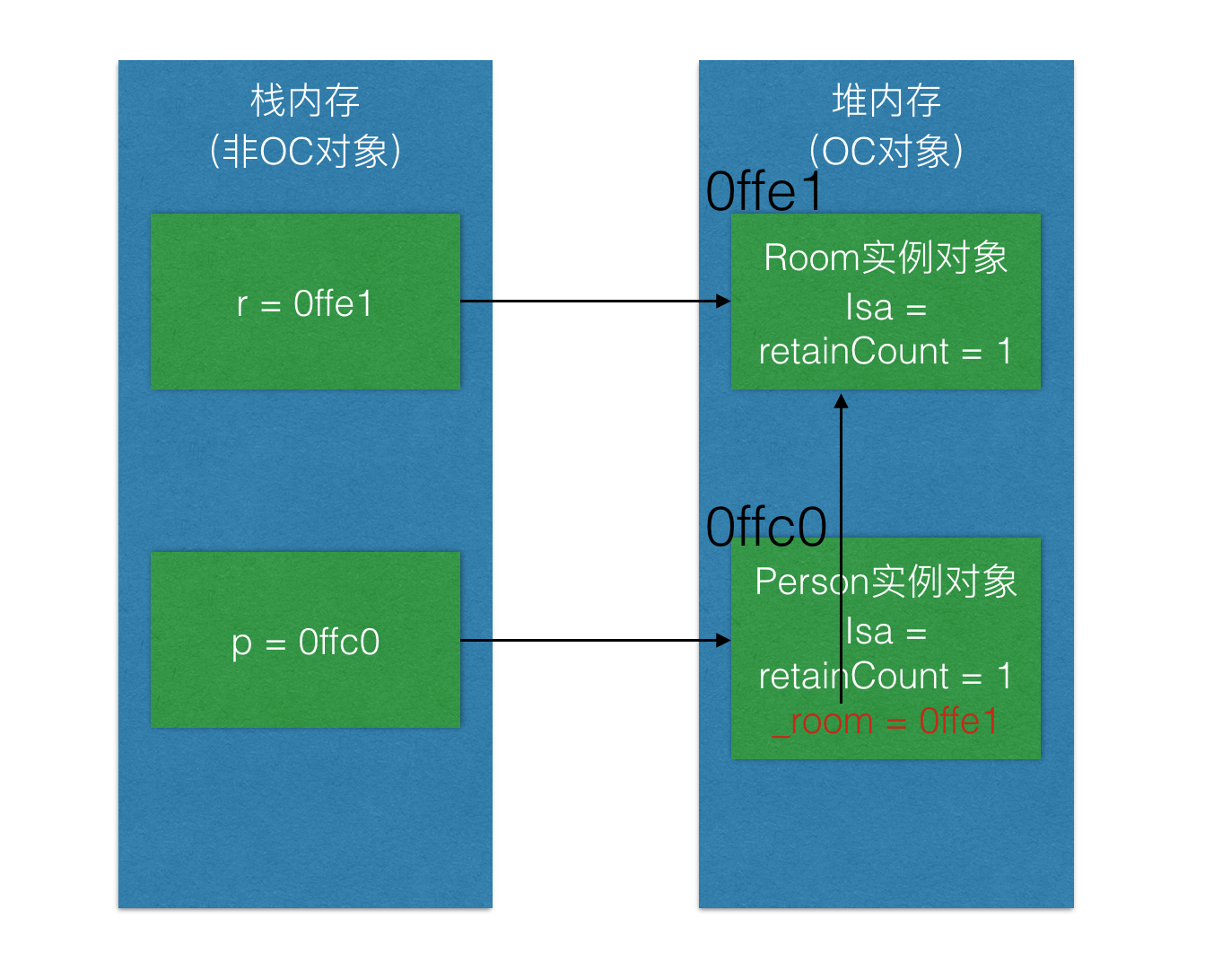

初步规格透露,HBM4将提供24Gb和32Gb的存储层,支持4至16层的硅通孔(TSV)堆栈,初期确定的速度等级可达6.4Gbps,且正在讨论更高频率的可能性。尽管如此,JEDEC尚未明确说明HBM4如何将存储器和逻辑半导体集成在一个封装中,这是业界目前亟待解决的重大技术挑战之一。

产业动态方面,NVIDIA于6月初宣布其预计2026年发布的下一代Rubin GPU将搭载8颗HBM4芯片,而Rubin Ultra GPU则配置12颗HBM4,展现了对HBM4技术的强烈信心。内存制造商的规划亦与之相匹配,三星据传正在开发单堆栈容量达48GB的HBM4大容量存储器,预计2025年投入生产。另一方面,HBM市场领头羊SK海力士与台积电合作,计划于2026年开始大规模生产HBM4。而美光也透露了其名为HBM Next的下一代HBM产品,预期提供36GB至64GB的不同容量配置,为市场提供更多选择。

综上所述,HBM4的发布标志着内存技术的又一次重大飞跃,虽然技术实现上仍面临内存堆叠的挑战,但以混合键合技术为代表的创新解决方案被视为突破的关键。随着主要玩家的积极布局,HBM4有望在未来的高性能计算和数据中心领域发挥重要作用。