目录

简介

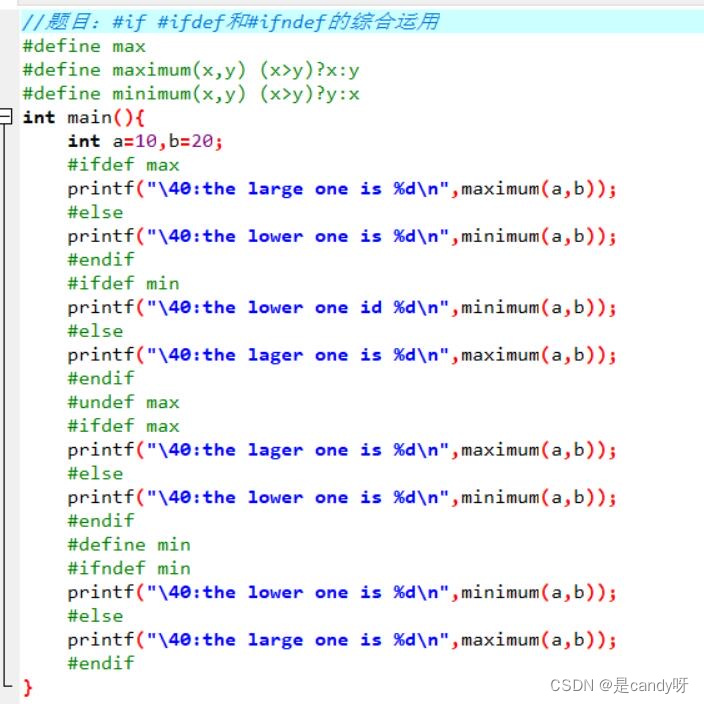

在 Verilog 硬件描述语言中,ifdef 是一种条件编译指令,允许根据宏定义的有无来包含或排除代码块。这一特性对于多平台设计、调试、性能优化等场景非常有用。Verilog-2001 和 SystemVerilog 在条件编译方面有所不同。

Verilog-2001 中的 ifdef

在传统的 Verilog-2001 中,ifdef 用于检查宏是否被定义。如果定义了指定的宏,则编译器会包含 ifdef 之后的代码块,直到匹配的 endif。Verilog-2001 中没有 elsif 或 else 预处理指令。

基本语法

`ifdef MACRO_NAME

// 当 MACRO_NAME 被定义时执行的代码

...

`endif示例 1:Verilog-2001 风格

`define USE_FEATURE_X

module feature_module(

input wire in,

output wire out

);

`ifdef USE_FEATURE_X

// 特定功能的实现代码

assign out = in ^ 1'b1; // 示例:取反操作

`else

// 通用功能的实现代码

assign out = in;

`endif

endmoduleSystemVerilog 中的 ifdef

SystemVerilog 扩展了条件编译指令,包括 ifdef、elsif、else 和 endif,提供了类似于程序语言中的条件编译能力。

基本语法

`ifdef MACRO_NAME_1

// 当 MACRO_NAME_1 被定义时执行的代码

...

`elsif MACRO_NAME_2

// 当 MACRO_NAME_1 未定义且 MACRO_NAME_2 被定义时执行的代码

...

`else

// 当上述宏都未定义时执行的代码

...

`endif示例 2:SystemVerilog 风格

`define OPTIMIZE_FOR_SPEED

module optimized_adder(

input wire [7:0] a,

input wire [7:0] b,

output wire [8:0] sum

);

`ifdef OPTIMIZE_FOR_SPEED

// 优化速度的加法器实现

always @(a or b) sum = a + b;

`elsif OPTIMIZE_FOR_AREA

// 优化面积的加法器实现

always @(a or b) sum = a + b; // 这里仅为示例,实际实现可能不同

`else

// 默认的加法器实现

always @(a or b) sum = a + b; // 标准实现

`endif

endmodule示例 3:调试与发布配置

`define DEBUG

`define RELEASE

module processor(

input wire clk,

input wire reset,

output reg [31:0] data

);

`ifdef DEBUG

initial begin

$display("Debug mode is enabled.");

end

`elsif RELEASE

initial begin

$display("Release mode is enabled.");

end

`else

initial begin

$display("Undefined mode.");

end

`endif

// 处理器的主要逻辑...

endmodule注意事项

- 确保您的开发环境和编译器支持 SystemVerilog,以便使用扩展的条件编译指令。

- 条件编译指令可以提高代码的灵活性,但过度使用可能导致代码难以理解和维护。

- 在团队项目中,明确宏定义的规则和使用方式,以保持代码的一致性。

通过掌握 ifdef 及其相关指令的用法,无论是在 Verilog-2001 还是 SystemVerilog 中,您都可以更有效地控制硬件设计的编译过程。