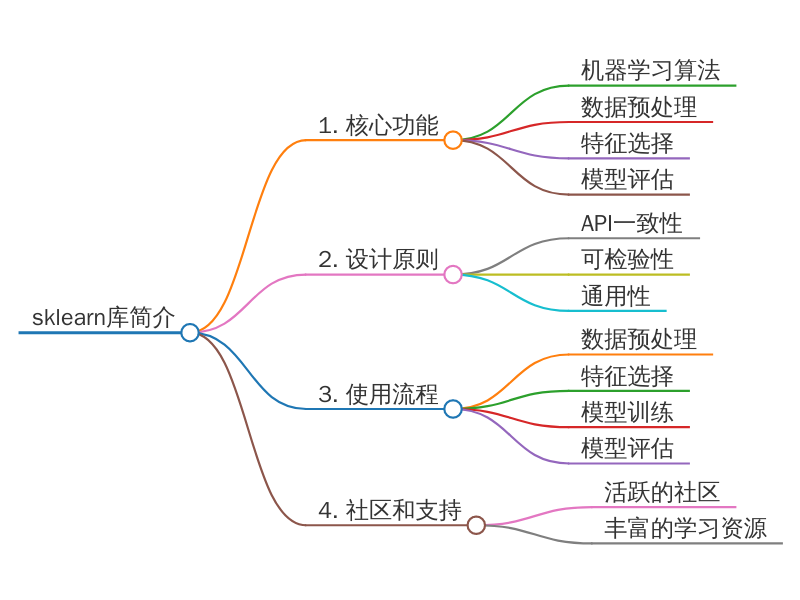

文章目录

由于芯片内部是一个黑盒子,在外部难以控制。因此将芯片中的所应用的普通寄存器替换成带有扫描功能的扫描寄存器,首尾相连成串,从而可以实现附加的测试功能。scan 过程就是在scan的shift mode(scan enable=1)下,测试机台将test pattern load到scan chain上(slow clk),然后在fast clk下进行launch和capture(AC测试)或在ate_clk(slow clk)下进行launch和capture(DC测试)。

function mode

function mode为最常见的功能模式,即标准时序约束模式。

对于function mode, case设置如下(示例):

set_case_analysis 0 [get_ports PIN_SCNTEST]

set_case_analysis 0 [get_ports PIN_SCN]

clock为function clock, datapath为function path。

scan mode

Scan mode主要包括scan-shift, scan-cpature和at-speed mode。

scan-shift mode

当scan enable端接1,扫描寄存器工作在scan shift模式,寄存器的输出Q是直接连接下一级的SI,中间没有其他组合逻辑。通常这个模式下的时钟频率都很慢,一般就几十MHz。在shift阶段使用测试机提供的慢速时钟,将测试向量‘0/1’shift到对应的flip-flop,如下图所示:

对于scan-shift mode, case设置如下(示例):

set_case_analysis 1 [get_ports PIN_SCNTEST]

set_case_analysis 1 [get_ports PIN_SCN]

clock为slow scan clock, datapath为scan path。需要注意的是在scan-shift mode所有的scan clocks是同步的,因为即使scan clock不同的scan chain会通过lockup latch穿到一起。

scan-capture mode(DC capture)

Capture mode通常分为低速和高速模式,分别对应DC capture和AC capture。 Capture模式下,scan enable信号接0,扫描寄存器工作在正常模式下,这时候开始检查function上的pin连接。 低速DC capture也就是我们经常说的Stuck-at模式,主要检查我们平时常见的stuck-at 0/1错误。比如下图中的 inverter A端如果被接到了VSS端的话,就是一个stuck at 1的fault。

对于scan-capture mode, case设置如下(示例):

set_case_analysis 1 [get_ports PIN_SCNTEST]

set_case_analysis 0 [get_ports PIN_SCN]

clock为slow scan clock, datapath为function path,主要检查电路的功能问题。在scan-capture mode所有的scan clocks是异步的。

at-speed mode(AC capture)

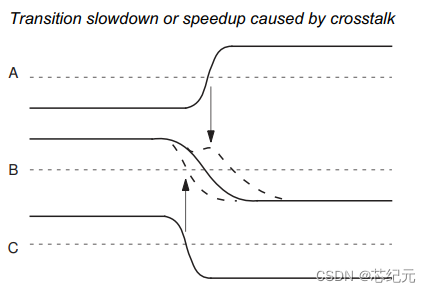

AC capture也被称为At-speed Structural Test(ASST),是一种高速测试模式,主要测试芯片中的延迟故障,即transition。随着半导体制造工艺的不断发展,片上器件的几何尺寸越来越小。此时,由于制造工艺异常,材料纯度不够,环境杂质等因素影响所造成的随机缺陷,导致电路中某些信号transition time变长,如果这种变化造成关键路径上的延迟不满足最大延迟要求,那么整个电路就不能工作在正常频率下。我们称这种故障为延迟故障。如下图的inverter,如果它下降的transition time延迟,就会导致它整个propagation delay超出限定的范围。

at-speed测试不再像stuck-at测试那样由测试机提供测试时钟,而是使用芯片内部的高速时钟,这样需要加入专门的电路(OCC-on chip clock)来支持。

对于at-speed mode, case设置如下(示例):

set_case_analysis 1 [get_ports PIN_SCNTEST]

set_case_analysis 0 [get_ports PIN_SCN]

clock为fast scan clock, datapath为function path,主要检查电路的时序问题。 可以看到scan-capture mode和at-speed mode的set_case_analysis设置是相同的,但是他们的scan clock是不同的,一个是slow clock,另一个是fast clock,区别在于写sdc的时候clock的定义不同。

At-speed测试是面向电路内部引入延迟的故障,一般电路都工作在一定频率下,如果因为一个故障导致0→1或者1→0的翻转无法在一定的时间内完成,此芯片就失效了。与传统的基于stuck-at故障模型的静态测试方法比较,at-speed测试生成的测试向量分为两部分。第一部分是在一个组合逻辑的输入端发射(1aunch)一个0—1或1—0的翻转,第二个部分要捕获(capture)组合逻辑的输出端响应。如果在指定的时间周期内capture的响应正确,那么说明电路没有at-speed故障。

现在高性能超大规模的芯片的故障也越来越多地表现为延迟故障,而不是传统的stuck-at 故障。因此这个ASST模式也是很重要的,通常会单独作为一个模式(at-speed mode)定义在MCMM环境中。