FPGA(Field Programmable Gate Array)即现场可编程门阵列,是一种在制造完成后可以由用户根据自己的需求进行编程配置的集成电路。

逻辑单元(Logic Cell):

逻辑单元堪称 FPGA 架构的基石,其设计的精妙与性能的优劣直接决定了 FPGA 所能承载的逻辑复杂性与运算速度的上限。

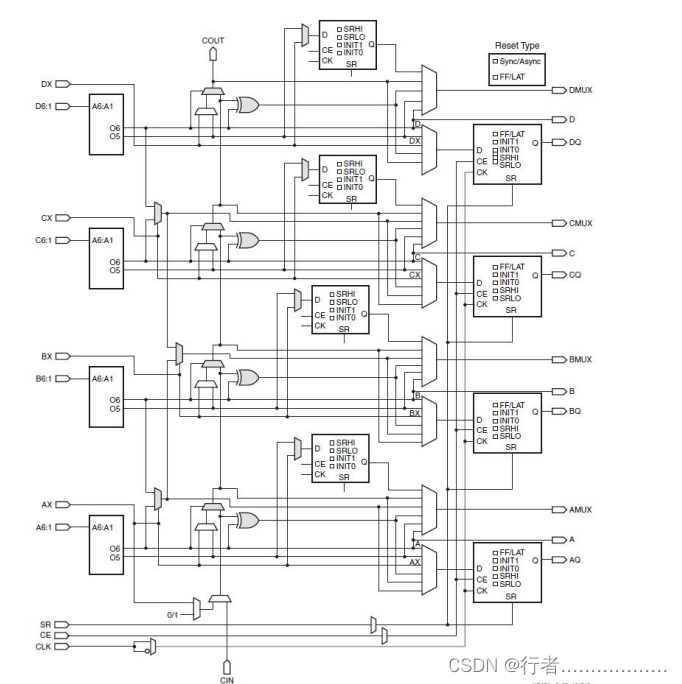

从微观结构剖析,逻辑单元通常由组合逻辑部分与时序逻辑部分无缝融合而成。组合逻辑部分的核心实现方式——查找表(LUT),以经典的 4 输入查找表为例,其内部精心布置了 16 个存储单元,每个单元犹如一位忠实的记录者,能够存储 1 位宝贵的数据。当输入信号宛如使者般前来,它们便充当地址线,精准地选取对应的存储单元,而存储单元中所蕴含的值则顺理成章地成为输出结果。这种设计的巧妙之处在于,通过对这 16 个存储单元进行精心的配置,它能够像一位全能的魔法师,变幻出多达 16 种不同的 4 输入布尔逻辑函数。无论是基础的与门、或门、异或门等逻辑运算,还是更为复杂的加法器、比较器等功能,都能在其掌控之中轻松实现。

而时序逻辑部分,通常由一个或多个寄存器构成,这些寄存器宛如时间的守护者,由触发器精心打造而成。它们能够在时钟信号那精准的节拍下,如同训练有素的士兵,迅速而准确地捕获输入数据,并将其稳稳地存储起来。寄存器的引入,为逻辑单元注入了处理时序相关操作的强大能力,使得数据能够在不同的时钟周期之间有序传递和暂存。

逻辑单元的数量和性能宛如两把衡量的标尺,直接影响着 FPGA 能够实现的逻辑复杂度和处理速度。数量的多寡,从理论层面决定了能够构建的逻辑电路的规模大小;性能的高低,例如查找表的转换速度如同闪电般迅速、寄存器的建立和保持时间如同秒表般精确等,都为支持更高频率的操作和更具挑战性的时序要求提供了坚实的保障。

在实际的 FPGA 设计战场上,多个逻辑单元通过错综复杂的布线资源相互连接,编织成一张庞大而精密的逻辑网络。不同的 FPGA 厂商,犹如身怀绝技的工匠,根据自身独特的技术专长和瞄准的目标应用领域,对逻辑单元的结构和功能进行独具匠心的优化和差异化设计。有的厂商可能侧重于提高查找表的灵活性和可配置性,以适应各种复杂多变的逻辑需求;有的则可能在寄存器的性能优化上苦下功夫,力求在高速处理和低功耗之间找到完美的平衡。

查找表(Look-Up Table,LUT):

查找表,作为实现组合逻辑功能的中流砥柱,在 FPGA 的神秘世界中扮演着不可或缺的角色。

深入探究其工作原理,以常见的 4 输入查找表为例,它的运作方式恰似一本预先精心编排好的“真值表”。当输入信号如勇敢的探险家般踏入查找表的领域,作为地址线的它们,经过地址译码的神奇魔法,相应存储单元中的值便如同宝藏般被揭示出来,成为最终的输出结果。这种方式所蕴含的灵活性和可配置性,仿佛一把万能钥匙,能够开启实现各种复杂逻辑功能的大门。

在现代 FPGA 设计的广袤天地中,查找表的规模和结构如同不断进化的生物,持续发展和优化。除了传统的 4 输入查找表,更多输入的查找表可能崭露头角,或者将多个较小的查找表巧妙组合,形成更为复杂和强大的结构,以迎合不同类型和规模的逻辑功能实现需求。这些变化不仅仅是数量上的增加,更是在性能、功耗和面积等多维度上的精心权衡和优化。

查找表的配置过程,通常在设计综合的关键阶段华丽上演。设计工具宛如智慧的军师,根据用户输入的逻辑描述,如同排兵布阵般,自动将其转化为对查找表存储内容的精确配置,从而巧妙地实现用户心中所想的逻辑功能。这一过程如同一场精密的舞蹈,每一个步伐都需要准确无误,才能展现出完美的逻辑之美。

此外,查找表的性能特征,如输入到输出的延迟、功耗等指标,宛如衡量其价值的金标准,成为 FPGA 整体性能评估中不可或缺的重要元素。每一个细微的改进和优化,都可能为整个系统带来性能的飞跃和效率的提升。

寄存器(Register):

寄存器,在 FPGA 的时序逻辑设计领域中,宛如定海神针般不可或缺,是确保数据稳定如磐和正确同步的关键所在。

寄存器通常由触发器精心构建而成,而触发器的世界丰富多彩,D 触发器、JK 触发器、T 触发器等各自展现着独特的魅力。在 FPGA 的广袤天地中,D 触发器因其简洁高效而备受青睐,成为最常见的选择。其工作原理犹如精准的时钟舞者,在时钟信号那精准的上升沿或下降沿,将输入数据(D 端)如珍宝般捕获,并稳定地存储到输出端(Q 端)。

寄存器的重要作用多如繁星,首先,它如坚固的堡垒,能够有效地守护数据的稳定性。在数字电路那充满变数的世界中,由于信号传输和处理的漫长旅程中可能遭遇各种干扰和不确定性的风暴,寄存器能够在每个时钟周期内,如同灯塔般提供一个确定、稳定的数据值,避免数据陷入混乱和错误的深渊。

其次,寄存器是不同模块之间数据传输的同步使者。在一个错综复杂的数字系统中,多个模块可能如同不同步的舞者,以各自独特的时钟频率或相位翩翩起舞。通过寄存器的巧妙运用,数据能够在正确的时钟边沿被接收和处理,如同指挥家手中的指挥棒,确保了整个系统的和谐与统一,避免了由于时钟偏差带来的数据错误和混乱。

此外,寄存器还是构建各种复杂时序逻辑电路的基石,如计数器、移位寄存器等精妙的设计。通过将多个寄存器按照特定的方式紧密连接和精确控制,能够实现对数据的计数、移位、存储等如同魔法般的操作,为系统赋予了丰富多样的功能和强大的处理能力。

寄存器的性能特性,如建立时间(Setup Time)、保持时间(Hold Time)和时钟到输出时间(Clock-to-Output Time)等,如同衡量其品质的精细刻度,对于整个 FPGA 系统的时序性能有着决定性的影响。建立时间如同起跑线上的准备指令,要求数据在时钟上升沿或下降沿之前必须稳定的最短时间;保持时间则是冲刺后的坚守,规定数据在时钟上升沿或下降沿之后必须保持稳定的最短时间;时钟到输出时间则是从时钟信号发出到寄存器输出有效数据的延迟,这每一个时间参数都需要被严格满足,如同工匠对每一个细节的精雕细琢,才能确保系统的可靠运行和卓越性能。

在 FPGA 设计的精细画布上,必须对寄存器的这些时序要求给予最严谨的关注和满足,如同艺术家对每一笔色彩的精准运用,以确保系统如同精心编排的交响乐,和谐、稳定且完美地运行。

布线资源(Routing Resources):

布线资源,如同 FPGA 内部的信息高速公路,是连接各个逻辑单元、寄存器和其他功能模块的物理桥梁,其质量和效率如同道路的平整度和通行能力,直接影响着 FPGA 设计的性能和实现的可能性。

从分类的角度审视,布线资源可以分为局部布线资源和全局布线资源这两大阵营。局部布线资源犹如城市中的小巷和街道,主要负责连接相邻的逻辑单元,提供短距离、低延迟的快速通道。这些局部布线通常由电阻和电容较小的线路构成,能够像闪电般实现快速的数据传输,特别适用于对时序要求如同针尖般精细的局部逻辑连接。

而全局布线资源则仿佛是跨越大陆的高速公路和铁路,能够实现跨越整个芯片的长距离信号传输。它们配备了强大的驱动能力和出色的信号完整性保障措施,如同坚强的卫士,确保信号在漫长的旅程中不会衰减或失真。全局布线资源常常被委以重任,用于连接分布在芯片不同角落的关键模块,如至关重要的时钟网络、全局控制信号等,确保整个系统的协调一致和稳定运行。

在实际的 FPGA 布线征程中,设计工具就如同智慧的交通规划师,需要根据设计的逻辑连接需求,像调配交通流量一样,合理分配和巧妙运用布线资源。这是一个充满挑战和复杂性的优化难题,需要综合考虑诸多关键因素,如布线的长度如同路程的远近、延迟如同行程的时间、拥塞情况如同道路的拥堵程度等等。

布线资源的管理和优化,如同城市交通规划的艺术,是 FPGA 设计中的关键环节和核心挑战。如果布线规划不合理,可能会引发一系列问题,如信号延迟如同交通堵塞般过大、时序违规如同交通规则被打破、布线拥塞如同道路瘫痪等,从而给整个设计的性能和功能带来严重的影响,如同交通混乱对城市运转造成的阻碍。为了提升布线的效率和质量,现代的 FPGA 设计工具纷纷施展先进的算法和技术魔法,如基于时序驱动的布线策略如同智能导航、多层布线策略如同立体交通网络等,力求在布线的世界中创造出高效、稳定和可靠的连接通道。

时钟网络(Clock Network):

时钟网络,在 FPGA 的浩瀚宇宙中,宛如精准的心跳节拍器,是确保整个系统同步运作和稳定航行的核心基石。

时钟网络通常由一系列精心设计的缓冲器、驱动器和专用的时钟布线共同构建而成。其神圣使命是将时钟信号从源头(如外部晶振或内部时钟生成模块)精确、均匀且稳定地分发到各个功能模块,如同生命的血液流向身体的每一个细胞。

为了保证时钟信号的高质量传输,时钟网络需要具备一系列如同黄金标准的关键特性。首先,低时钟偏差如同天平的精准平衡,至关重要。时钟偏差,如同不同位置的模块接收到时钟信号的时间差异,必须被严格控制在最小范围内。为了实现这一目标,时钟网络常常采用树状结构或网格结构等精妙的拓扑布局,如同精心设计的物流网络,确保时钟信号能够以尽可能相等的路径长度和延迟到达各个模块,如同阳光均匀地洒在大地上。

其次,低时钟抖动如同心脏跳动的稳定节奏,必不可少。时钟抖动,即时钟边沿变化在时间上的不确定性,必须被有效地抑制。高稳定性的时钟网络如同坚固的堡垒,能够为时钟边沿的变化提供稳定和可预测的环境,从而最大程度地减少对时序逻辑的不利影响,确保系统的稳定运行。

此外,时钟网络还需要具备高驱动能力,如同强大的引擎,以能够驱动大量的负载。在 FPGA 的广袤世界中,可能有成千上万个逻辑单元和寄存器如同嗷嗷待哺的孩子,同时渴望接收时钟信号。因此,时钟网络必须拥有足够的强度和功率,如同源源不断的能源供应,来确保时钟信号在整个芯片上的完整性和一致性,使其如同精确的指挥棒,引导着每一个模块的同步运作。

为了实现这些苛刻的性能要求,FPGA 厂商如同技艺精湛的工匠,通常会采用先进的工艺技术和电路设计方法来精心优化时钟网络。例如,运用低功耗、高性能的缓冲器和驱动器,如同选用精良的零部件;采用特殊的布线材料和层来降低电阻和电容,如同打造优质的传输通道;以及运用时钟树综合和优化算法等,如同运用智慧的策略规划,共同铸就一个高效、稳定且可靠的时钟网络,为 FPGA 系统的卓越性能奠定坚实的基础。

IP 核(Intellectual Property Core):

IP 核,作为预先精心设计和严格验证的具有特定功能的模块,在 FPGA 设计的广阔天地中发挥着不可或缺的作用,如同璀璨的明珠,极大地提升了设计的效率和可靠性。

从实现方式和特性的角度划分,IP 核可以分为软核、硬核和固核这三种各具特色的类型。

软核,通常以硬件描述语言(如 VHDL 或 Verilog)形式呈现的源代码,宛如一张充满潜力的蓝图。用户在获得这张蓝图后,拥有如同建筑师般的自由度,可以根据自身的独特需求对其进行修改和优化,但同时也肩负着更多的设计和验证工作。软核的魅力在于其高度的灵活性和可定制性,如同一块未经雕琢的璞玉,等待着用户的巧手将其打磨成理想的形状。然而,由于需要在目标 FPGA 上进行综合和实现,其性能和面积的优化程度相对较低,如同在探索的道路上还需要不断地磨砺和完善。

硬核,则是在芯片制造的神秘过程中直接实现的物理模块,犹如一座坚不可摧的城堡,具有最高的性能和最小的面积。然而,这座城堡的结构已经固定,硬核的灵活性较差,用户通常只能如同访客般按照给定的接口和功能进行使用,无法对其内部结构进行大幅度的改动。

固核,如同介于软核和硬核之间的桥梁,通常以网表(Netlist)的形式展现。用户在这座桥上可以进行一定程度的参数配置,但无法像在软核的广阔天地中那样进行深入的结构修改。固核在提供一定灵活性的同时,也具备相对较好的性能和面积优化,如同在平衡木上找到了一个恰到好处的支点。

IP 核的功能领域犹如一片广阔的星空,从基本的数字逻辑模块,如加法器、乘法器等闪烁的星辰,到复杂的系统级功能,如数字信号处理算法(如 FFT、FIR 滤波器)、通信协议栈(如以太网、PCI Express)、存储器控制器(如 DDR 控制器)等璀璨的星系,无所不包。这些预先设计和验证完善的模块,如同夜空中的北斗星,为 FPGA 设计指明了方向,大大缩短了 FPGA 设计的开发周期,降低了设计风险的迷雾,并提升了设计的可靠性,如同在未知的海洋中找到了可靠的灯塔。

在使用 IP 核的旅程中,用户需要如同精明的航海家,根据自己的设计需求精准地选择合适的类型和功能,并严格遵循相应的使用规则和授权协议。同时,还需要对 IP 核与整个设计的接口和集成进行细致入微的规划和验证,如同精心拼接航海图的每一个碎片,以确保系统的性能和功能如同预期的目标那样闪耀光芒,引领设计的船只顺利抵达成功的彼岸。

配置文件(Configuration File):

配置文件,作为 FPGA 实现特定功能的详细指令宝典,其内容的精准性和完整性如同密码锁的每一个数字,决定了 FPGA 芯片内部资源的配置方式和工作状态的优劣。

从格式的角度审视,配置文件通常以多种特定的形式呈现,常见的包括二进制、十六进制或经过精心压缩和编码的独特格式。这些格式的选择,宛如精心挑选的工具,旨在优化文件的存储大小,如同压缩行李以节省空间,同时保证数据的准确性和可靠性,如同守护珍贵的宝藏不被丝毫损坏。

在生成配置文件的神秘过程中,设计工具如同智慧的魔法师,会对用户的设计描述进行全面而深入的综合、精细入微的优化和精确无误的映射,将逻辑单元的连接关系、查找表的配置细节、寄存器的初始值设定、布线资源的分配策略等诸多关键内容,转化为一系列犹如繁星般的位流数据。

当踏上将设计下载到 FPGA 的征程时,配置文件通过专门的编程接口(如 JTAG 接口、SPI 接口等),如同传递密信的使者,被加载到芯片内部的配置存储器中。这一配置存储器通常具有非易失性的特质,如同永恒的记忆,确保在断电的黑暗时刻,配置信息不会如流星般消逝。

一旦配置文件成功入驻 FPGA ,芯片内部的逻辑资源将如同听从将军指令的士兵,按照配置文件中的精确指令进行连接和设置,从而使 FPGA 能够如同精准的机器,按照设计要求执行相应的复杂功能,展现出无与伦比的计算和处理能力。

配置文件的生成和下载过程,需要如同遵循古老法典般严格遵循 FPGA 厂商提供的规范和工具,以确保配置的成功和正确性,如同在钢丝上行走,不容丝毫差错。

资源利用率(Resource Utilization):

资源利用率,作为评估 FPGA 设计在芯片上资源消耗情况的精确标尺,对于设计的优化和芯片选型具有如同指南针般关键的指导意义。

常见的资源类型犹如璀璨星空中的繁星,包括逻辑单元的使用数量、查找表的占用率、寄存器的使用比例、布线资源的使用程度、Block RAM(块随机存储器)的占用量、DSP(数字信号处理)模块的使用情况等等。

对于逻辑单元的利用率,它如同反映设计复杂程度的镜子,直观地展现了设计中实际运用的逻辑功能与芯片所提供的逻辑单元总数之间的微妙比例。高逻辑单元利用率,可能暗示着设计如同复杂的迷宫,需要审慎考虑是否能够通过优化逻辑结构,如同梳理乱麻,或者采用更高效的算法,如同寻找捷径,来降低资源的消耗,从而提高设计的效率和经济性。

查找表的占用率,则直接映射了组合逻辑功能的实现方式和效率的高低。过高的查找表占用,可能如同警示灯般暗示设计中存在过于复杂的组合逻辑,或者需要思考是否可以通过资源复用现有逻辑、运用更高级的综合策略等手段,如同巧妙的战术调整,来进行优化和改进。

寄存器的使用比例,清晰地反映了时序逻辑在设计中的权重和地位。如果寄存器使用过多,可能需要像侦探般仔细检查是否存在不必要的时序逻辑,或者是否可以通过流水线等先进技术,如同引入高效的生产流水线,来提高系统的性能和效率。

布线资源的使用程度,是衡量设计布线复杂度和合理性的重要指标,如同地图上的道路拥堵情况。过高的布线资源利用率,可能导致布线拥塞,如同交通瘫痪,信号延迟增加,如同行程延误,以及时序违规等严重问题,需要重新评估布线策略,如同重新规划交通路线,或者对设计进行结构调整,如同重新布局城市规划,以确保信号传输的顺畅和系统的稳定运行。

Block RAM 的占用量,对于需要大量存储数据的设计而言,至关重要。如果 Block RAM 资源不足,可能需要像建筑师重新构思般优化数据存储结构、灵活运用分布式 RAM 或者果断选择具有更多 Block RAM 资源的 FPGA 芯片