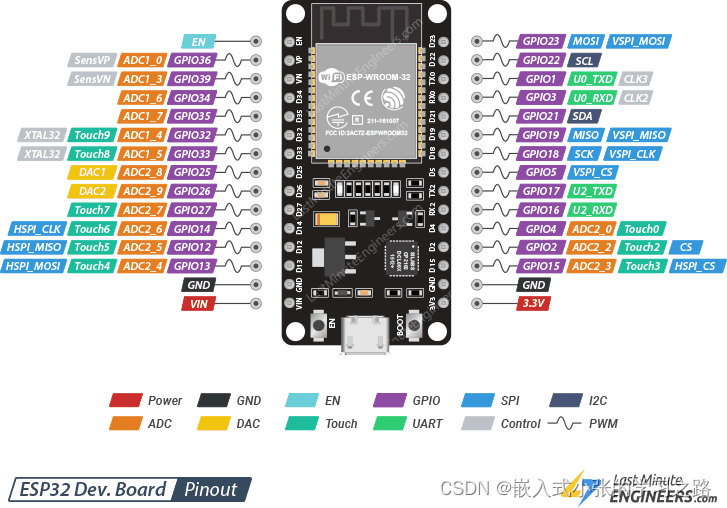

ESP32 I2S 接口

ESP32 有 2 个标准 I2S 接口。这 2 个接口可以以主机或从机模式,在全双工或半双工模式下工作,并且可被配置为 8/16/32/48/64-bit 的输入输出通道,支持频率从 10 kHz 到 40 MHz 的 BCK 时钟。当 1 个或 2 个 被配置为主机模式时,主机时钟可以输出到外部 DAC/CODEC。

2 个 I2S 接口都有专用的 DMA 控制器。支持 PDM 和 BT PCM 接口。

PDM可直接接入I2S,但只能接入I2S0。

用于串行立体声数据的输入输出,并行LCD 数据的输出,camera 并行数据的输入。

I2S第0通道接口

| 信号 | 管脚 |

|---|---|

| I2S0I_DATA_in0~15 | I2S除I2S_CLK,均支持映射(切换)到任意 GPIO 管脚 |

| I2S0O_BCK_in | |

| I2S0O_WS_in | |

| I2S0I_BCK_in | |

| I2S0I_WS_in | |

| I2S0I_H_SYNC | |

| I2S0I_V_SYNC | |

| I2S0I_H_ENABLE | |

| I2S0O_BCK_out | |

| I2S0O_WS_out | |

| I2S0I_BCK_out | |

| I2S0I_WS_out | |

| I2S0O_DATA_out0~23 |

I2S第1通道接口

| 信号 | 管脚 |

|---|---|

| I2S1I_DATA_in0~15 | I2S除I2S_CLK,均支持映射(切换)到任意 GPIO 管脚 |

| I2S1O_BCK_in | |

| I2S1O_WS_in | |

| I2S1I_BCK_in | |

| I2S1I_WS_in | |

| I2S1I_H_SYNC | |

| I2S1I_V_SYNC | |

| I2S1I_H_ENABLE | |

| I2S1O_BCK_out | |

| I2S1O_WS_out | |

| I2S1I_BCK_out | |

| I2S1I_WS_out | |

| I2S1O_DATA_out0~23 |

| 信号 | 管脚 |

|---|---|

| I2S0_CLK | 仅可通过GPIO0、U0RXD、或 U0TXD |

| I2S1_CLK | 仅可通过GPIO0、U0RXD、或 U0TXD |

注:I2S0_CLK 和 I2S1_CLK 仅可通过 IOMUX 映射至 GPIO0、U0RXD (GPIO3) 或U0TXD (GPIO1),选择 GPIO 功能CLK_OUT1、CLK_OUT2 或 CLK_OUT3。这个CLK是高速CLK,主要是用于RGB接口的LCD液晶显示屏。每组I2S的DATA有0-23个信号,用于RGB接口液晶显示屏时,可连接18位或24位的LCD液晶显示屏。

12.4 I2S 模式

ESP32 I2S 模块内置数据 A 律压缩/解压缩模块,用于对接收到的音频数据进行 A 律缩/解压缩操作。如果要使用 A 律缩/解压缩模块,需要将 I2S_CONF1_REG 寄存器的 RX_PCM_BYPASS 比特和 TX_PCM_BYPASS 比特清零。

12.4.1 支持的音频标准

I2S 模式下,BCK 为串行时钟;WS 为通道选择信号,用于表示左右声道的切换;SD 为串行数据信号,传输音频数据。WS 信号和 SD 信号在 BCK 的下降沿发生变化,并在 BCK 的上升沿采样 SD 信号。如果将寄存器I2S_CONF_REG 的 I2S_RX_RIGHT_FIRST 比特和 I2S_TX_RIGHT_FIRST 比特都置 1,表示 I2S 模块首先接收和发送的是右声道数据,否则为首先接收和发送的是左声道数据。

12.4.1.1 Philips 标准

如图 12-3 所示,在 Philips 标准下,在 BCK 的下降沿,WS 信号先于 SD 信号一个 BCK 时钟周期开始变化,即WS 信号从当前通道数据的第一个位之前的一个时钟开始有效,并在当前通道数据发送结束前一个 BCK 时钟周期变化。SD 信号线首先传输音频数据的最高有效位。如果分别将寄存器 I2S_CONF_REG 的I2S_RX_MSB_SHIFT 比特和 I2S_TX_MSB_SHIFT 比特置 1,I2S 模块接收数据和发送数据将使用 Philips 标准。

12.4.1.2 MSB 对齐标准

如图 12-4 所示,MSB 对齐标准下,在 BCK 下降沿,WS 信号和 SD 信号同时变化。WS 持续到当前通道数据发送结束,SD 信号线上首先传输音频数据的最高位。如果寄存器 I2S_CONF_REG 的 I2S_RX_MSB_SHIFT 比特和 I2S_TX_MSB_SHIFT 比特清零,则 I2S 模块接收数据和发送数据将使用 MSB 对齐标准。

12.4.1.3 PCM 标准

如图 12-5 所示,在 PCM 标准的短帧同步模式下,在 BCK 的下降沿,WS 信号先于 SD 信号一个 BCK 时钟周期开始变化,即 WS 信号从当前通道数据的第一个位之前的一个时钟开始有效,并持续 1 个 BCK 时钟周期。

SD 信号线上首先传输音频数据的最高位。如果将寄存器 I2S_CONF_REG 的 I2S_RX_SHORT_SYNC 比特和I2S_TX_SHORT_SYNC 比特置 1,那么 I2S 模块接收数据和发送数据将使用短帧同步模式。

![<span style='color:red;'>ESP</span><span style='color:red;'>32</span>入门六(读取<span style='color:red;'>引</span><span style='color:red;'>脚</span><span style='color:red;'>的</span>模拟信号[<span style='color:red;'>2</span>]:信号出现误差<span style='color:red;'>的</span>原因)](https://img-blog.csdnimg.cn/direct/ff1d1bec38594c2eb6a8c4309b892d65.png)

![[FreeRTOS 功能应用] 任务通知 功能应用](https://i-blog.csdnimg.cn/direct/d53ae15c952b41cba1cb4c95d5f7839f.png)