目录

0 引言

PCI Express Base Specification 5.0的电气规范中,关键技术要点如下:

1. 支持2.5、5.0、8.0、16.0和32.0 GT/s的数据速率;

2. 支持公共的和分立的参考时钟体系结构;

3. 支持时钟扩频技术(SSC);

4. 支持低电压摆幅(Voltage Swing)的低功耗模式;

5. 在8.0、16.0和32.0 GT/s时的眼图闭合下,支持自适应发射机均衡和参考接收机均衡。

本文就上述的技术要点进行了串联梳理,旨在增加相关技术指标的可读性,并使之更好地展现给设计者。

1 参考时钟--Refclk

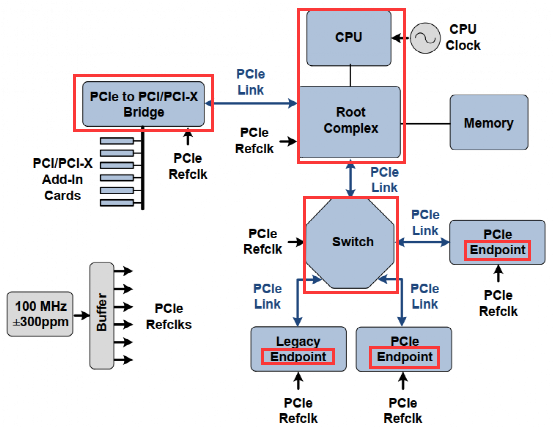

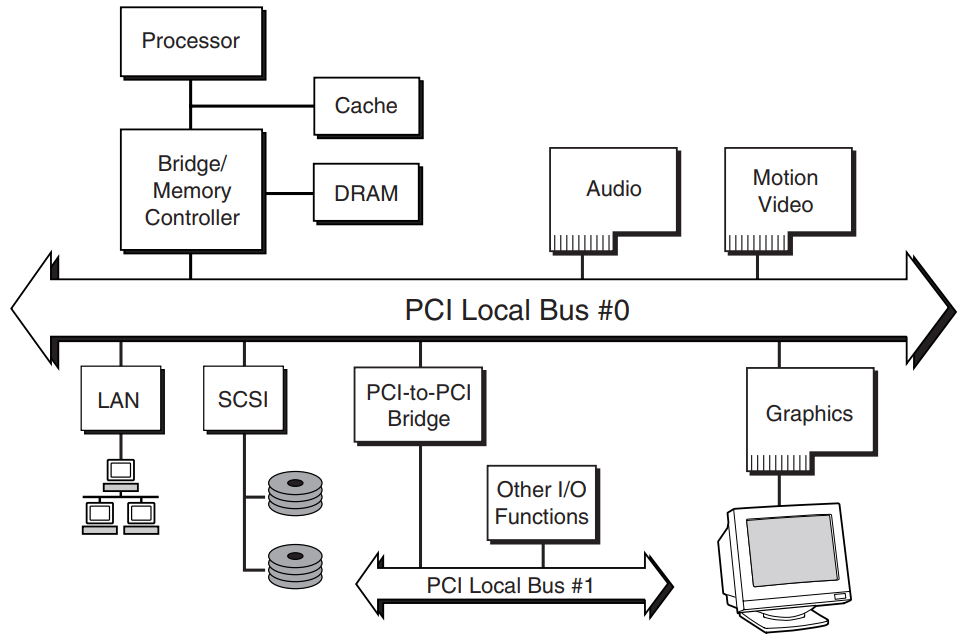

公共(Common Refclk--CC)和分立(Independent Refclk--IR)参考时钟的架构示意如下图所示,公共参考时钟架构中,系统中由一个统一的时钟源驱动发射和接收端,而分立参考时钟架构中,发射和接收端由不同的时钟源所驱动,并且每个时钟源可以独立进行相关抖动参数的定义。

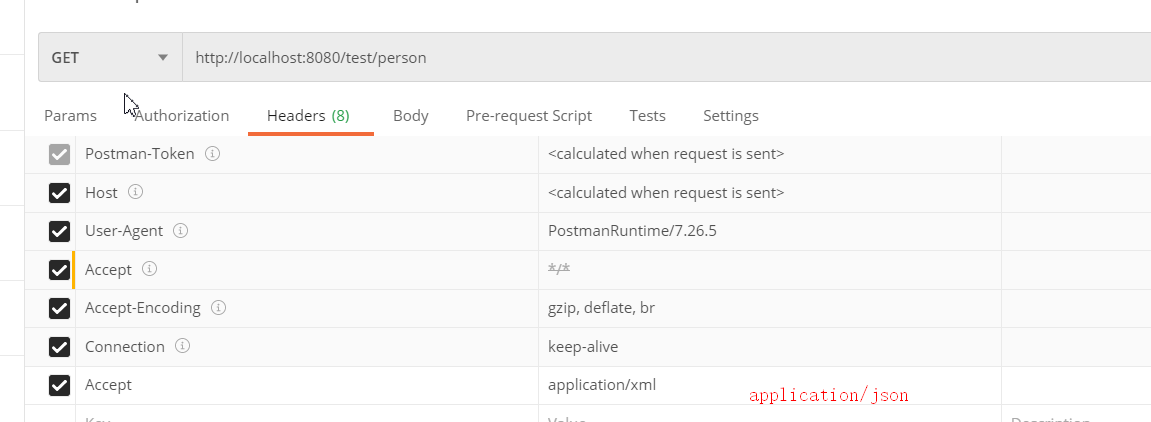

针对Refclk的测试台架配置如下图所示,台架对信号传输通道有明确的插入损耗、阻抗控制和负载属性要求,用于模拟可能发生在PCI Express设备的引脚上的最坏情况下的信号衰减情况,并使用相位噪声分析仪测量参考时钟抖动相位,用示波器测量参考时钟抖动参数,所有测试都需要在50欧姆设备端接负载下进行,以避免不必要的反射对结果产生影响。

下表列出了Refclk需要关注的DC&AC电气设计参数规格,基于上述台架的测试结果需要满足这些技术要求;

除此之外,如下表所示,还有一些额外的与具体数据传输速率相关的技术参数,对时钟设计要求严苛的场景可以进行详细的设计参考。

另外,对于支持SSC的Refclk必须满足低频范围内的额外抖动限制,其定义为从30 kHz到500 kHz的连续分段线性图,如下图所示,未经滤波的Refclk相位抖动必须在该频率范围内低于限制值。

2 发射端通道设计

与参考时钟的通道设计复用,Tx和Rx的回波损耗(RL)测量值是相同的,其测量是在各自的break-out通道的末端进行的,并要求break-out通道对RL的贡献被去嵌入,从而将RL参数与Tx或Rx引脚相关联。

图中Breakout和Replica通道应设计为在奈奎斯特频率的插入损耗小于2 dB(最大信号速率为16.0 GT/s时,奈奎斯特频率为8GHz),并且从TP2或TP3测量时返回损耗大于15 dB,这可能需要使用低损耗介质、宽信号走线和通孔背钻等技术,因为,只有性能更好的通道设计,去嵌入的效果才可能更优。

RL测量时采用的参考阻抗为50欧姆,如下图所示定义了 Tx和Rx端口去嵌入后的差模和共模的RL模板,两种模式都被定义在50 MHz到16.0 GHz的频率范围内进行测量。

3 发送均衡技术

在发送端速率为2.5、5.0 GT/s时,仅支持数据去加重功能,而在发送端速率为8.0、16.0和32.0 GT/s时,可支持具备三个抽头的FIR滤波器的均衡器结构。

上述均衡器结构的规范参数因子配置如下表所示,以此为基础对发送信号进行调理。

具体测试时,需要根据不同的波形判定其处于预加重还是去加重,因为均衡器调节的效果发生在信号边沿处,因此,可以通过边沿峰值的位置来判定所使用的均衡方式,由上表可知:

当Pre-shoot>0dB时,即预加重模式,意味着均衡器结构图中的Vc>Vb,信号波形可能如下图所示:

当De-emphasis<0dB时,即去加重模式,意味着均衡器结构图中的Vb<Va,信号波形可能如下图所示:

由上述Va、Vb和Vc之间的关系可知,不同的因子组合会导致作为稳态信号电平Vb的变化,当Pre-shoot和De-emphasis非零时,使之不能达到信号的最大电压摆幅Vd,因此,规范对极限电压摆幅(Voltage Swing)给出了限制要求,虽然降低电压摆幅可以一定程度地降低功耗,但是也必须在最小限制要求的范围内,否则,信号可能会因为过度调制导致无法正常传输和接收。

根据前面均衡器结构图的参数描述,当完成Pre-shoot和De-emphasis的配置,即可得到Boost的参数,这三个参数组成一个矩阵单元,如下图所示,该矩阵单元有三个项对应预加重(PS)、去加重(DE)和boost,蓝色和橙色单元分别代表了电压摆动降额的最小和最大区域,信号调理需要在此区域以内(两个虚线之间的区域)进行参数的选择。

4 接收端通道设计

所有接收器的信号质量都是通过施加在校准通道上的应力眼睛来测试验证的,该校准通道模拟在实际通道中遇到的接近最坏情况的损失特性,对于2.5 GT/s和5.0 GT/s,恢复的眼图相当于Rx引脚处;对于8.0 GT/s、16.0 GT/s和32.0 GT/s,相当于应用Rx均衡后的裸芯片端口(Die)处。

一个标准的测试台架如下图所示,信号源连接到校准通道后,在TP2处进行应力眼图的校准,校准合格后,再将信号源应用于DUT,TP1~TP2包含了信号源和DUT之间的所有组件,从而捕获了由于电缆和Replica/Breakout通道造成的总体插入损失中的所有非理想特性,而发射端到TP1的所有直流和交流损耗被假设为0,否则必须进行去嵌入,换言之,测试只允许计入TP3之后的通道损耗。

一个校准通道的插入损耗指标通过一对高频和低频的IL极限值来定义,校准通道需要包括TP3后的所有物理损失,如下图所示为不同速率下的IL限制要求。

通道的特性阻抗要求为:2.5、5.0和8.0 GT/s速率下,通道要求差分100 欧姆和单端50 欧姆,16.0 GT/s和32.0 GT/s速率下,通道要求差分85 欧姆和单端42.5 欧姆,阻抗公差应保持在±5%或更高。

值得注意的是,插入损耗的定义虽然没有覆盖1GHz以下的频段,但是校准通道的DC阻抗之和(D+/-)不能超过7.5欧姆,另外,对于16.0 GT/s和32.0 GT/s,插入损失范围FHIGH-IL-MIN到FHIGH-IL-MAX只是名义上的定义,实际中,最好保证覆盖范围从“FHIGH-IL-MIN减去2 dB”到“FHIGH-IL-MAX加上3 dB”。

校准通道的回波损耗定义如下,分为16和32 GT/s两个版本:

请注意,校准通道是用于模拟真实信道参数的,因此,现实中,工程师可以拿这些参数对其互连通道进行设计约束,使用时,请注意与前文中的Tx、Rx端的回波损耗参数进行区分。

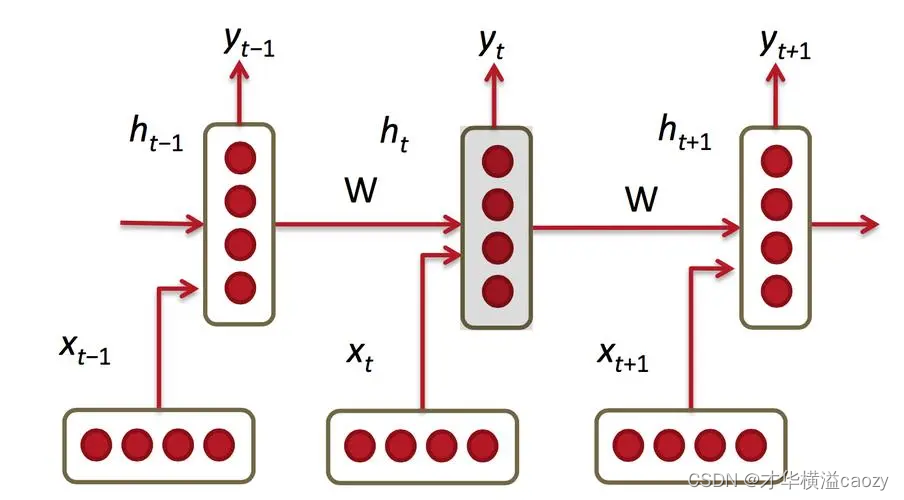

5 接收均衡技术

在2.5和5.0 GT/s速率下,并不需要额外定义Rx端的信号后处理,有Tx端的均衡技术已经足够使用; 在8.0、16.0、32.0 GT/s速率下,TP2的应力眼图通常是打不开的,此时就需要通过使用接收均衡器进行优化,该均衡器可以实现CTLE和1-tap(8 GT/s)、2-tap(16 GT/s)、3-tap(32 GT/s)DFFE功能。

8.0和16.0 GT/s的Rx均衡定义了一个具有固定低频和高频极点的一阶CTLE,如图所示,对于8.0 GT/s速率,ADC可在-6至-12 dB范围内调节,调节步长为1.0 dB,16.0 GT/s的参数基本相同,除了将ωp2系数改为16 GHz。

32.0 GT/s的Rx均衡定义了一个具有固定极点的二阶CTLE,如图所示,ADC可在-5至-15 dB范围内调节,调节步长为1.0 dB。

CTLE往往需要与DFE搭配使用,对于8.0 GT/s和16.0GT/s,d1的限制为±30 mV;对于16.0GT/s,d2的限制为±20 mV; 对于32.0GT/s,d2和d3的限制为±20 mV。

当完成上述的信号后处理配置,既可以进行应力眼图的测试,规范中根据不同速率,明确给出了眼图模板的测试指标,需要注意的是,这些眼高和眼宽的指标都是在信号误码率BER10^-12等级下获取的。

6 结语

实际的PCIe规范文档中,电气指标的技术内容很多,上述内容仅是关键部分的汇总,另外,本人的理解难免有所偏差,因此,感兴趣的工程师,需要仔细阅读文档的内容,以获取更多对设计有帮助的指标要求。

参考文献

[1] PCI Express Base Specification Revision 5.0, May 2019;

扩展阅读

[1] SerDes系列之DFE均衡技术_serdes ffe-CSDN博客

[2] SerDes系列之CTLE均衡技术_serdes ctle-CSDN博客