目录

1 背景

最近使用FPGA驱动USB PHY实现高速USB功能,为了方便,购买了一块微雪的USB3300子板,发现怎么都枚举不了,使用逻辑分析仪抓取波形,和STM32F407+USB3300波形进行对比,发现STP拉高是作为激活PHY CLKOUT的电平触发信号,目前STP也正常拉高了,就是不能输出时钟。

突然查看手册,发现USB3300的IO电压是3.3V的,输入电压最小为2.0V,也就是说我的FPGA电压是1.8V,都没达到USB3300的IO电压阈值。这就很尴尬了,只有重新选择其他芯片。

通过网上对比资料,最终选定了如下几款型号:

- USB3318

- USB3320

- CH132B

2 USB3320在FPGA上的应用

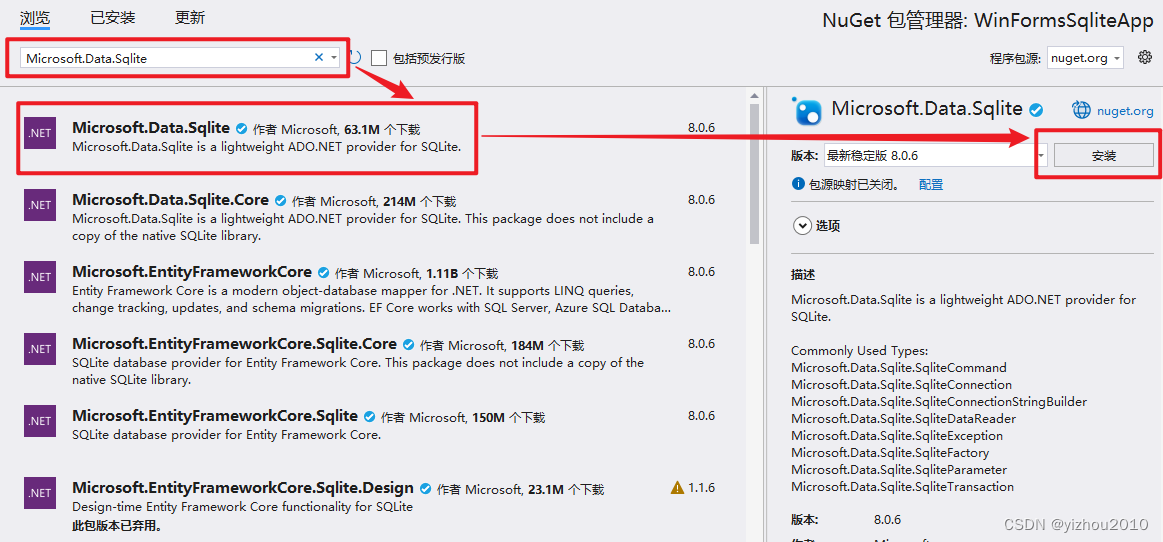

对本人来说,更加愿意支持国产芯片CH132B,但是通过很多渠道,都不能购买到散片(只能去官方申请样品),网上只能买到CH132H,显然是不满足的。

接下来就是对比USB3318和USB3320这两款芯片了,感觉这两款芯片功能基本一致,通过进一步对比,发现USB3318市面上没有多少货了,最终选择了USB3320这款芯片。

接下来就是查看USB3320这款芯片的手册了,从Features可以看出,USB3320支持1.8V-3.3V的IO电压范围。

根据下图绘制原理图,这里使用的是ULPI OUTPUT CLOCK模式,从下图可以看出,如果使用1.8V的VDDIO,那么pin32需要接1.8V电压(自己则是在某宝上购买的现成的USB3320测试板)。

此处有个易错项,USB3320可通过REFSEL[2:0]引脚选择外部晶振输入频率,如果使用52M晶振,REFSEL[2:0]引脚接地即可,如果使用其他频率的晶振,则需要向REFSEL[2:0]引脚输入不同的电平,这里的电平是VDDIO电平。

到这里就基本结束了,购买的板子,调试也很顺利,基本上一步到位就成功了。

如果是自己绘制板子,需要特别注意VDDIO的电压,不然轻者可能造成不能达到芯片IO电压阈值,重则导致IO引脚烧坏。

当然如果必须使用USB3300芯片和FPGA进行通信,也是可以实现的,需要在USB3300和FPGA中间增加一个双电源总线收发芯片,例如SN74LVC8T245、SN74LVC16244A等(根据实际情况选择其他型号),主要作用是进行电压的匹配,也就是把FPGA输出的1.8V电压经过电源总线收发芯片转换成3.3V电压输出到USB3300,把USB3300输出的3.3V电压经过电源总线收发芯片转换成1.8V电压输出到FPGA。