FPGA可重构技术就是通过上位机控制在FPGA运行过程中加载不同的Bitstream文件,FPGA芯片根据文件内的不同逻辑将内部的资源全部或部分进行重新配置以达到多种功能任务动态切换的目标,从而提高了使用FPGA进行开发的灵活度。

FPGA芯片本身就具有可以反复擦写的特性,允许FPGA开发者编写不同的代码进行重复编程,而FPGA可重构技术正是在这个特性之上,采用分时复用的模式让不同任务功能的Bitstream文件使用FPGA芯片内部的各种逻辑资源,使得同一个逻辑电路在不同时间段上加载不同的功能模块。从时间轴上看,系统的每一项任务功能在FPGA芯片上依次执行,系统的整体功能全部得以实现。从局部看,FPGA只执行了一项小任务,而从整体看,FPGA完成了整个系统任务。使用一块FPGA芯片完成了需要多块FPGA芯片的任务,由此可见FPGA内部资源的利用率得到很大提升。

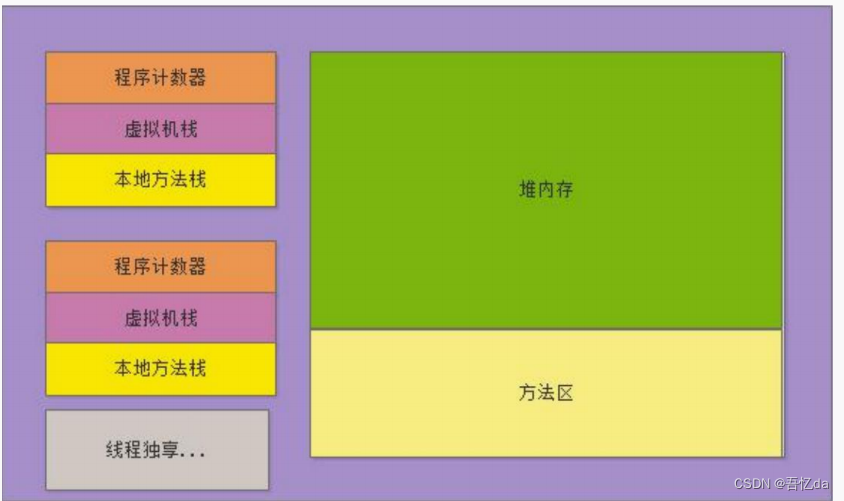

FPGA上的可重构技术根据FPGA芯片内部的不同结构可以分为两种,分别是动态可重构和静态可重构。如果FPGA芯片是常规的SRAM结构,那么它只能做到静态可重构,重构过程必须首先发送中断指令停止正在运行的程序,之后再把全新的Bitstream文件加载到FPGA上。而如果FPGA芯片是特殊结构,那么它就可以进行动态可重构,重构过程可以在FPGA运行时期进行,动态可重构不但可以在系统运行时期随时改变模块参数,甚至可以在系统运行时期在FPGA内部的可重构区域动态重构电路逻辑。

FPGA的动态可重构又可以分为动态全局可重构和动态局部可重构。动态全局可重构是指上位机给FPGA芯片加载一个全新的配置文件,而这个配置文件包含了新的任务需求所要涉及的整片FPGA内所有资源,从而实现FPGA重新配置,上一个任务实现的所有逻辑电路将全部消除。在重构操作执行前,首先在外挂存储器中加载多个不同任务需求的配置文件,同时每个配置文件中都包含该任务所需要涉及的FPGA芯片全部逻辑资源。正是因为每一个配置文件都包含了整块FPGA芯片的所有资源,所以动态全局可重构只能从外挂存储器中选择将一个配置文件加载到FPGA芯片中。当这个配置文件对应的任务结束后,再选择另一个新的配置文件加载到FPGA芯片中,通过不同配置文件的分时加载实现系统功能任务的切换。

动态局部可重构因为只重构部分区域,所以配置文件中的重构内容也相应变小,重构时间也随之缩短。但是动态局部可重构的难点在于静态区域和可重构区域的大小划分是否可以满足系统功能要求、分别处在两个区域的模块之间如何进行通信以及如何在可重构区域进行合理的布局布线。因此使用动态局部可重构的实现过程相对复杂。