基于 MIPS 指令系统的处理器设计

根据计算机组成原理课程所学的知识,设计一个基于 MIPS 指令系统的处理 器,深刻理解处理器结构和计算机系统的整体工作原理。

🍆 0 实验要求

0.1 处理器功能及指令系统定义

本实验的任务是结合数据通路的思想,设计一个简单的基于 MIPS 指令系统 的 RISC 处理器,选取有代表性的 R 类指令、I 类指令和 J 类指令,指令总的条数不少于 5 条。

处理器的指令字长为 32 位,包含 32 个 32 位通用寄存器 R0~R31,具体指令格式参考课件和 MIPS-课外阅读资料。

0.2 设计要求

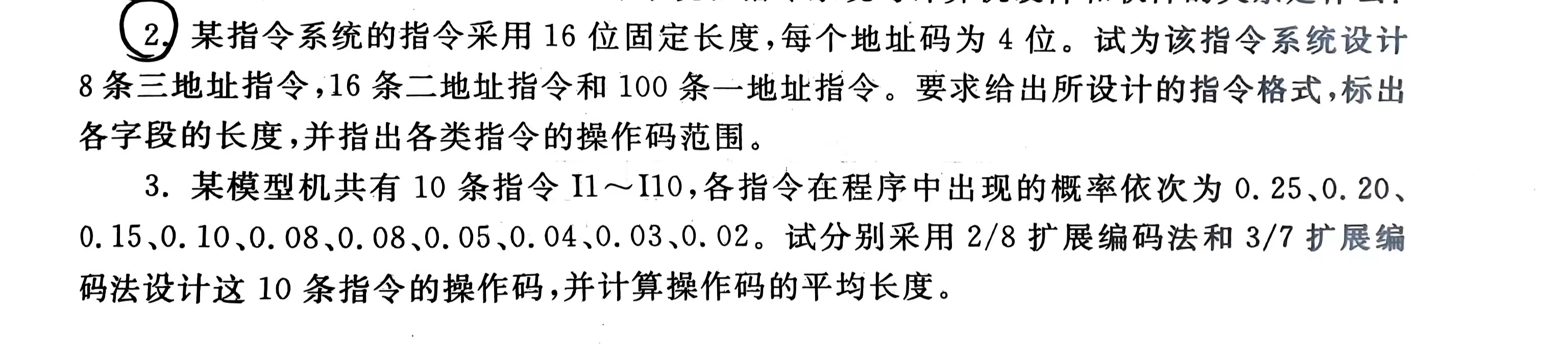

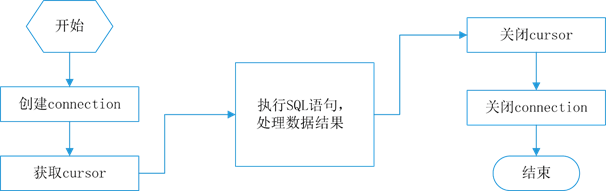

要求根据以上给定的指令系统设计处理器,处理器工作流程按取指、译码、 运算、访存、写回五个阶段进行(或自行设计)。

控制器设计方法可选(组合逻辑设计或微程序设计方法) 需完成的环节包括:

- 指令格式设计;

- 微操作的定义;

- 节拍的划分

- 处理器结构设计框图及功能描述

- 如采用微程序设计,写出每条机器指令对应的微指令序列,确定微指令字长和微指令格式,编写微指令码点

提交纸质版,统一 A4 纸,左侧装订。正文 5 号字宋体,西文用 Times New Roman,1.2 倍行距。要求排版规范,图表规范。 提交时间:2024 年 6 月 25 日提交。

🍉1.引言

1.1 MIPS指令概述

MIPS(Microprocessor without Interlocked Pipeline Stages,无互锁流水线微处 理器)是一种精简指令集(RISC)架构,由美国 MIPS 计算机系统公司(由斯坦 福大学团队于 1984 年创立,现为美普思科技)开发,以其高效、简洁和强大的 特性,在嵌入式系统、工作站和超级计算机等领域得到了广泛应用。

MIPS 架构有多个版本,包括 MIPS I、II、III、IV,以及 MIPS V,这五个版本又分别分为 MIPS32/64 Release(即其 32 位/64 位实现)。截至 2017 年 4 月的 最新版本是 MIPS32/64 Release 6;2021 年 3 月,美普思科技宣布停止开发 MIPS 架构,并加入 RISC-V 基金会,未来的处理器设计将基于 RISC-V 架构。

MIPS指令集有以下特点:

- 简单的Load/Store结构。

- 易于流水线CPU设计。

- 易于编译器开发。

- MIPS指令的寻址方式非常简单,每条指令的操作也非常简单。

1.2 MIPS指令格式概述

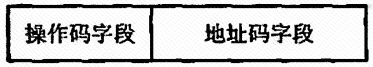

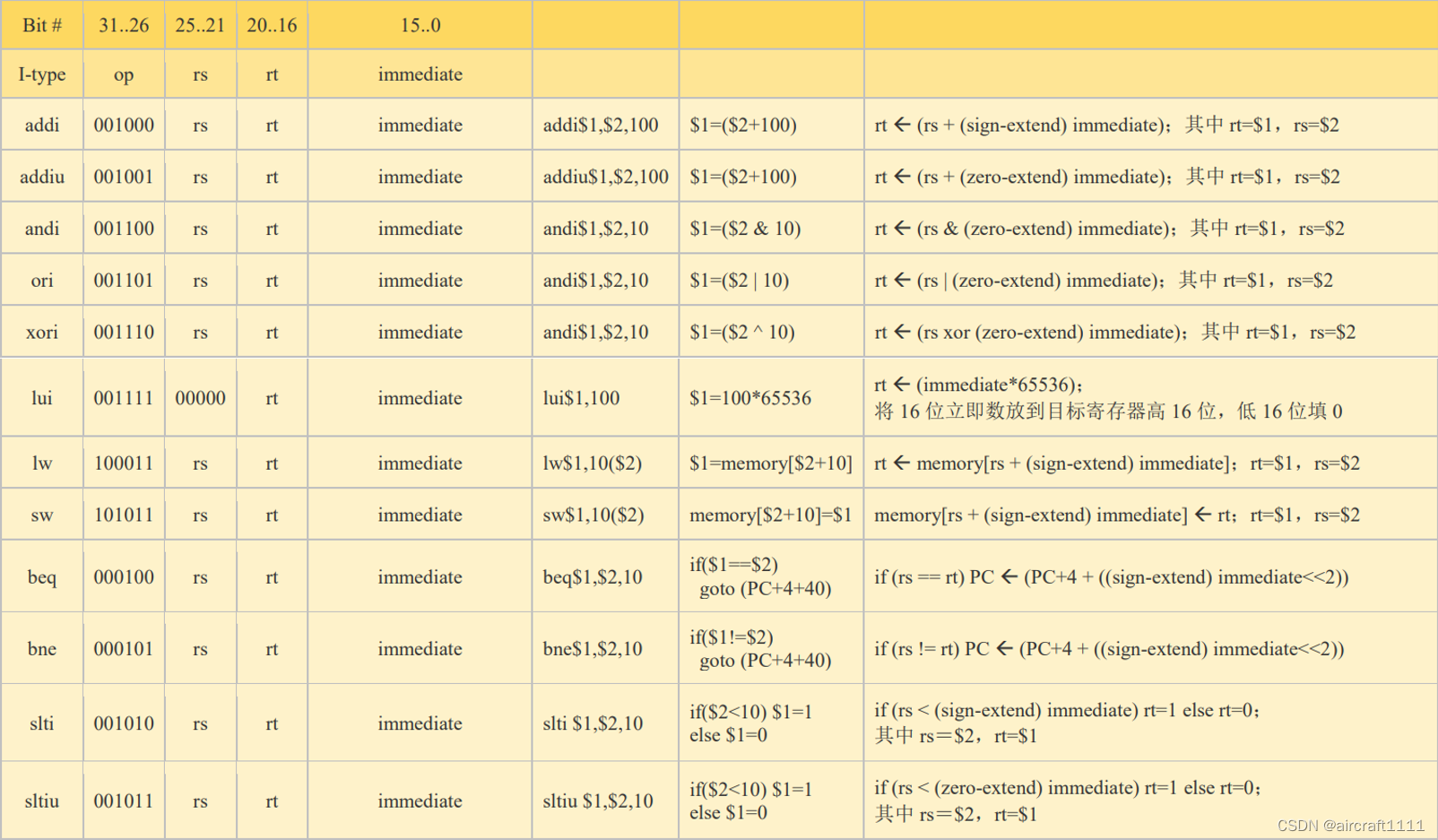

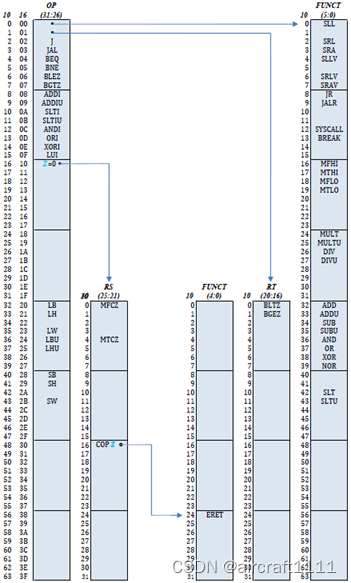

MIPS指令集的指令格式主要包括三种:R-Type、I-Type 和 J-Type。以下是这三种指令格式的详细介绍:

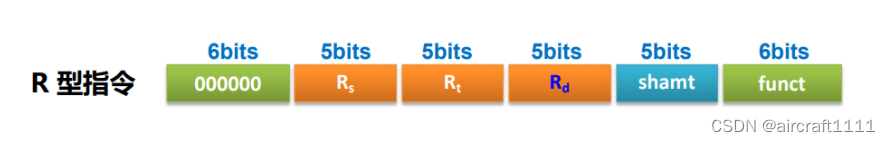

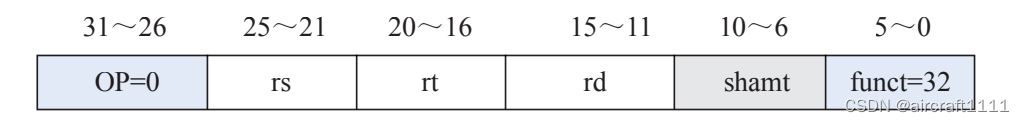

- R-Type 指令格式:

R-Type 指令通常用于操作寄存器之间的操作,如加法、减法、逻辑运算等。其基本格式如下:

OP rs rt rd shamt funct

OP:指令操作码,用于表示指令的类型。rs、rt、rd:分别表示源寄存器、目标寄存器和目的寄存器。shamt:表示移位操作的偏移量,一般用于逻辑左移或右移等操作。funct:功能字段,用于指明具体的操作。

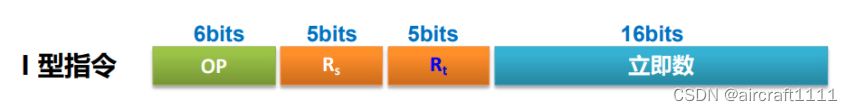

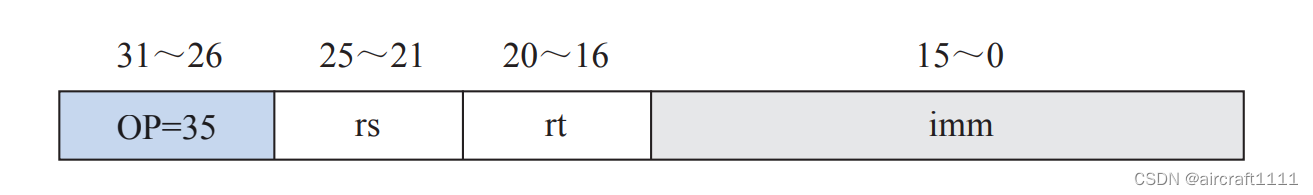

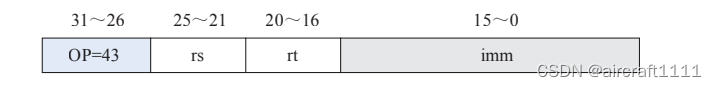

- I-Type 指令格式:

I-Type 指令主要用于立即数操作或者内存读写操作。其基本格式如下:

OP rs rt immediate

OP:指令操作码,表示指令类型。rs:源寄存器。rt:目标寄存器。immediate:立即数字段,用于存储立即数或者偏移量。

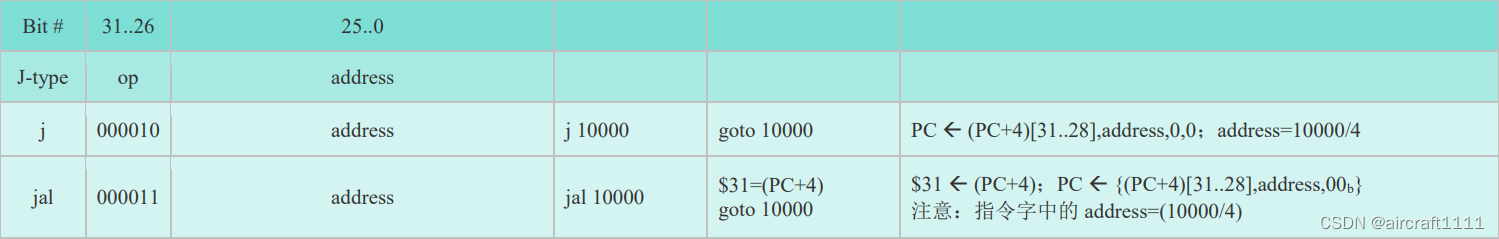

- J-Type 指令格式:

J-Type 指令主要用于跳转指令,如无条件跳转或者函数调用等。其基本格式如下:

OP address

OP:指令操作码,表示指令类型。address:跳转地址字段,用于存储跳转的目标地址。

总的来说,MIPS 指令集采用这三种不同的指令格式来支持不同类型的指令操作,使得指令编码简洁明了,有助于提高指令的执行效率。

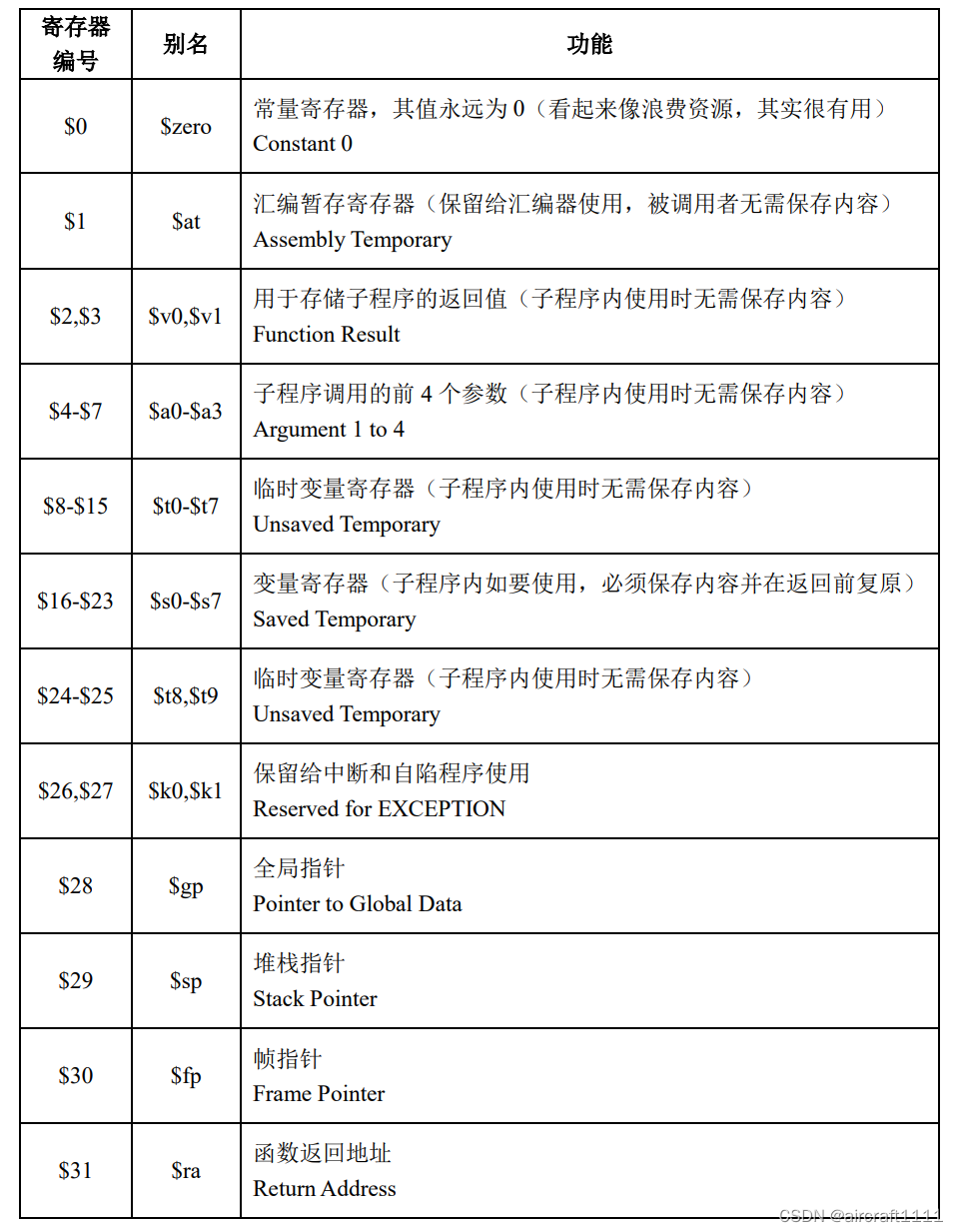

1.3 MIPS寄存器

MIPS有32个通用寄存器。硬件上,这些寄存器并没有区别(除了 0 号以外),区分的目的是为了不同的编译器产生的代码可以正常的互相调用。

🍍2 指令格式的设计

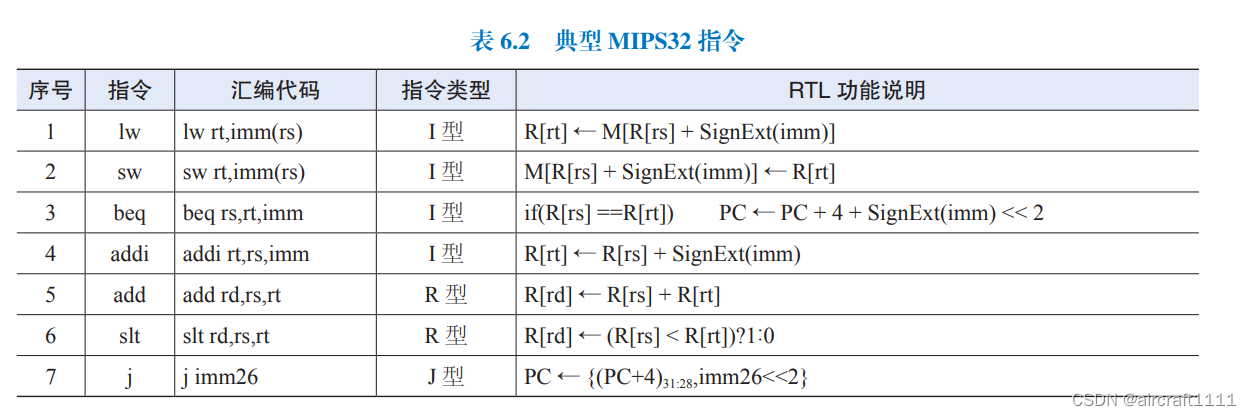

我们选择有代表性的"ADD","SUB","LW","SW","J“五条指令来进行处理器的设计。

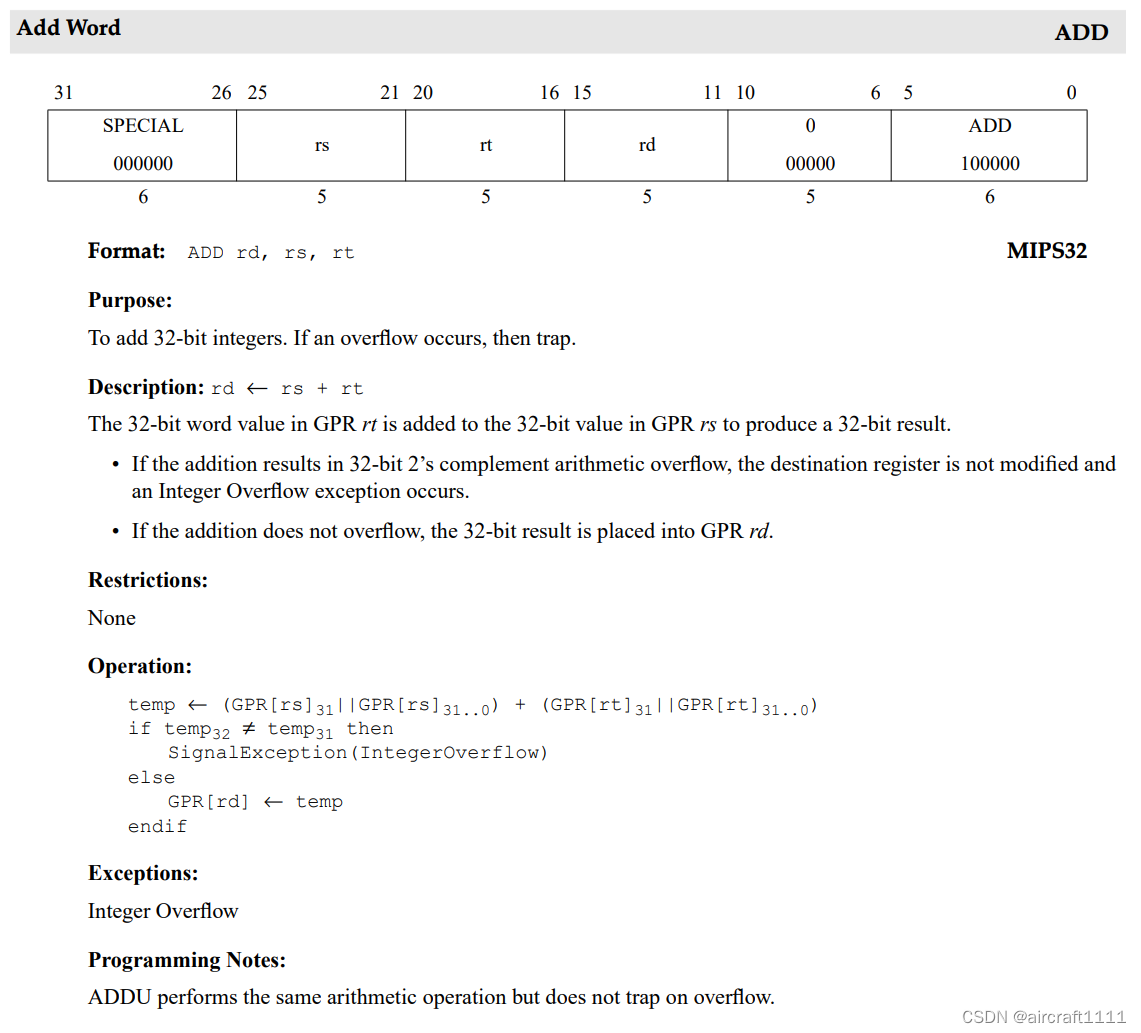

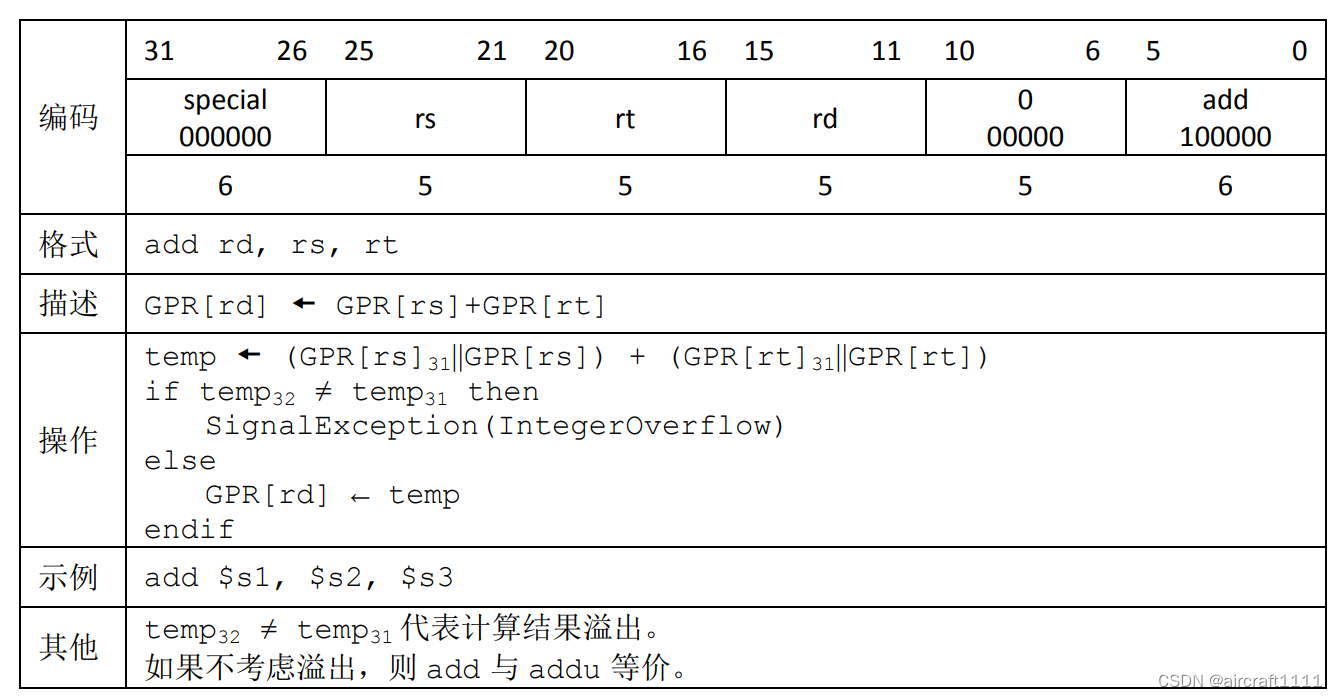

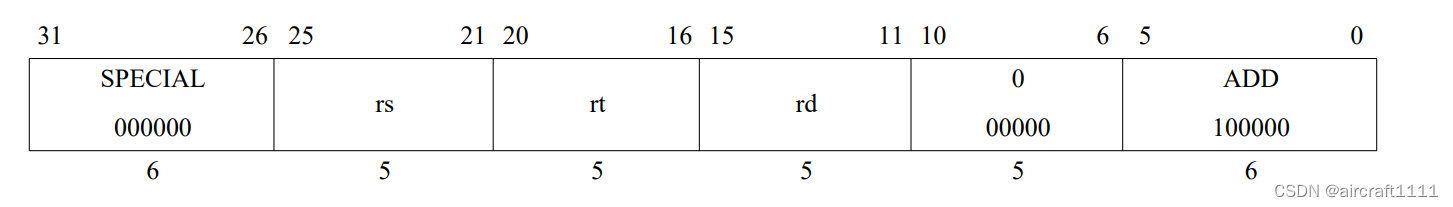

2.1 ADD指令设计

ADD rd, rs, rt

// e.g. ADD $t2, $t0, $t1

ADD指令的汇编格式为add rd,rs,rt,这实现了32位整数加的操作,加数与被加数分别置于rs和rd寄存器中,最后由ALU运算器计算出结果并存到rd寄存器中。

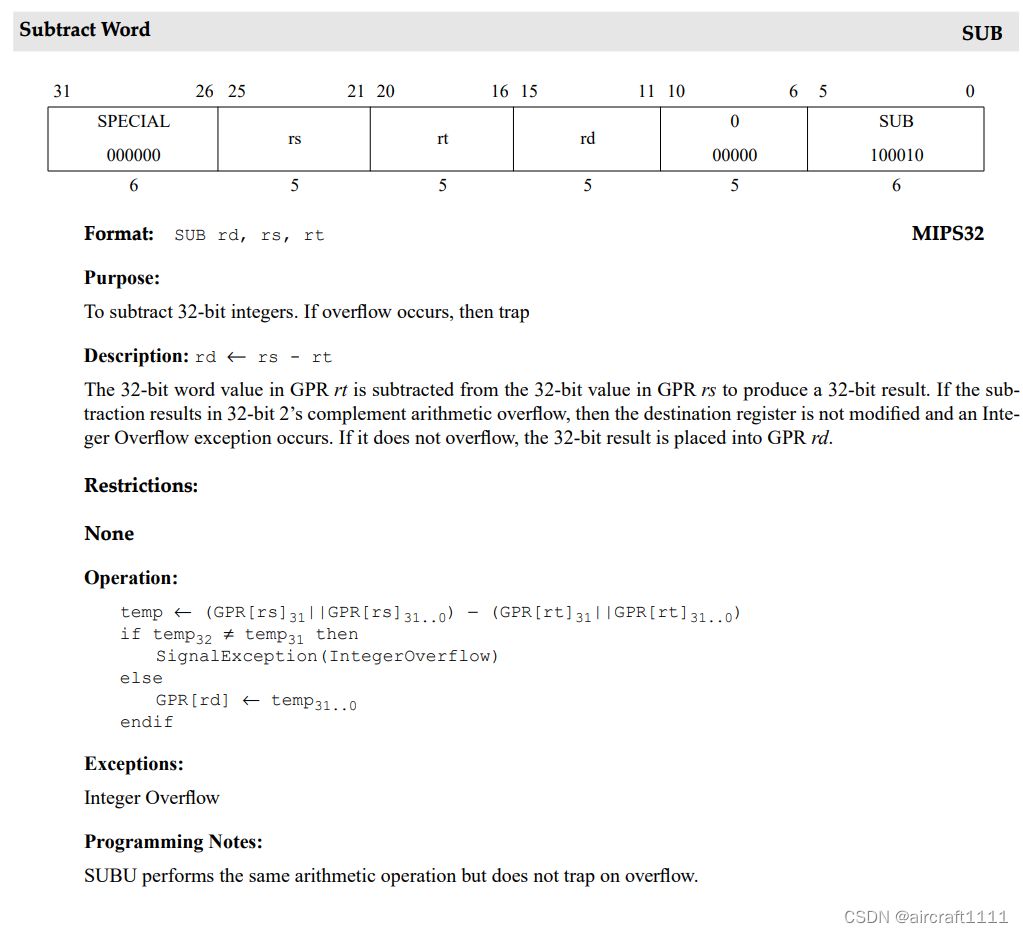

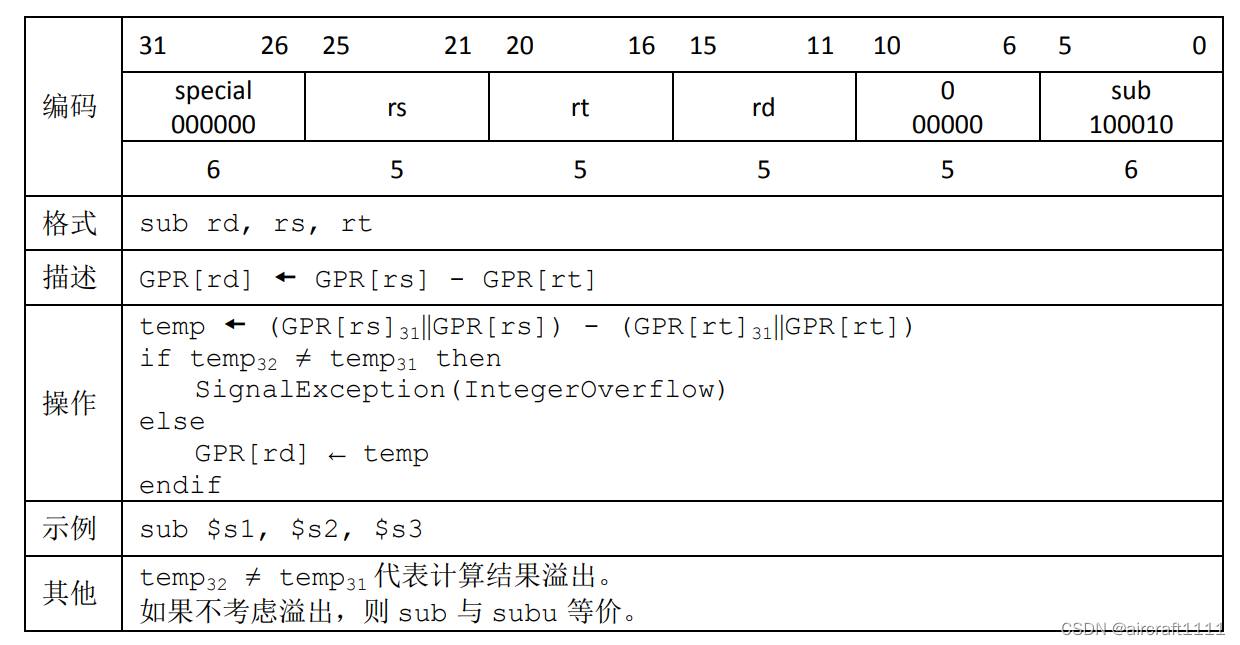

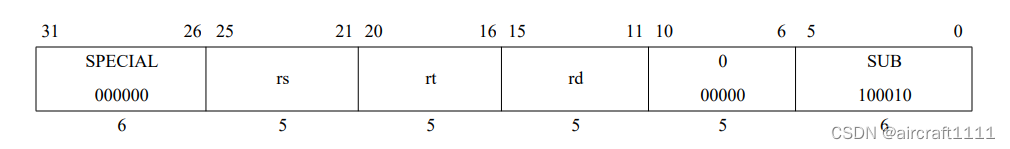

2.2 SUB指令设计

SUB rd, rs, rt

// e.g. SUB $t2, $t0, $t1

SUB指令的汇编格式为sub rd,rs,rt,这实现了32位整数减的操作,被减数与减数分别置于rs和rd寄存器中,最后由ALU运算器计算出结果并存到rd寄存器中。

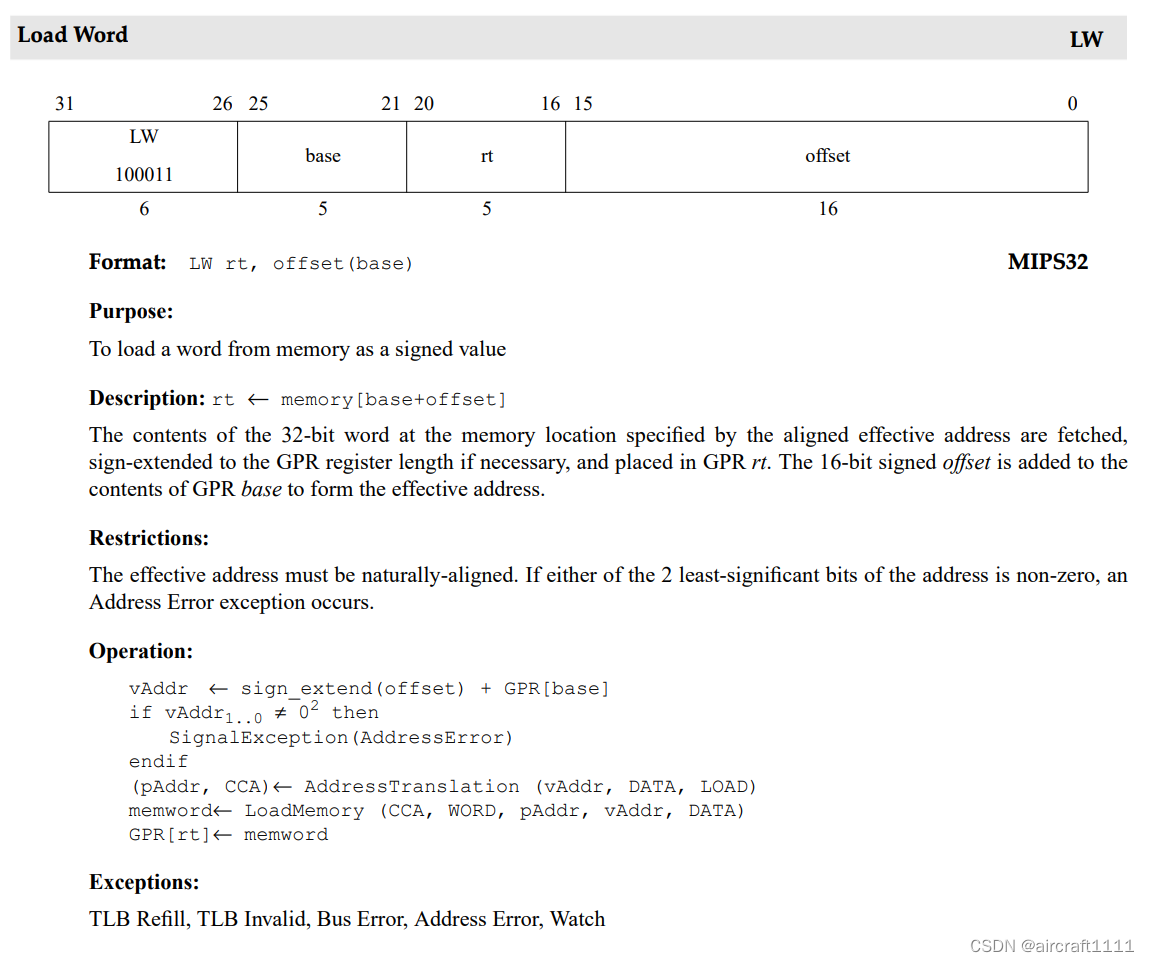

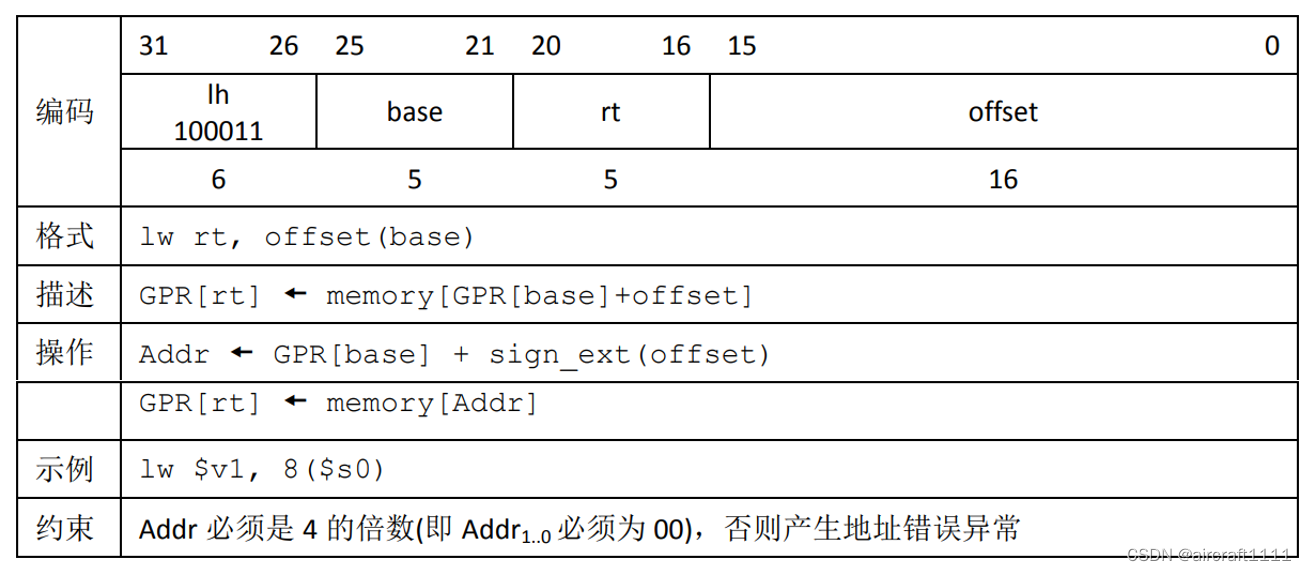

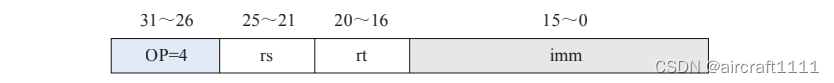

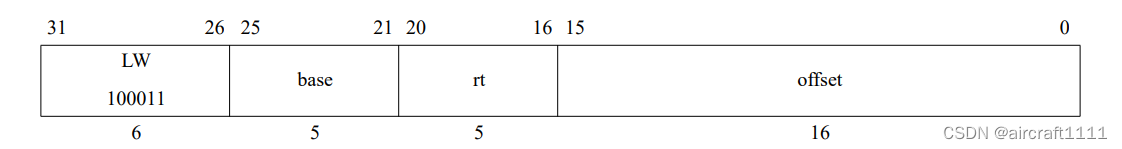

2.3 LW指令设计:

LW指令的汇编格式为lw rt,offset(rs),这将offset进行位拓展后与rs寄存器中数据相加获得访存地址,然后从该地址取出数据并存到rt寄存器中。

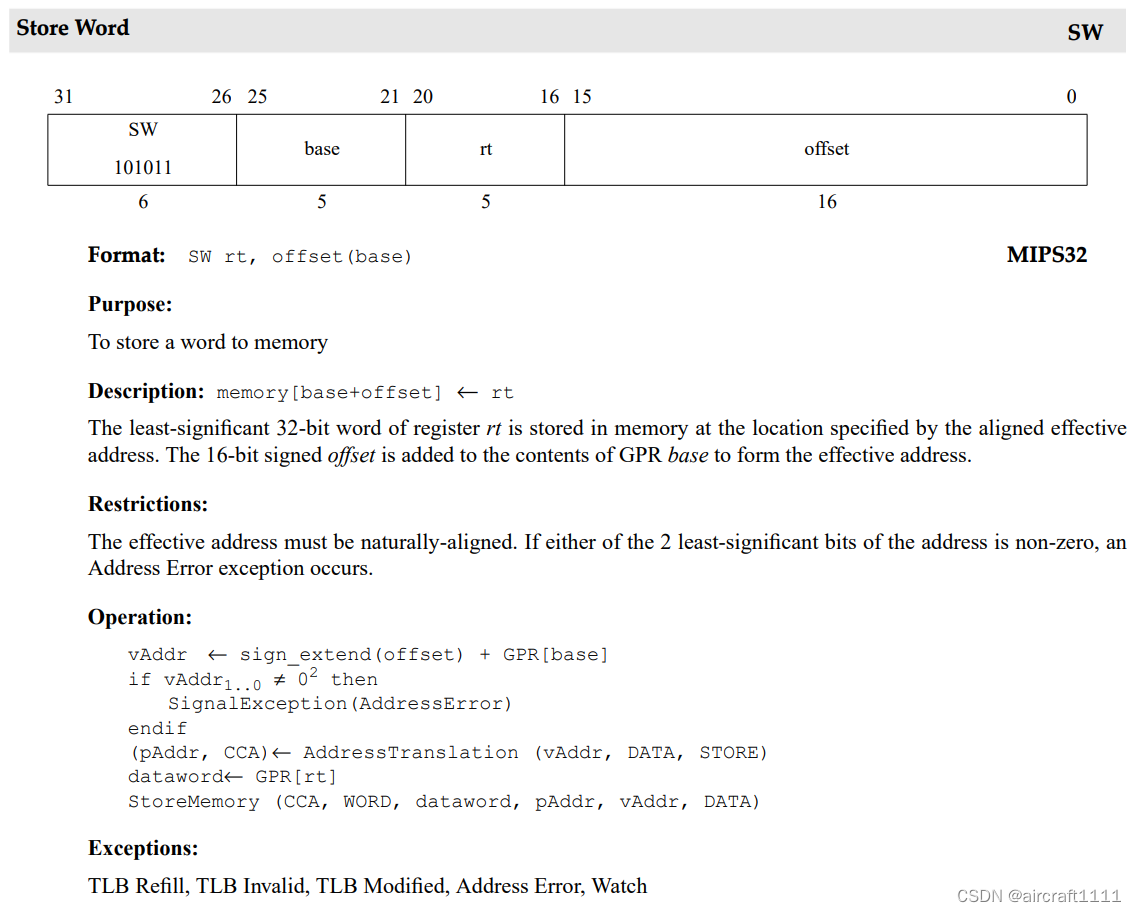

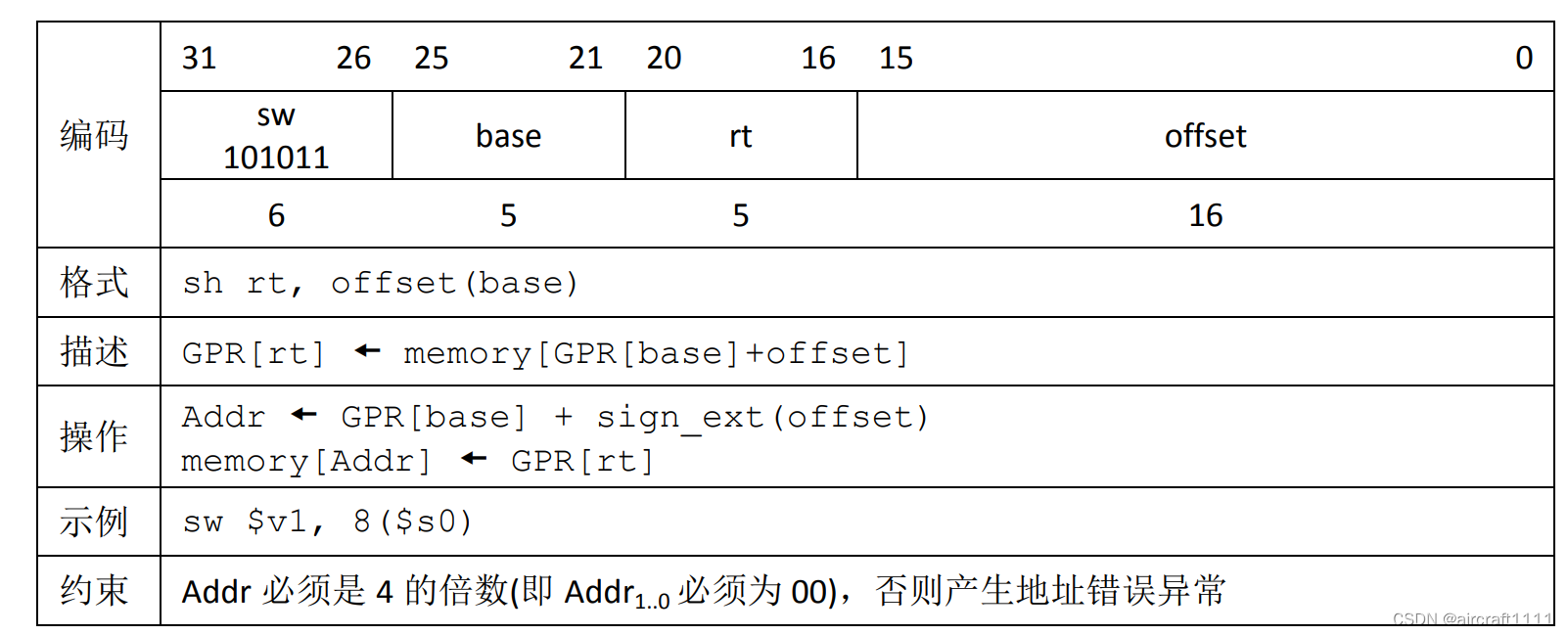

2.4 SW设计

SW指令的汇编格式为sw rt,offset(rs),这将rt寄存器中的数据存到offset与rs寄存器中数据计算后得到的地址位置处。

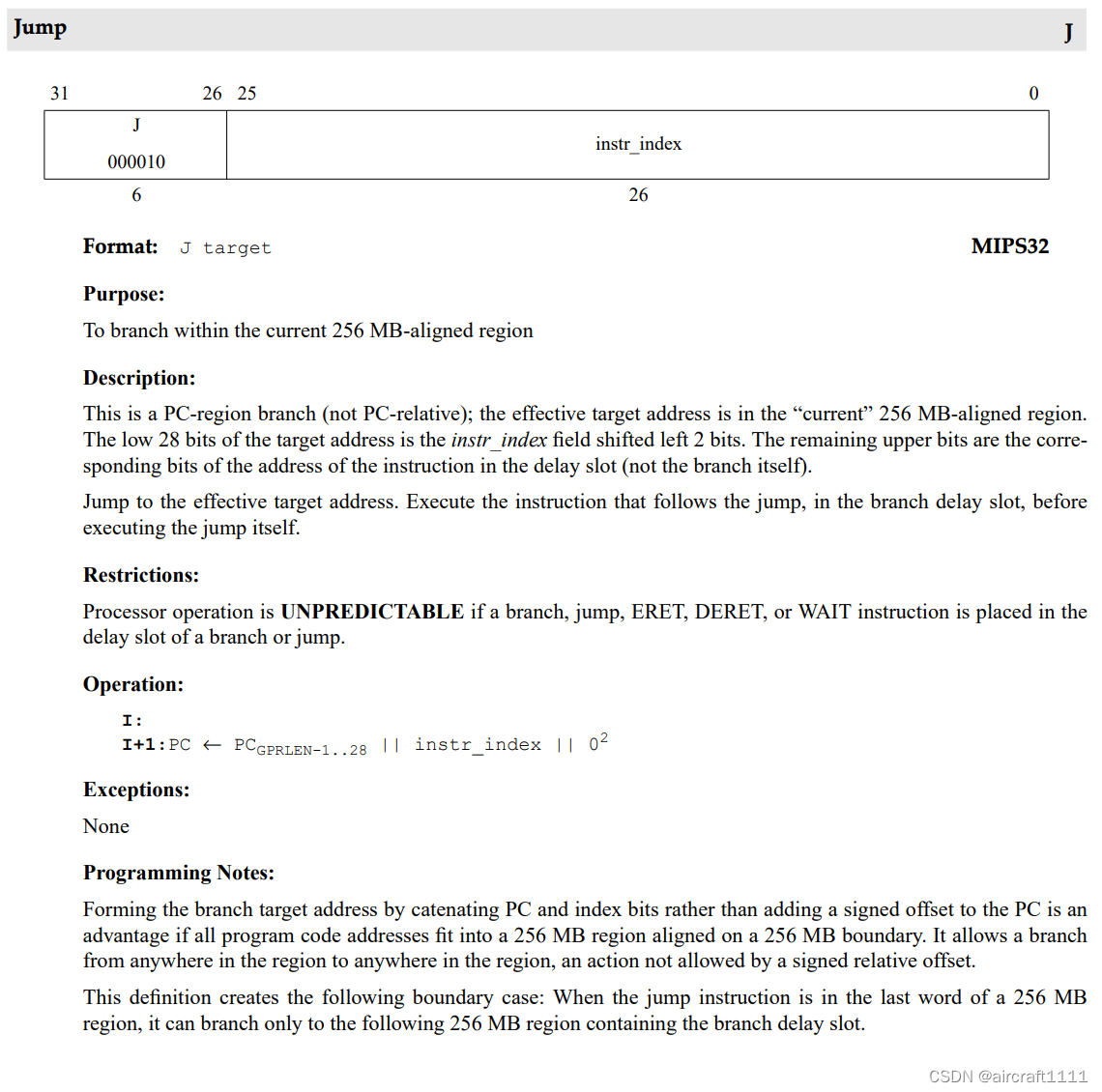

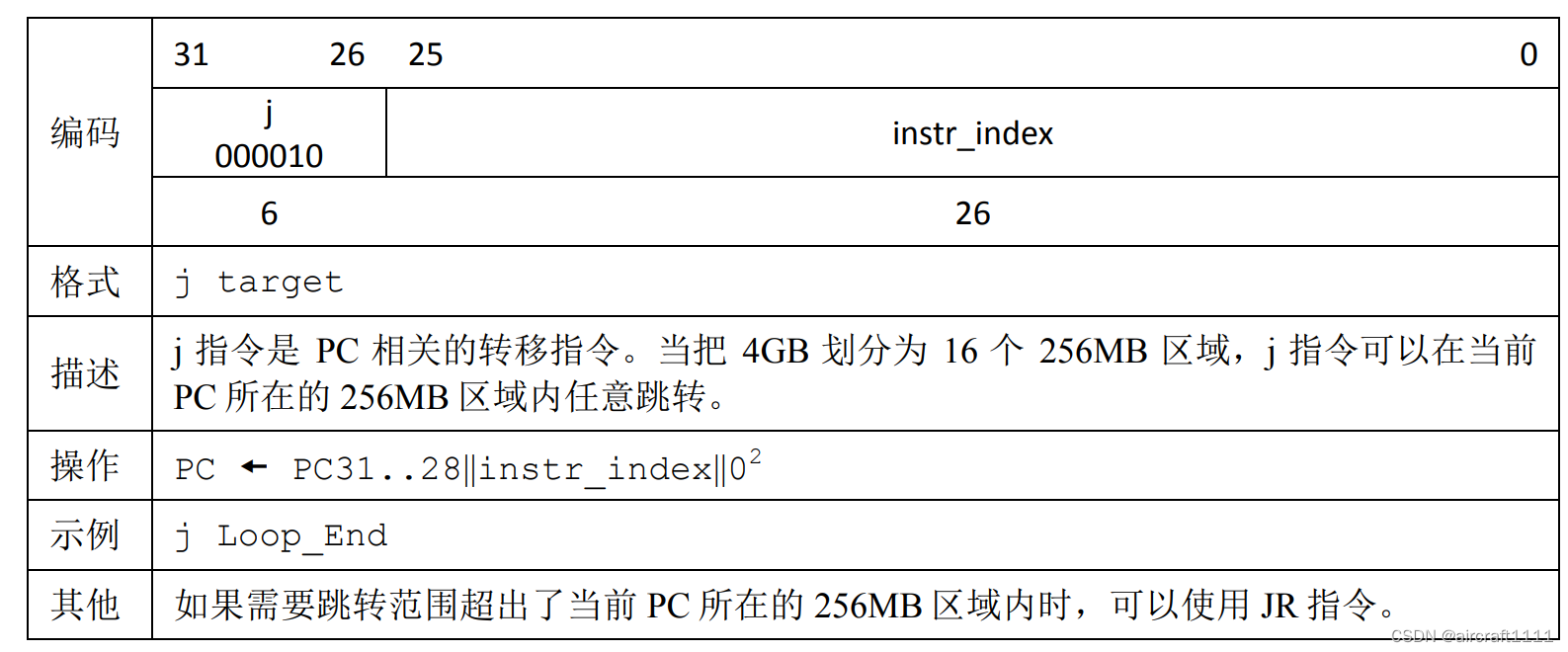

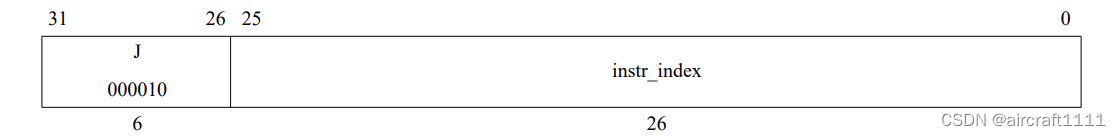

2.5 J指令设计

J target

// e.g. J 0x00400020

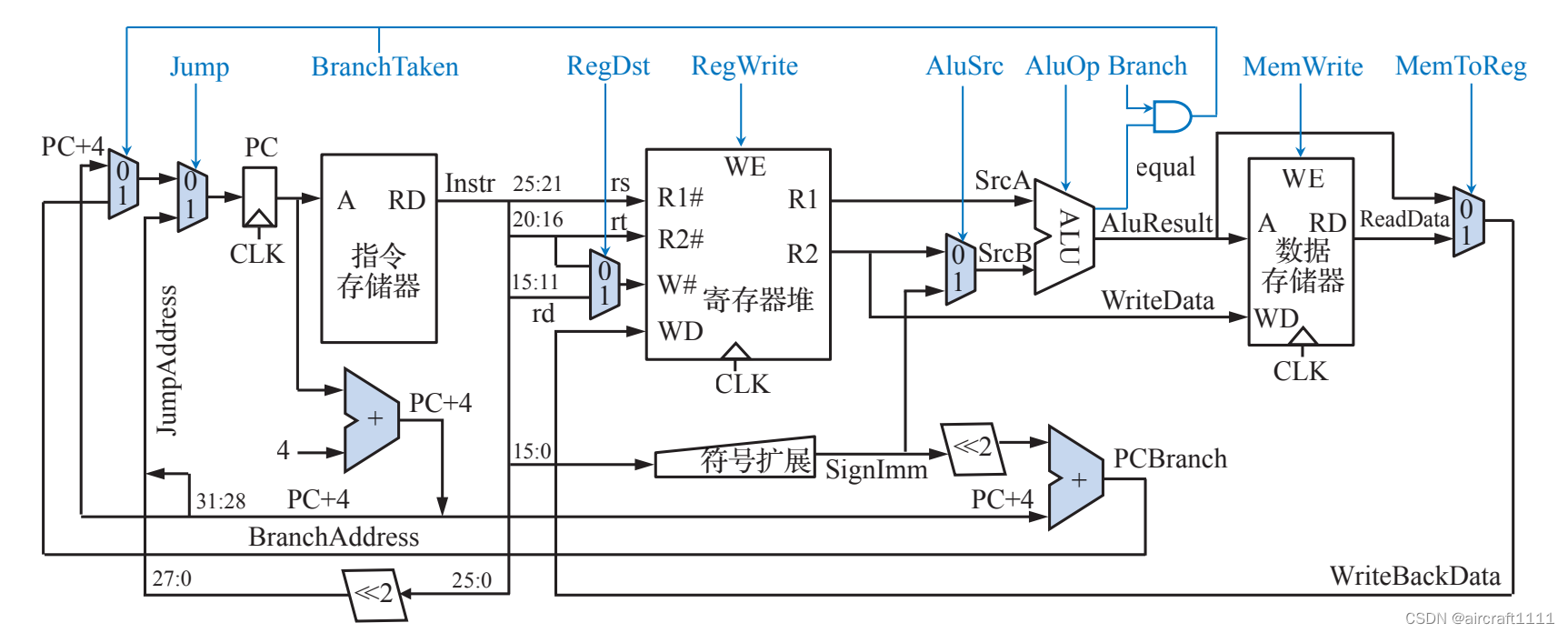

J指令的汇编格式为j target,其分支目标地址的计算与条件分支指令不同,具体是将顺序指令地址 PC+4 的高 4 位作为高地址部分并与指令字中的 26 位立即数 Address 左移两位得到的 28 位数据进行拼接,生成一个 32 位的无条件转移目标地址。

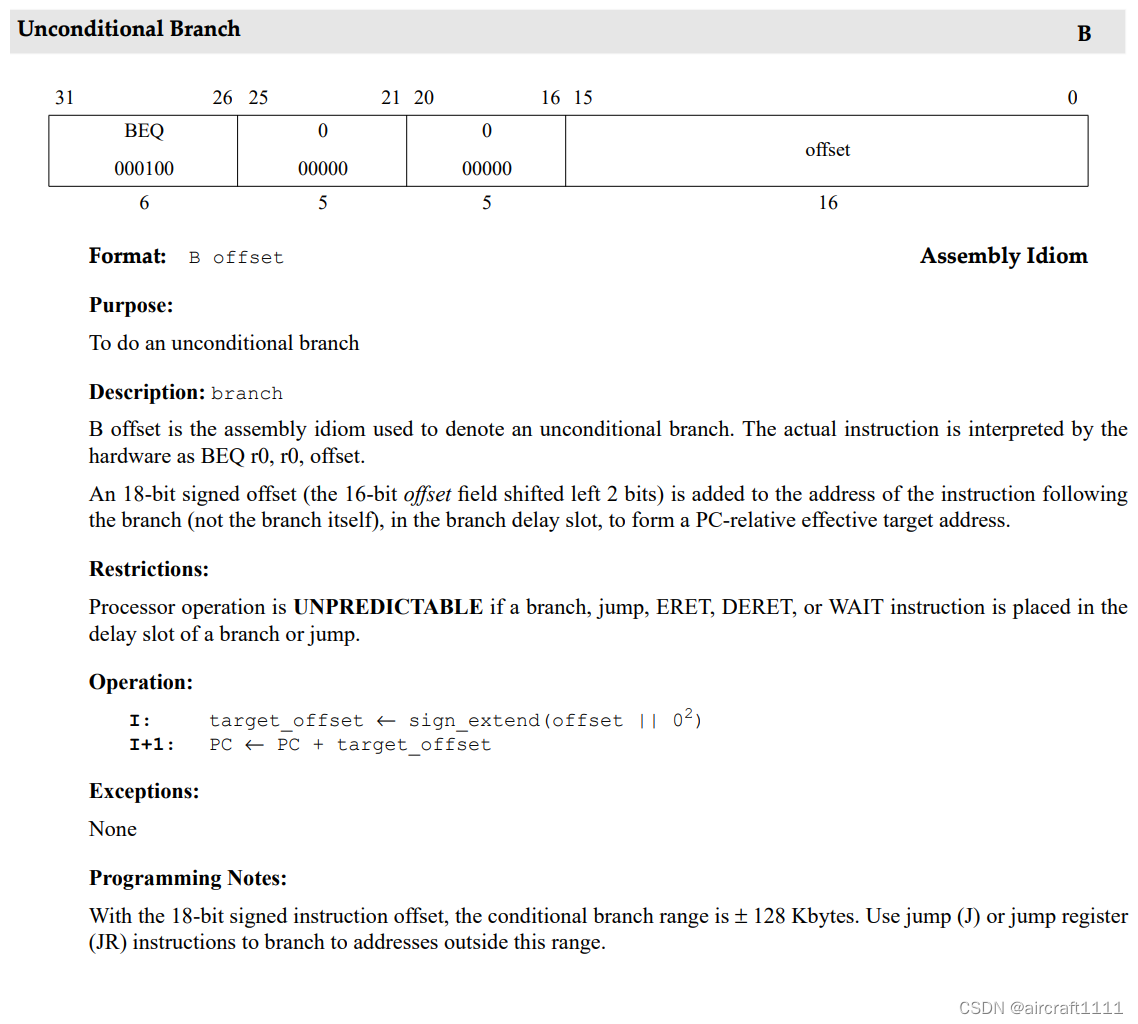

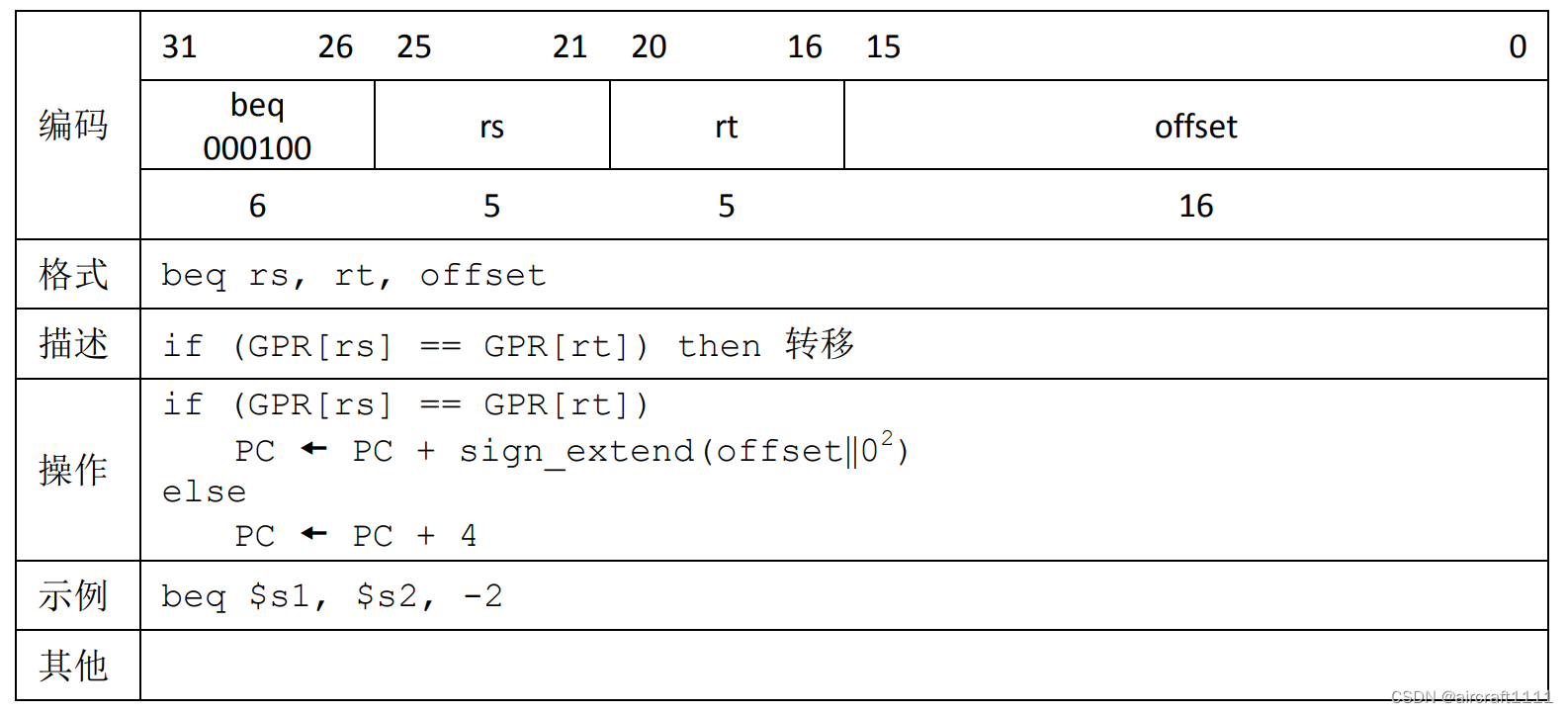

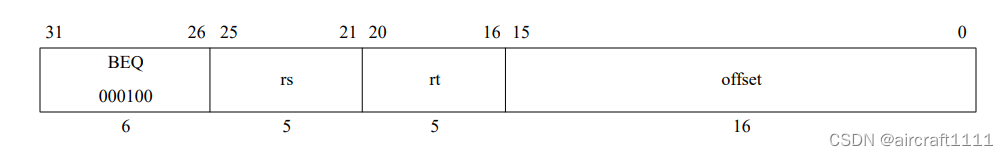

2.6 BEQ设计

BEQ rs, rt, offset

// e.g. BEQ $t0, $t1, 16

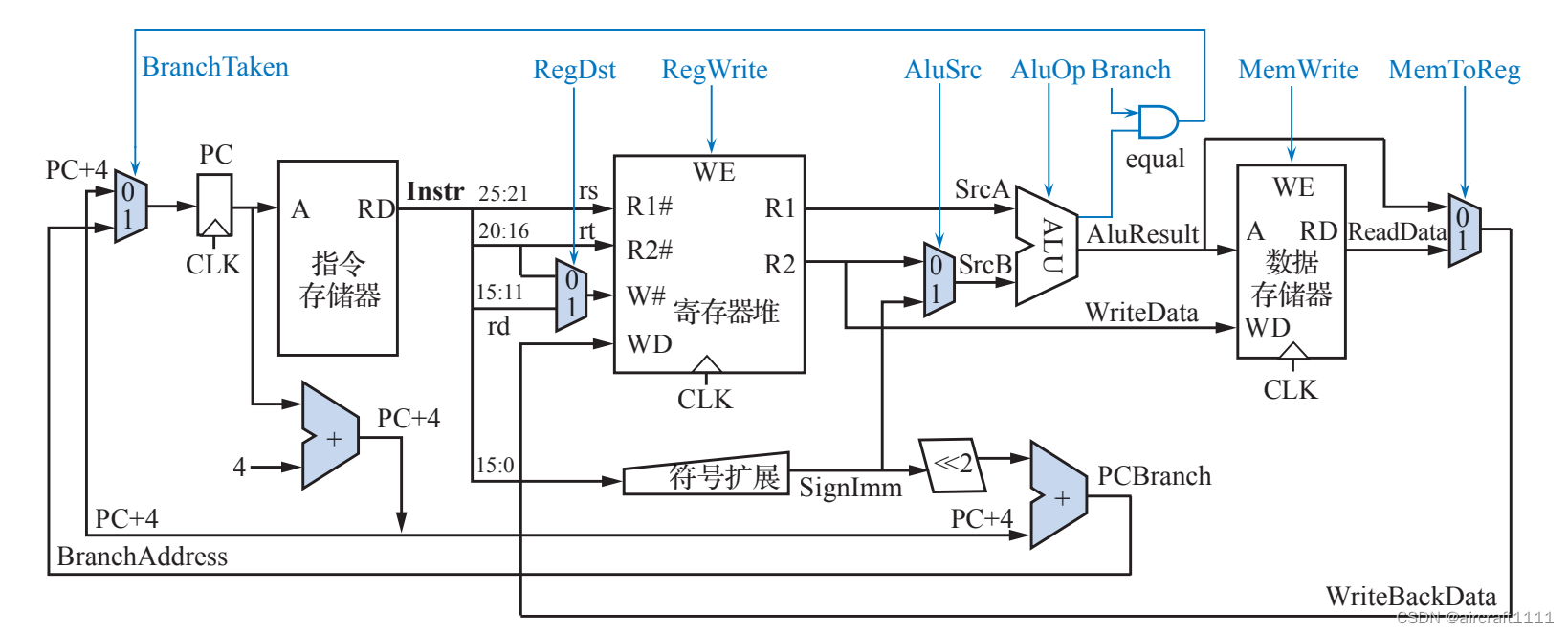

beq 指令用于比较两个寄存器的值是否相等,若相等则进行分支。指令字中的立即数字段为 16 位有符号数,是分支目标地址与顺序指令地址 PC+4 之间的字偏移,可正可负(既可向后跳转, 也可向前跳转)。由于指令长度为 4 字节,因此需要将 16 位立即数符号扩展成 32 位后并左移两 位生成 32 位字节偏移量,再加上顺序指令地址 PC+4 才能得到分支目标地址。为了避免资源冲突, 这里需要单独设置一个加法器。当比较条件满足时,用分支目标地址修改 PC 的内容,即产生分 支跳转;反之将PC的值更新为PC+4,程序顺序执行。这里PC输入端也需要增设一个多路选择器, 用于选择顺序执行还是跳转执行。

🍌3 微操作定义

一下会基于CPU基本结构框架图与前面提到的MIPS寄存器来定义指令不同阶段的微操作。由于定义的五种指令均不存在间址周期,所以将指令执行周期设置为取指、取数、执行、访存、写回五个阶段。

同时会结合单周期 MIPS 处理器的数据通路来分析每条指令的实际情形下的具体执行过程。辅助理解位操作。

3.1 ADD指令的位操作定义

- 1 取指阶段:

| 微操作 | 描述 | 微命令 |

|---|---|---|

| ( P C ) → M A R (PC) → MAR (PC)→MAR | PC→Bus,Bus→MAR,取当前指令地址→MAR |

PCo,MARi |

| 1 → R 1 → R 1→R | 读主存 | MemR=1 |

| M ( M A R ) → M D R M(MAR)→MDR M(MAR)→MDR | 从MAR的地址中读取指令 |

MARo,MDRi |

| M D R → I R MDR → IR MDR→IR | 把指令送到IR |

MDRo,IRi |

| ( P C ) + 4 → P C (PC)+4 → PC (PC)+4→PC | PC+4 |

+4 |

- 2 取数阶段

| 微操作 | 描述 | 微命令 |

|---|---|---|

| R ( I R [ 21 25 ] ) ) → Y R(IR[21~25]))→Y R(IR[21 25]))→Y | 把rs寄存器中的加数先存到Y中 |

R(IR(21~25))o,Yi |

- 3 执行阶段

| 微操作 | 描述 | 微命令 |

|---|---|---|

| ( Y ) + R ( I R ( 16 20 ) ) → Z (Y)+R(IR(16~20))→Z (Y)+R(IR(16 20))→Z | 把(Y)与rt寄存器中的操作数求和并送入Z,其中rt寄存器中的操作数直接通过Bus送到ALU |

Yo,Ro,ALUi+,Zi |

- 4 写回阶段

| 微操作 | 描述 | 微命令 |

|---|---|---|

| ( Z ) → R ( I R ( 11 15 ) ) (Z)→R(IR(11~15)) (Z)→R(IR(11 15)) | 把暂存器Z中存储的运算结果写入目的寄存器rd中 |

Ri,Zo |

3.2 SUB指令的位操作定义

- 取指阶段

| 微操作 | 描述 | 微命令 |

|---|---|---|

| ( P C ) → M A R (PC) → MAR (PC)→MAR | PC→Bus,Bus→MAR,取当前指令地址→MAR |

PCo,MARi |

| 1 → R 1 → R 1→R | 读主存 | MemR=1 |

| M ( M A R ) → M D R M(MAR)→MDR M(MAR)→MDR | 从MAR的地址中读取指令 |

MARo,MDRi |

| M D R → I R MDR → IR MDR→IR | 把指令送到IR |

MDRo,IRi |

| ( P C ) + 4 → P C (PC)+4 → PC (PC)+4→PC | PC+4 |

+4 |

- 取数阶段

| 微操作 | 描述 | 微命令 |

|---|---|---|

| ( R ( I R [ 21 25 ] ) ) → Y (R(IR[21~25]))→Y (R(IR[21 25]))→Y | 把rs寄存器中的被减数数先存到Y中 |

R(IR(21~25))o,Yi |

- 执行阶段

| 微操作 | 描述 | 微命令 |

|---|---|---|

| ( Y ) − R ( I R ( 16 20 ) ) → Z (Y)-R(IR(16~20))→Z (Y)−R(IR(16 20))→Z | 把(Y)与rt寄存器中的操作数计算并送入Z,其中rt寄存器中的操作数直接通过Bus送到ALU |

Yo,Ro,ALUi“-”,Zi |

- 写回阶段

| 微操作 | 描述 | 微命令 |

|---|---|---|

| ( Z ) → R ( I R ( 11 15 ) ) (Z)→R(IR(11~15)) (Z)→R(IR(11 15)) | 把暂存器Z中存储的运算结果写入目的寄存器rd中 |

Ri,Z |

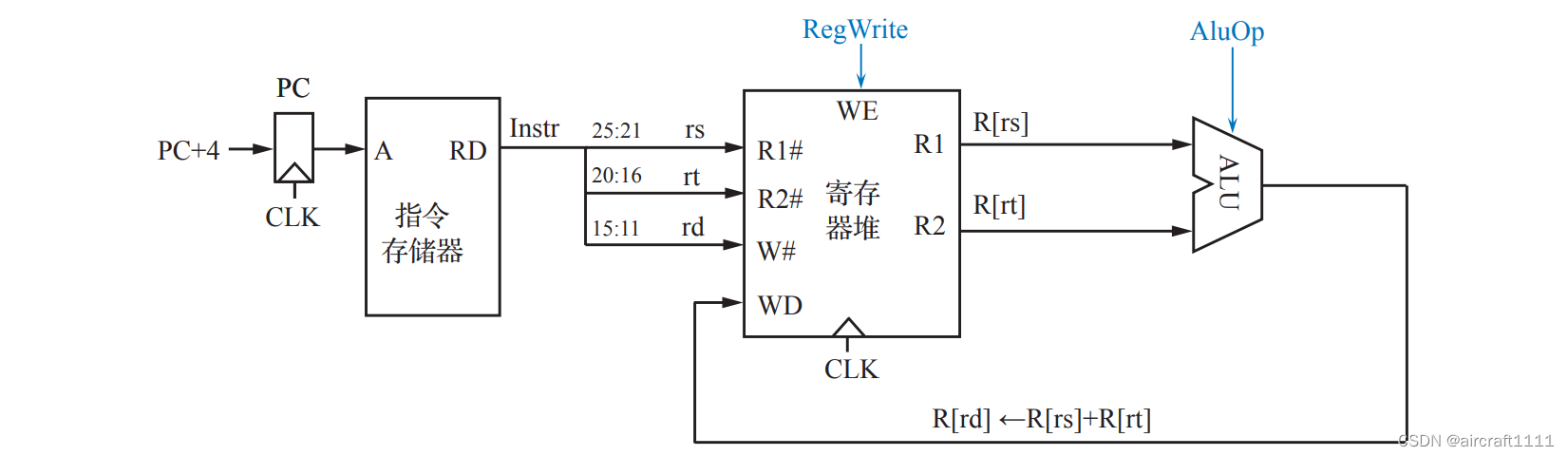

- R型指令的数据通路

指令执行过程中涉及的功能部件主要包括寄存器堆和 ALU。其只需将从指令存储器读出的指令字中的源寄存器字段 rs、rt 分别送入寄存器堆的两个读寄存器编号端 R1#、R2#,将目的 寄存器字段 rd 送入寄存器堆的写寄存器编号端 W#,将从寄存器堆读出的两个源寄存器的值经 R1、R2 端口输出到运算器;指令字中的 funct 字段决定 AluOp 控制 ALU 进行相应的运算(这里 应选择加法),运算结果被送入寄存器堆的写数据端口 WD,时钟上跳沿到来时会将运算结果写入目的寄存器 rd 中。

3.3 LW指令的位操作定义

- 取指阶段

| 微操作 | 描述 | 微命令 |

|---|---|---|

| ( P C ) → M A R (PC) → MAR (PC)→MAR | PC→Bus,Bus→MAR,取当前指令地址→MAR |

PCo,MARi |

| 1 → R 1 → R 1→R | 读主存 | MemR=1 |

| M ( M A R ) → M D R M(MAR)→MDR M(MAR)→MDR | 从MAR的地址中读取指令 |

MARo,MDRi |

| M D R → I R MDR → IR MDR→IR | 把指令送到IR |

MDRo,IRi |

| ( P C ) + 4 → P C (PC)+4 → PC (PC)+4→PC | PC+4 |

+4 |

- 取数阶段

| 微操作 | 描述 | 微命令 |

|---|---|---|

| ( R ( I R [ 21 25 ] ) ) → Y (R(IR[21~25]))→Y (R(IR[21 25]))→Y | 把rs寄存器中的地址先存到Y中 |

R(IR(21~25))o,Yi |

- 执行阶段

| 微操作 | 描述 | 微命令 |

|---|---|---|

| ( Y ) + E x t e n d e d ( I R ( 0 15 ) ) → Z (Y)+Extended(IR(0~15))→Z (Y)+Extended(IR(0 15))→Z | 把(Y)与offset偏移量求和并送入Z |

Yo,ALUi“+”,Zi |

- 访存阶段

| 微操作 | 描述 | 微命令 |

|---|---|---|

| ( Z ) → M A R 、 1 → R 、 M ( M A R ) → M D R (Z)→MAR、\\1→R、\\M(MAR)→MDR (Z)→MAR、1→R、M(MAR)→MDR | 把暂存器Z中存储的运算地址送到MAR并发出读命令,并取出该地址的数据存到MDR |

Zo,MARi,MemR=1,MDRi,MARo |

- 写回阶段

| 微操作 | 描述 | 微命令 |

|---|---|---|

| M D R → R ( I R ( 16 20 ) ) MDR→R(IR(16~20)) MDR→R(IR(16 20)) | 把MDR的数放入目标寄存器rt中 |

MDRo,Ri |

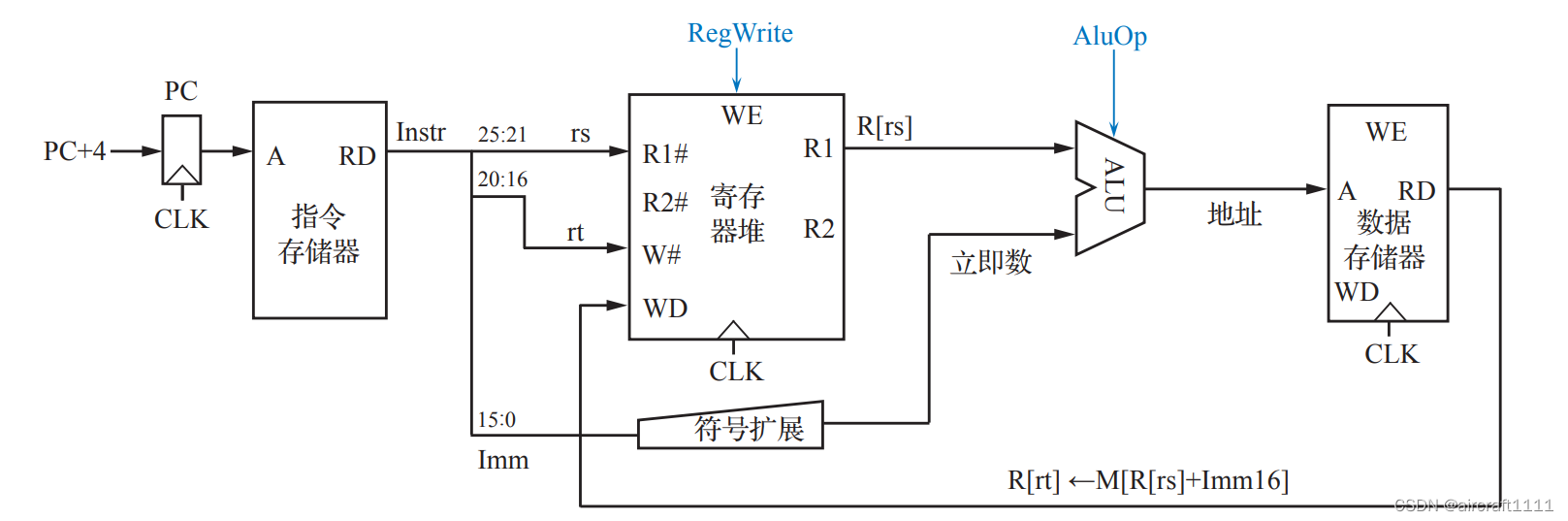

- LW指令的数据通路

lw 访存指令需要使用的操作数包括变址寄存器 rs、目的寄存器 rt 和 16 位地址偏移量 imm16,将指令字中的 rs 字段仍然送入寄存器堆的 R1# 端;将目的寄存器字段 rt 送入寄存器堆的 写寄存器编号端 W#;另外要将 16 位立即数 imm16 通过符号扩展单元转换成 32 位后送入 ALU, 与变址寄存器 rs 的值相加形成最终的访存地址后读取数据存储器中的数据并送入寄存器堆写数据 端口 WD。如图所示为 lw 指令操作的部分数据通路,其数据通路涉及的功能部件包括指令存储器、寄存器堆、符号扩展单元、ALU、数据存储器等,需要注意的是 lw 指令中 rt 字段变成了 目的寄存器。寄存器堆的写使能控制信号 RegWrite 应设置为 1,用于控制数据写回;AluOp 应 该设置为加法操作;而数据存储器写使能控制信号 WE 应该为 0,用于控制存储器进行读操作。

3.4 SW指令的位操作定义

- 取指阶段

| 微操作 | 描述 | 微命令 |

|---|---|---|

| ( P C ) → M A R (PC) → MAR (PC)→MAR | PC→Bus,Bus→MAR,取当前指令地址→MAR |

PCo,MARi |

| 1 → R 1 → R 1→R | 读主存 | MemR=1 |

| M ( M A R ) → M D R M(MAR)→MDR M(MAR)→MDR | 从MAR的地址中读取指令 |

MARo,MDRi |

| M D R → I R MDR → IR MDR→IR | 把指令送到IR |

MDRo,IRi |

| ( P C ) + 4 → P C (PC)+4 → PC (PC)+4→PC | PC+4 |

+4 |

- 取数阶段

| 微操作 | 描述 | 微命令 |

|---|---|---|

| ( R ( I R [ 21 25 ] ) ) → Y (R(IR[21~25]))→Y (R(IR[21 25]))→Y | 把rs寄存器中的地址先存到Y中 |

R(IR(21~25))o,Yi |

- 执行阶段

| 微操作 | 描述 | 微命令 |

|---|---|---|

| ( Y ) + E x t e n d e d ( I R ( 0 15 ) ) → Z (Y)+Extended(IR(0~15))→Z (Y)+Extended(IR(0 15))→Z | 把(Y)与offset偏移量求和并送入Z |

Yo,ALUi“+”,Zi |

- 访存阶段

| 微操作 | 描述 | 微命令 |

|---|---|---|

| ( Z ) → M A R 、 ( R ( I R [ 16 20 ] ) ) → M D R 、 1 → W 、 M D R → M ( M A R ) (Z)→MAR、\\(R(IR[16~20]))→MDR、\\1→W、\\MDR→M(MAR) (Z)→MAR、(R(IR[16 20]))→MDR、1→W、MDR→M(MAR) | 把Z中计算的地址送至MAR,并把rt寄存器中的数据送到MDR,把MDR的数据写入主存 |

Zo,MARi,Ro,MemW=1,MDRi,MDRo |

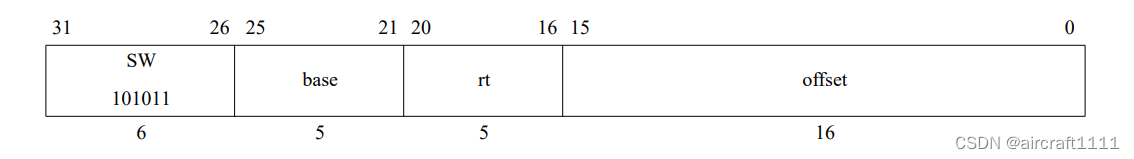

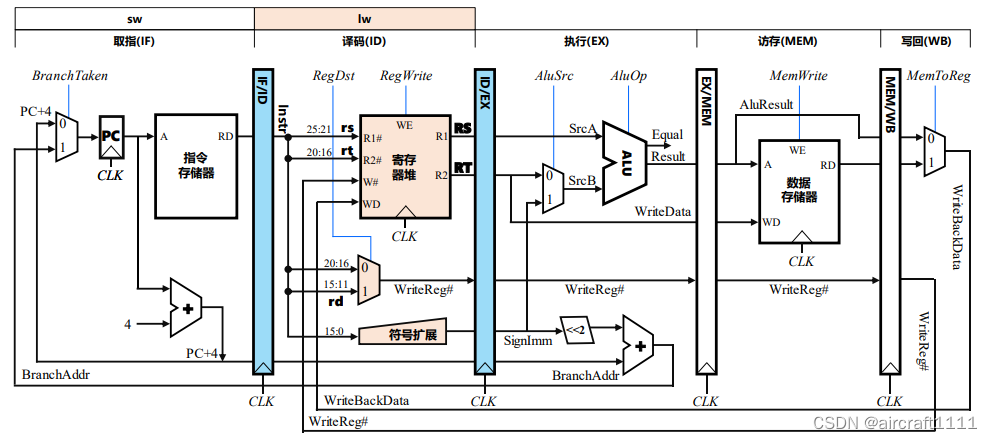

- SW指令的数据通路

sw 访存指令需要使用的操作数包括变址寄存器 rs、源寄存器 rt 和 16 位地址偏移量 imm16,将指令字中的 rs、rt 字段分别送入寄存器堆的 R1#、R2# 端;将 16 位立即数通过符号 扩展单元转换成 32 位后送入 ALU,与变址寄存器 rs 的值相加后形成最终的主存地址;将从寄 存器堆读出的 rt 寄存器的值送入数据存储器写数据端口 WD。如图所示为 sw 指令的数据通路。 寄存器堆不需要写入,所以 RegWrite 设置为 0;AluOp 应设置为加法操作;而数据存储器写使 能控制信号 MemWrite 应该为 1,用于控制存储器进行写操作。

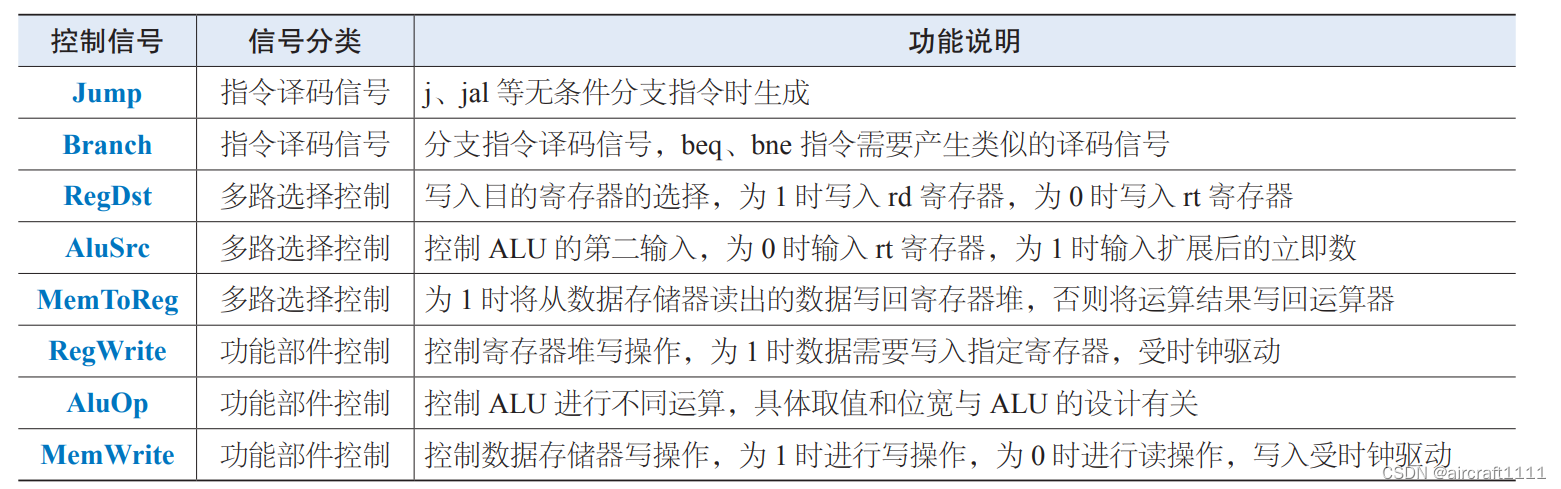

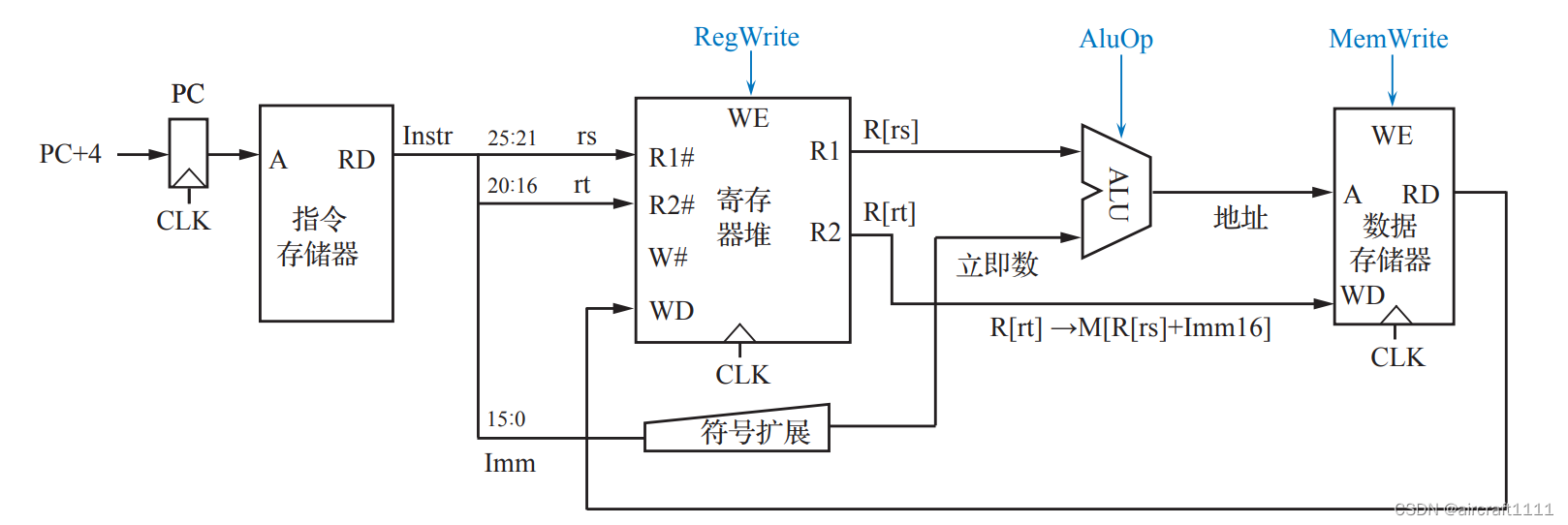

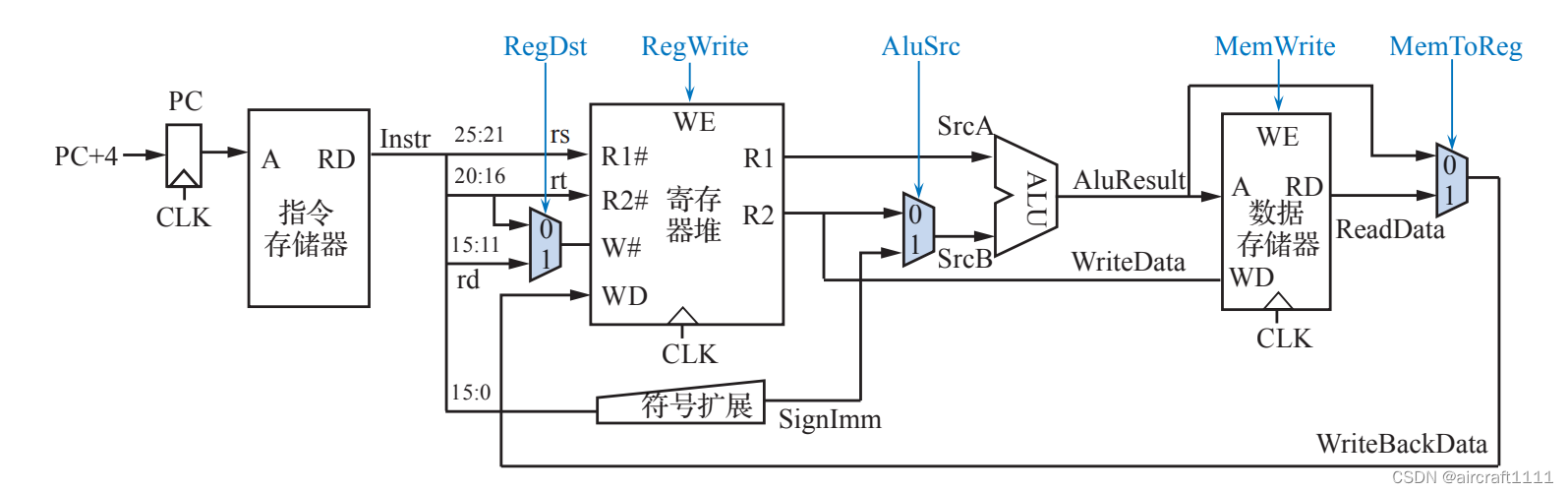

补充-混合型数据通路

- 支持 R 型运算指令和访存指令的混合数据通路

访存指令数据通路中寄存器堆写寄存器编号端口 W#、写数据端口 WD 的输入来源,ALU 第二个操作数的输入来源与 R 型运算类指令数据通路均不同。为了将不同的数据通路统一到同 一个电路中以支持两种不同类型的指令,可在有多个输入来源的端口处增加多路选择器,从而 得到如图所示的混合数据通路。

每增加一个多路选择器就会额外引入一个控制信号,这里分别增加了 RegDst、AluSrc、 MemToReg 三个控制信号。其中 RegDst 用于决定指令字中的 rt、rd 哪个字段作为目的寄存器进 行写入;AluSrc 用于从寄存器或立即数扩展值中选择一个操作数送入 ALU;MemToReg 用于从 ALU 的运算结果或主存访问数据中选择一路写回寄存器堆。通过设置这些控制信号的值就可以形成适合不同指令的数据通路,这些控制信 号都应该由操作控制器根据指令译码自动生成。

3.5 J指令的位操作定义

- 取指阶段

| 微操作 | 描述 | 微命令 |

|---|---|---|

| ( P C ) → M A R (PC) → MAR (PC)→MAR | PC→Bus,Bus→MAR,取当前指令地址→MAR |

PCo,MARi |

| 1 → R 1 → R 1→R | 读主存 | MemR=1 |

| M ( M A R ) → M D R M(MAR)→MDR M(MAR)→MDR | 从MAR的地址中读取指令 |

MARo,MDRi |

| M D R → I R MDR → IR MDR→IR | 把指令送到IR |

MDRo,IRi |

| ( P C ) + 4 → P C (PC)+4 → PC (PC)+4→PC | PC+4 |

+4 |

- 执行阶段

| 微操作 | 描述 | 微命令 |

|---|---|---|

| P C , I R [ 0 25 ] → P C {PC,IR[0~25]}→PC PC,IR[0 25]→PC | 计算得到跳转后的PC | PCi |

- 无条件跳转指令的数据通路

3.6 BEQ指令的位操作定义

- 有条件跳转指令的数据通路

条件分支指令是否发生分支跳转取决于两个操作数的比较情况,为此,条件分支指令数据通路需要同时完成计算分支目标地址和比较寄存器内容的工作。如图所示为 beq 指令的数据 通路。这里 beq 指令会译码生成条件分支指令译码信号 Branch,将其与 ALU 的运算结果标志 equal(两数相等)进行逻辑与后生成分支跳转信号 BranchTaken,BranchTaken 用于选择 PC 的 数据来源。

🫐4 微操作节拍的划分与微指令的确定

4.1 取指阶段微操作节拍划分与微指令的确定

在取指阶段各指令微操作格式相同

| 节拍 | 微操作 | 说明 |

|---|---|---|

| T0 | P C → M A R , 1 → R PC →MAR , 1 → R PC→MAR,1→R | 微指令1 |

| T1 | A d ( C M D R ) → C M A R Ad(CMDR) →CMAR Ad(CMDR)→CMAR | |

| T2 | M ( M A R ) → M D R , ( P C ) + 1 → P C M(MAR) → MDR , (PC)+1 → PC M(MAR)→MDR,(PC)+1→PC | 微指令2 |

| T3 | A d ( C M D R ) → C M A R Ad(CMDR) → CMAR Ad(CMDR)→CMAR | |

| T4 | M D R → I R , O P ( I R ) → MDR → IR , OP(IR) → MDR→IR,OP(IR)→ 微地址生成部件 | 微指令3 |

| T5 | 微地址生成部件 → C M A R → CMAR →CMAR 下地址 |

4.2 取数阶段微操作节拍划分与微指令的确定

| 节拍 | 微操作 | 说明 |

|---|---|---|

| T0 | ( R ( I R [ 21 25 ] ) ) → Y (R(IR[21~25]))→Y (R(IR[21 25]))→Y | 微指令4 |

| T1 | A d ( C M D R ) → C M A R Ad(CMDR) → CMAR Ad(CMDR)→CMAR |

4.3 执行阶段微操作节拍划分与微指令的确定

在执行(运算)阶段各指令微操作格式不同

- ADD指令

| 节拍 | 微操作 | 说明 |

|---|---|---|

| T0 | ( Y ) + R ( I R ( 16 20 ) ) → Z (Y)+R(IR(16~20))→Z (Y)+R(IR(16 20))→Z | 微指令5 |

| T1 | A d ( C M D R ) → C M A R Ad(CMDR) → CMAR Ad(CMDR)→CMAR |

- SUB指令

| 节拍 | 微操作 | 说明 |

|---|---|---|

| T0 | ( Y ) − R ( I R ( 16 20 ) ) → Z (Y)-R(IR(16~20))→Z (Y)−R(IR(16 20))→Z | 微指令6 |

| T1 | A d ( C M D R ) → C M A R Ad(CMDR) → CMAR Ad(CMDR)→CMAR |

- LW指令

| 节拍 | 微操作 | 说明 |

|---|---|---|

| T0 | ( Y ) + E x t e n d e d ( I R ( 0 15 ) ) → Z (Y)+Extended(IR(0~15))→Z (Y)+Extended(IR(0 15))→Z | 微指令7 |

| T1 | A d ( C M D R ) → C M A R Ad(CMDR) → CMAR Ad(CMDR)→CMAR |

- SW指令

| 节拍 | 微操作 | 说明 |

|---|---|---|

| T0 | ( Y ) + E x t e n d e d ( I R ( 0 15 ) ) → Z (Y)+Extended(IR(0~15))→Z (Y)+Extended(IR(0 15))→Z | 微指令7 |

| T1 | A d ( C M D R ) → C M A R Ad(CMDR)→CMAR Ad(CMDR)→CMAR |

- J指令

| 节拍 | 微操作 | 说明 |

|---|---|---|

| T0 | P C , I R [ 0 25 ] → P C {PC,IR[0~25]}→PC PC,IR[0 25]→PC | 微指令8 |

| T1 | A d ( C M D R ) → C M A R Ad(CMDR) → CMAR Ad(CMDR)→CMAR |

4.4 访存阶段微操作节拍划分与微指令的确定

- LW指令

| 节拍 | 微操作 | 说明 |

|---|---|---|

| T0 | ( Z ) → M A R , 1 → R (Z)→MAR,1→R (Z)→MAR,1→R | 微指令9 |

| T1 | A d ( C M D R ) → C M A R Ad(CMDR) → CMAR Ad(CMDR)→CMAR | |

| T2 | M ( M A R ) → M D R M(MAR) → MDR M(MAR)→MDR | 微指令10 |

| T3 | A d ( C M D R ) → C M A R Ad(CMDR) → CMAR Ad(CMDR)→CMAR |

- SW指令

| 节拍 | 微操作 | 说明 |

|---|---|---|

| T0 | ( Z ) → M A R , ( R ( I R [ 16 20 ] ) ) → M D R , 1 → W (Z)→MAR,\\(R(IR[16~20]))→MDR,\\1→W (Z)→MAR,(R(IR[16 20]))→MDR,1→W | 微指令11 |

| T1 | A d ( C M D R ) → C M A R Ad(CMDR) → CMAR Ad(CMDR)→CMAR | |

| T2 | M D R → M ( M A R ) MDR →M(MAR) MDR→M(MAR) | 微指令12 |

| T3 | A d ( C M D R ) → C M A R Ad(CMDR) → CMAR Ad(CMDR)→CMAR |

4.5 写回阶段微操作节拍划分与微指令的确定

- ADD指令

| 节拍 | 微操作 | 说明 |

|---|---|---|

| T0 | ( Z ) → R ( I R ( 11 15 ) ) (Z)→R(IR(11~15)) (Z)→R(IR(11 15)) | 微指令13 |

| T1 | Ad(CMDR) → CMAR |

- SUB指令

| 节拍 | 微操作 | 说明 |

|---|---|---|

| T0 | ( Z ) → R ( I R ( 11 15 ) ) (Z)→R(IR(11~15)) (Z)→R(IR(11 15)) | 微指令13 |

| T1 | A d ( C M D R ) → C M A R Ad(CMDR) → CMAR Ad(CMDR)→CMAR |

- LW指令

| 节拍 | 微操作 | 说明 |

|---|---|---|

| T0 | M D R → R ( I R ( 16 20 ) ) MDR→R(IR(16~20)) MDR→R(IR(16 20)) | 微指令14 |

| T1 | A d ( C M D R ) → C M A R Ad(CMDR) → CMAR Ad(CMDR)→CMAR |

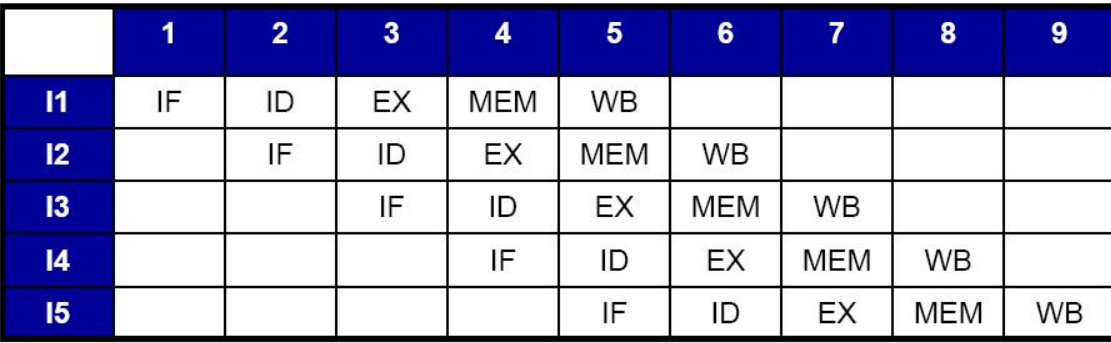

🥖5 处理器结构设计框图及功能描述

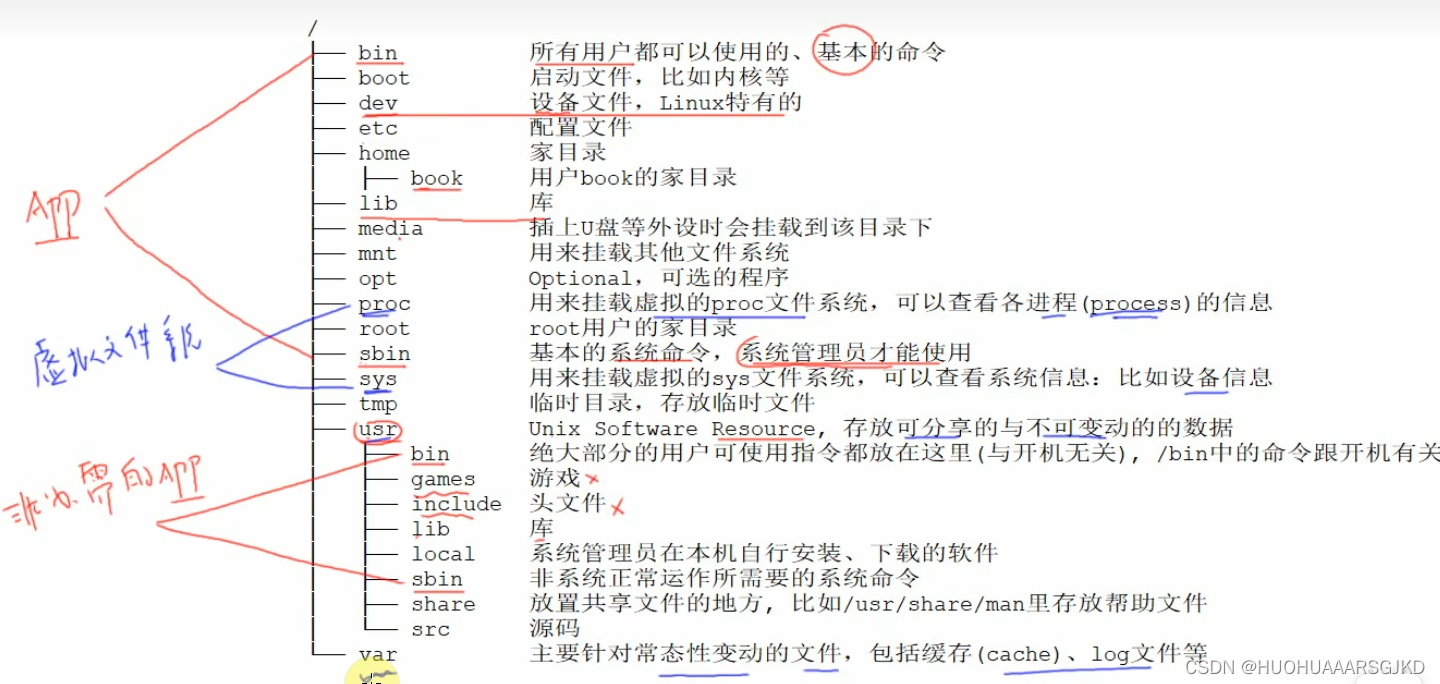

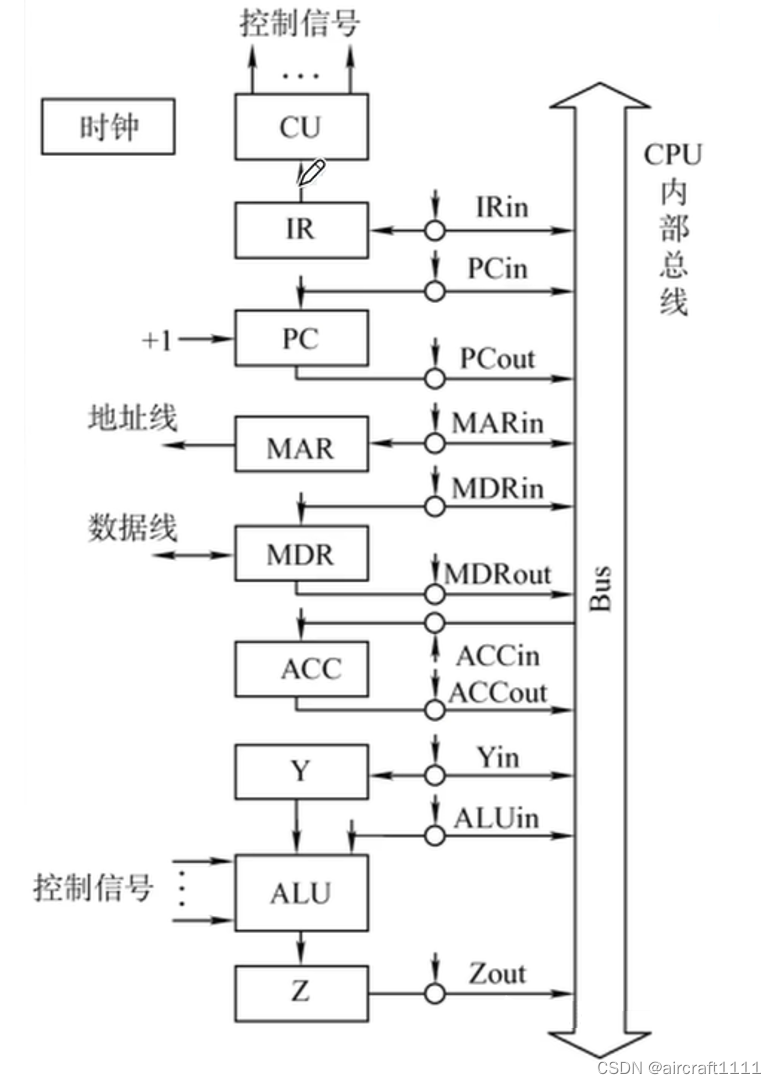

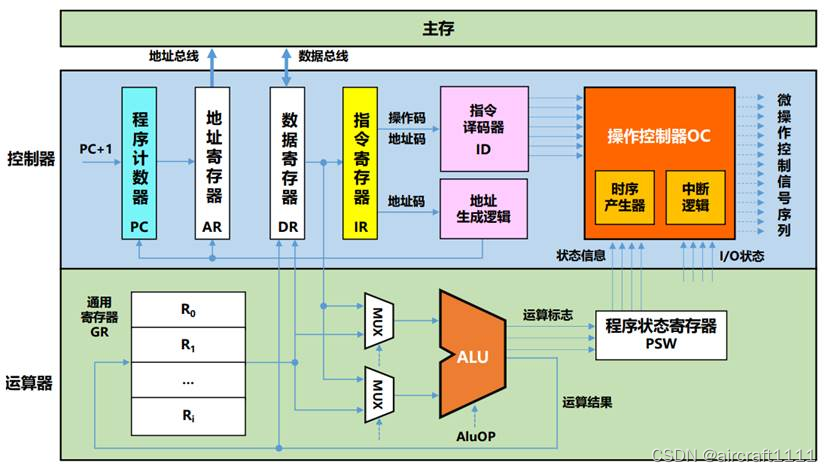

5.1 简单CPU模型

CPU(中央处理器)是计算机系统的核心部件,负责执行指令和处理数据。CPU包含许多重要的部分,每个部分都有特定的功能。

控制单元(Control Unit):控制单元是CPU的核心部分,负责控制整个计算机系统的运行。它从内存中读取指令,解码指令,调度执行,以确保指令按照正确的顺序和时间被执行。

算术逻辑单元(Arithmetic Logic Unit, ALU):ALU执行各种算术运算(如加法、减法、乘法、除法)和逻辑运算(如与、或、非)的操作。它从寄存器中获取数据进行计算,并将结果存回寄存器。

寄存器(Registers):寄存器是CPU内部的高速存储器件,用于临时存储指令、数据和地址。不同类型的寄存器包括:

- 程序计数器(Program Counter, PC):存储下一条要执行的指令的地址。

- 指令寄存器(Instruction Register, IR):存储当前正在执行的指令。

- 累加器(Accumulator):用于存储算术运算的结果。

- 数据寄存器(Data Registers):存储计算过程中的数据。

- 地址寄存器(Address Register):存储内存地址。

缓存(Cache):缓存是位于CPU和主内存之间的高速存储器,在存储器访问频繁的数据和指令,以提高数据访问速度。

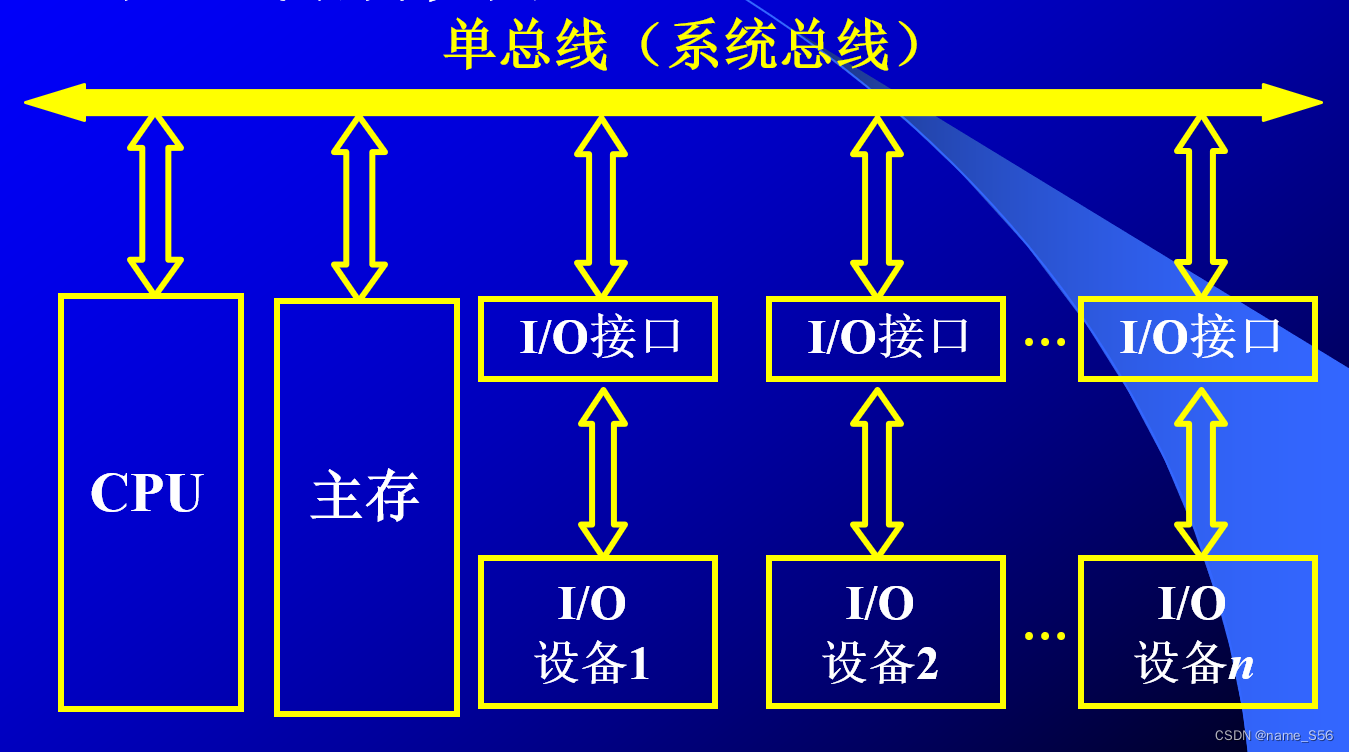

数据总线(Data Bus)和地址总线(Address Bus):数据总线用于传输数据,地址总线用于传输地址。它们是CPU和其他计算机组件之间进行通信的通道。

计时器(Timer):计时器用于控制CPU内部的时钟频率和执行指令的速度,以确保指令按照正确的顺序和时间被执行。

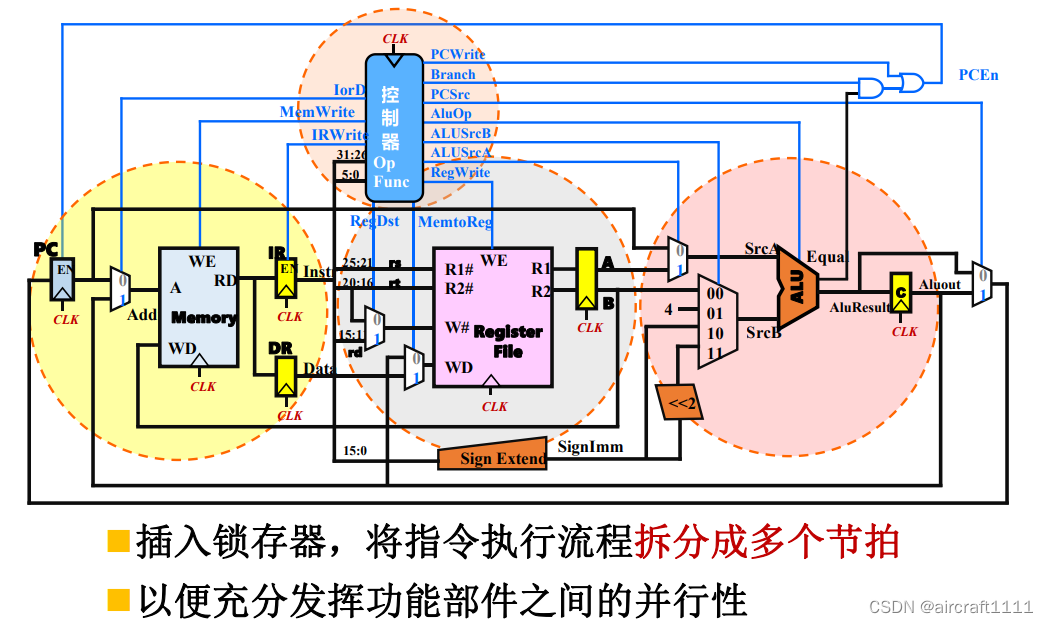

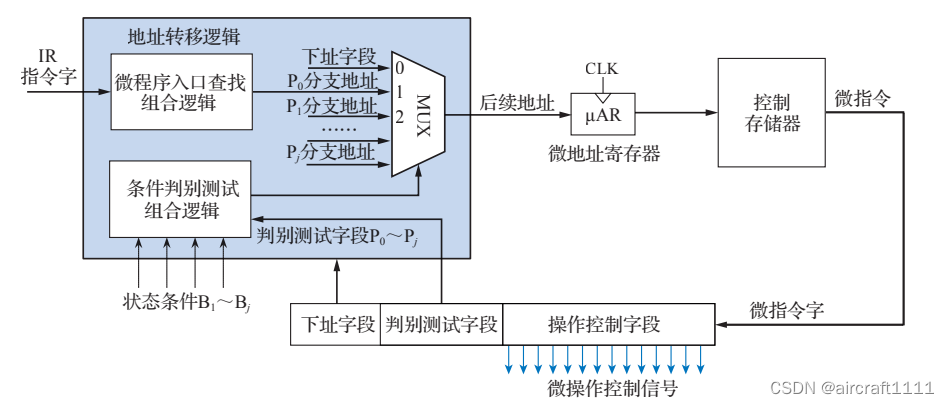

5.2 微程序控制器

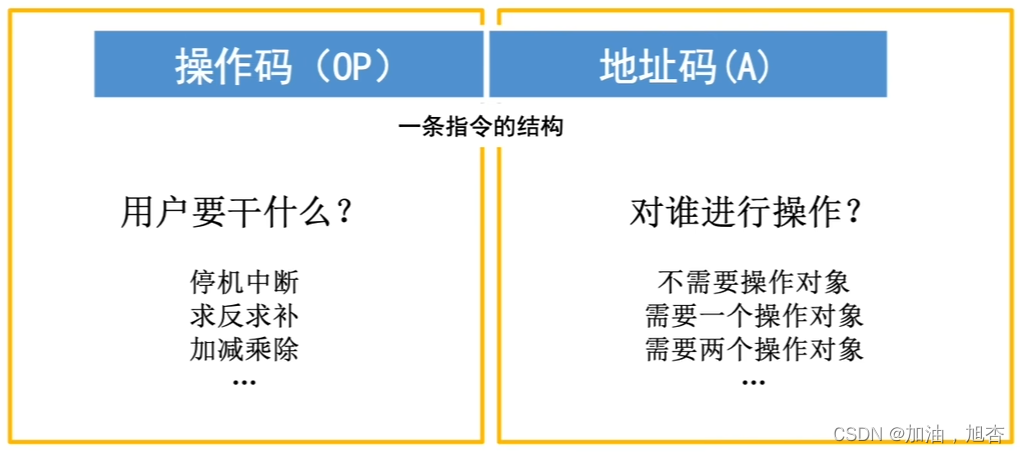

5.2.1基本概念

- 微命令与微操作:

控制部件向执行部件发出的各种控制命令称为微命令,执行部件收到微命令后所进行的操 作称为微操作。图 6.8 所示的由控制器产生的 PCin、PCout、IRin、RegDst、ADD、Rin、Rout 等控 制信号就属于微命令。收到微命令后,PC、IR、多路选择器、运算器、寄存器堆等执行部件会 执行相应的微操作,如 PC 写入新的地址、IR 接收新指令、多路选择器根据选择端的值选择对应 的输入输出等。

其中相容性微操作是指能同时或在同一个机器周期内并行执 行的微操作,不能在同一个机器周期并行执行的微操作就是互斥性微操作。

信号 Read、Write 就属于互斥性微操作,所有内总线的输出控制信号 PCout、DRout、Zout、DRout、 IR(A)out、IR(I)out、Rout 等都是互斥性微操作,运算器的运算控制信号 ADD、+4、SUB 等也属于 互斥性微操作;从总线向寄存器锁存数据的使能信号 PCin、ARin、IRin、Xin、Rin 等就属于相容性微操作。

- 微指令与微程序

在计算机的一个机器周期中,一组实现一定操作功能的相容性微命令称为微指令。这些微 命令组合产生的一组控制信号,控制执行相应的一组微操作,实现一条指令的部分功能。

微指令包括操作控制字段和顺序控制字段两部分。其中操作控制字段是主体,由若干微命 令位组成,每一位均对应表中的一个微操作控制信号,有多少个微操作控制信号,这里就对 应有多少个比特位;微指令是否含某个微命令,由对应位的状态 1 或 0 决定。微程序控制器向 执行部件发出的微命令就是通过微指令的操作控制字段发出的

实现一条指令功能的若干条微指令的集合称为微程序,微程序中多条微指令的先后关系由微指令格式中的顺序控制字段决定。

顺序控制字段包括判别测试字段和下址字段两部分。判别 测试字段(图中 P0 ~ P2)指出微指令执行过程中需要测试的外部条件,如是否要根据指令译码 进行微程序分支、进位、运算结果是否为零、是否是当前微程序的最后一条微指令等。下址字 段存放的是下条微指令的地址,位宽与微程序规模有关,最终是否按照该地址执行微程序与判 别测试结果有关。

5.2.2微程序控制器组成原理

- 控制存储器

控制存储器用于存放全部指令的所有微程序。控制存储器的字长等于微指令的长度,其存 储容量取决于指令系统,即等于所有指令的微程序包含的微指令数量。从控制存储器中取出的 数据就是微指令字,微指令字包括操作控制字段、判别测试字段、下址字段 3 部分。操作控制 字段经控制存储器取出后通过控制总线传输到所有执行部件的控点,控制相应部件进行适当的 微操作;判别测试字段用于实现地址逻辑转移;下址字段用于指示即将访问的下一条微指令的 地址。注意图中下方给出的微指令字只是用来表示指令格式的,并不是一个寄存器部件,它用 于表示微指令字中不同字段送往不同部件

- 微地址

微地址寄存器 μAR 为控制存储器提供微指令地址,初始化时为 0,所以控制存储器 0 号单 元应该为取指令微程序的第一条微指令,这样系统上电复位时计算机就可以访问控制存储器中的 取指微程序并开始取指令的操作。μAR 输入来源为地址转移逻辑的输出。它靠时钟控制其地址 更新,每一次时钟控制端的触发都会重新锁存新的微地址,从而取出并执行下一条微指令。在 三级时序中,这个时钟控制端应在机器周期的最后一个节拍结束时触发;在现代时序中这个时 钟控制端应该在当前时钟周期结束时触发。如果 CPU 中需要时序配合的控制信号是上跳沿有效, 那么这里的时钟控制端就应该是下跳沿触发。

- 地址转移逻辑

地址转移逻辑用于产生后续地址(下一条微指令的地址)。地址转移逻辑根据指令字的译 码情况、外部状态条件、微指令判别测试字段、下址字段等共同决定微地址寄存器的输入,生 成后续微指令的地址并送入 μAR,时钟触发到来时 μAR 更新为后续地址的值。后续微指令地址 形成常用的方法有下址字段法和计数器法。

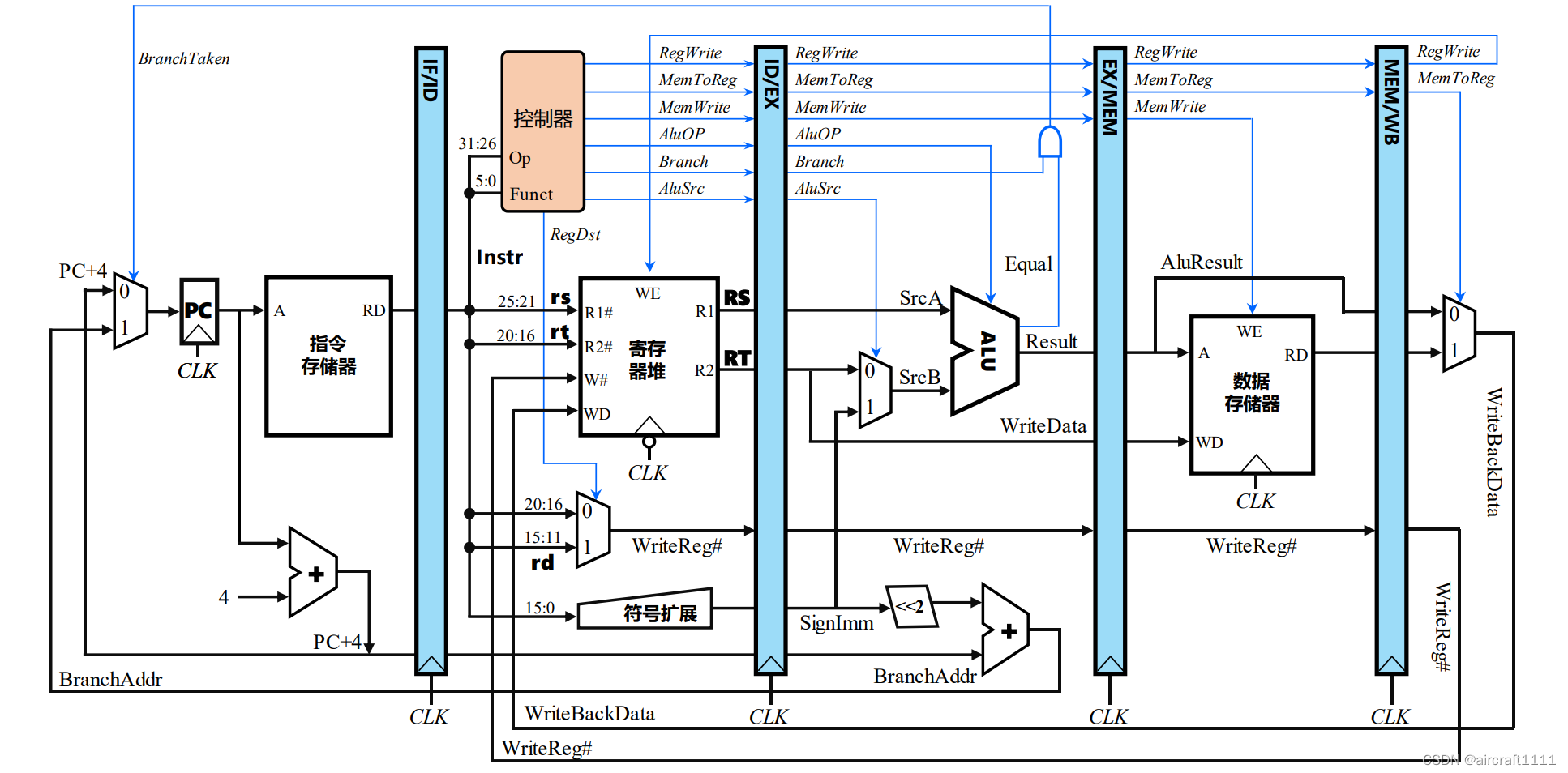

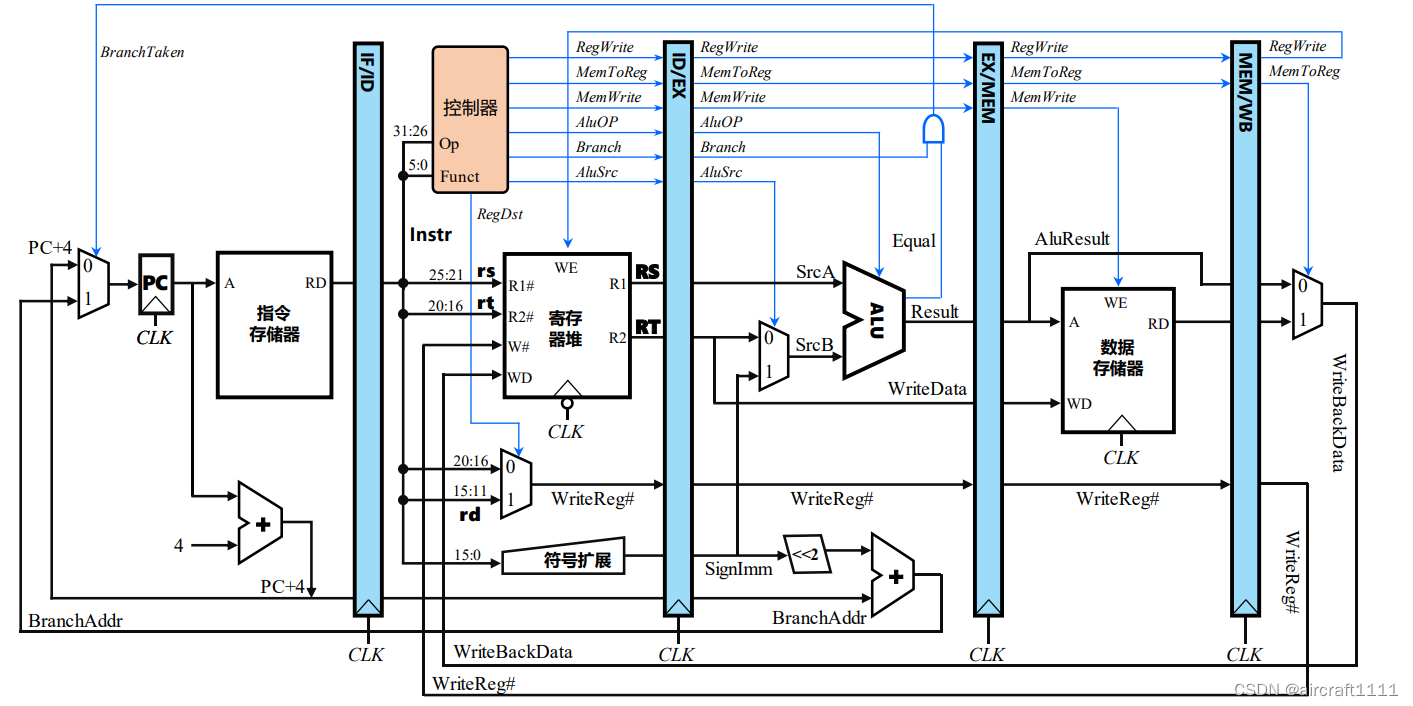

5.3 MIPS处理器的流水线设计方案

- 取指令

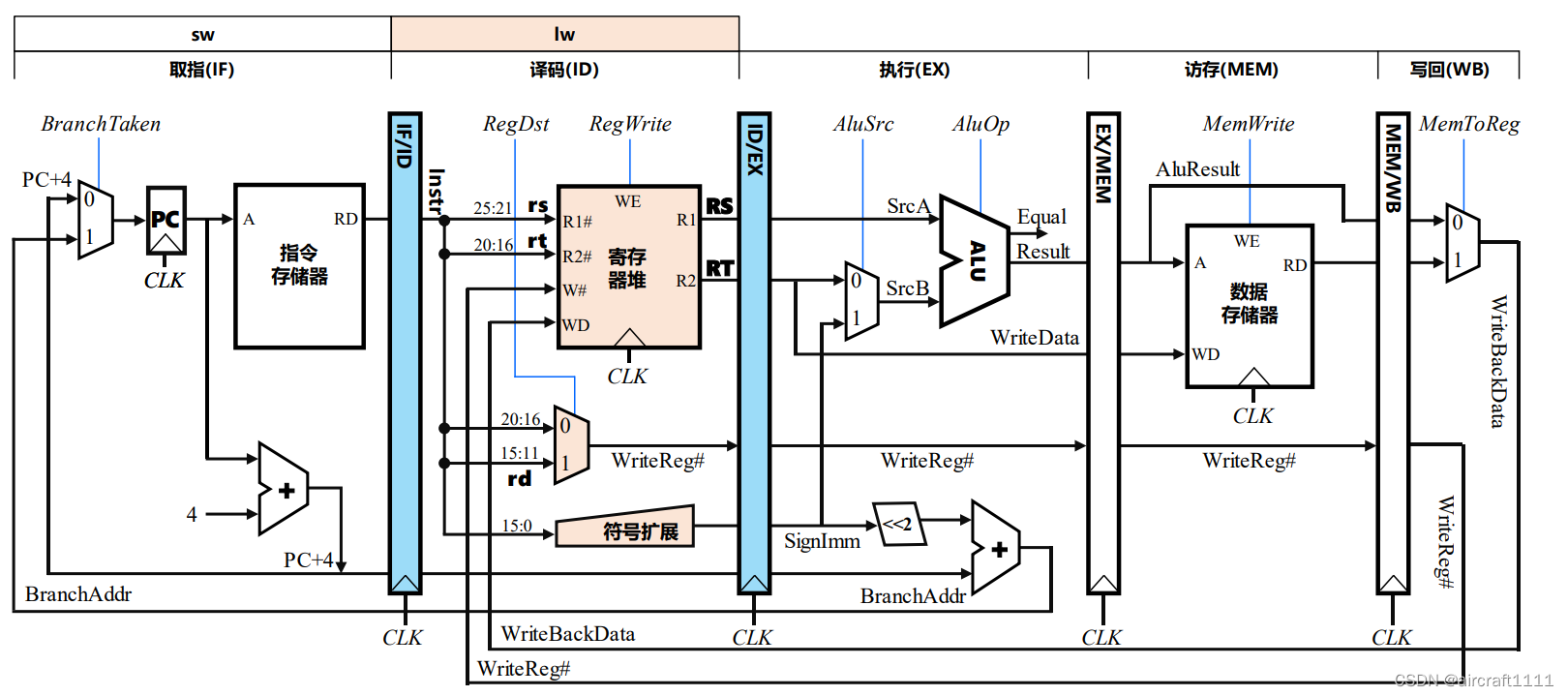

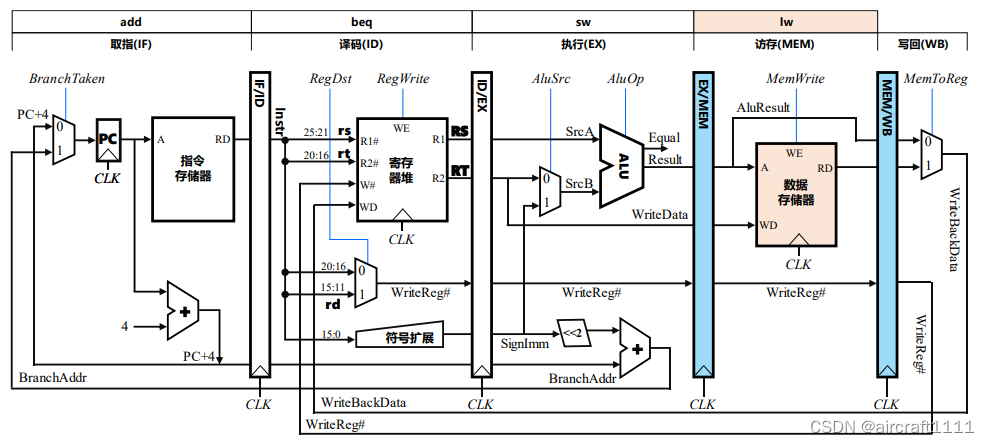

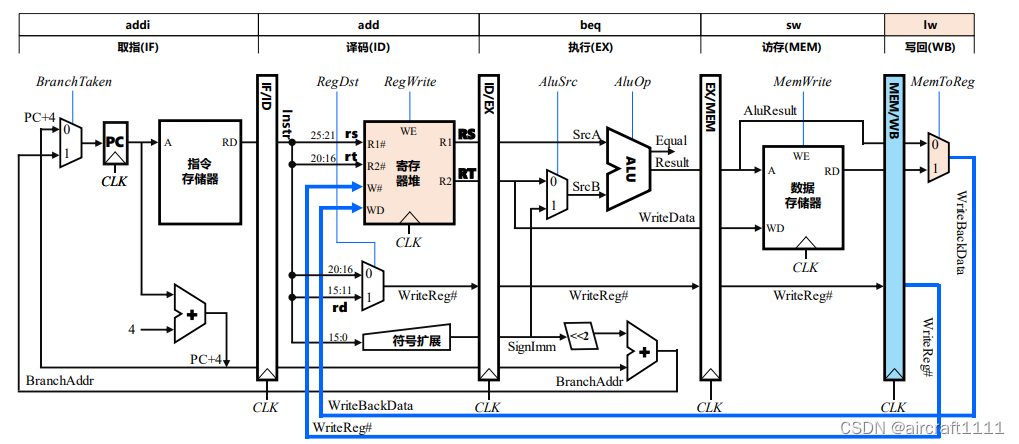

如图:程序第一条指令 lw 指令进入 IF 段取指令的示意图,lw 指令在当前时钟节拍所使用的数据通路用深色表示,lw 指令字由程序计数器 PC 提供的地址访问指 令存储器得到,并将指令存储器 RD 输出端的 lw 指令字送 IF/ID 流水寄存器输入端;另外 程序计数器 PC 的值与 4 相加形成顺序指令地址 PC+4,送 PC 输入端以便下一个时钟周期 可以取出下一条指令。注意虽然 lw 指令在后续功能段并不会使用 PC+4,但 PC+4 还是会 传送给 IF/ID 流水寄存器,以备其他指令(如 beq)使用。流水线各功能段并不区分指令的 功能,所有数据信息和操作控制信号都来自段首的流水寄存器输出,所以只要是后续功能 段有可能要用到的数据和控制信号都要向后传递。时钟到来时指令字将锁存在 IF/ID 流水 寄存器中,同时 PC 更新为 PC+4 的值,lw 指令进入 ID 段,同时 IF 段取出下一条指令 sw。

- 指令译码、取操作数

如图: lw 指令进入 ID 段译码的示意图,具体数据通路用 深色表示,ID 段由操作控制器根据 IF/ID 流水寄存器中的指令字生成以后各段所需要的操 作控制信号并向后传输,具体见图 7.8;另外 ID 段还会根据指令字中的 rs、rt 字段读取寄 存器堆中的 rs 和 rt 寄存器的值 RS、RT;符号扩展单元会将指令字中的 16 位立即数符号扩 展为 32 位;多路选择器根据指令字生成指令可能的写寄存器编号 WriteReg#(有些指令并不需要写寄存器)。这 4 个数据连同顺序指令地址 PC+4 一起传输给 ID/EX 流水寄存器,时 钟到来时这些数据信息连同操作控制器产生的操作控制信号都会锁存在 ID/EX 流水寄存器 中,lw 指令进入 EX 段,同时 sw 指令进入 ID 段、beq 指令进入 IF 段。

- 执行或访存地址运算:

如图:lw 指令进入 EX 段的示意图,具体数据通路用深 色表示。对于 lw 指令来说,EX 段主要用于计算访存地址,将 ID/EX 流水寄存器中的 RS 的值与符号扩展后的立即数相加得到访存地址送 EX/MEM 流水寄存器;如果是 beq 指令 EX 段还需要计算分支目标地址,生成分支跳转信号 BranchTaken。ID/EX 流水寄存器中 RT 的值会在 MEM 段作为写入数据使用,所以 RT 的值会作为写入数据 WriteData 送 EX/MEM 流水寄存器;另外 ID/EX 流水寄存器中的写寄存器编号 WriteReg#也将直接传送给 EX/MEM 流水寄存器。同样时钟到来后这些数据信息连同后段所需要的操作控制信号都会锁存在 EX/MEM 流水接口中的寄存器中,lw 指令进入 MEM 段,sw、beq、add 指令分别进入 EX、 ID、IF 段。

- 存储器访问

如图:为 lw 指令进入 MEM 段的示意图,具体数据通路用深色表示。 该阶段功能比较单一,主要根据 EX/MEM 流水寄存器中锁存的 ALU 运算结果—访存地址 和写入数据对于存储器进行读或写操作,EX/MEM 流水寄存器中的 ALU 运算结果、 WriteReg#、数据存储器读出的数据都会送 MEM/WB 流水寄存器输入端,同样时钟到来后 这些数据信息连同后段所需要的操作控制信号都会锁存在 MEM/WB 流水寄存器中,lw 指 令进入 WB 段,sw、beq、add、addi 指令分别进入 MEM、EX、ID、IF 段,此时指令流水线充满。

- 结果写回

如图:为 lw 指令进入 WB 段的示意图,具体数据通路用深色表示。 WB 段从 MEM/WB 流水寄存器中选择 ALU 运算结果或内存访问数据写回到寄存器堆指定 寄存器 WriteReg#中,时钟到来时寄存器堆会完成数据写入,lw 指令离开流水线。注意此 时 sw 指令也进入了最后阶段 MEM 段,同时 beq 指令也进入了最后阶段 EX 段,同一时刻 实际上有 3 条指令执行完毕,当然这些指令即使执行完成也需要在流水线中继续向后传递 直至 WB 段。

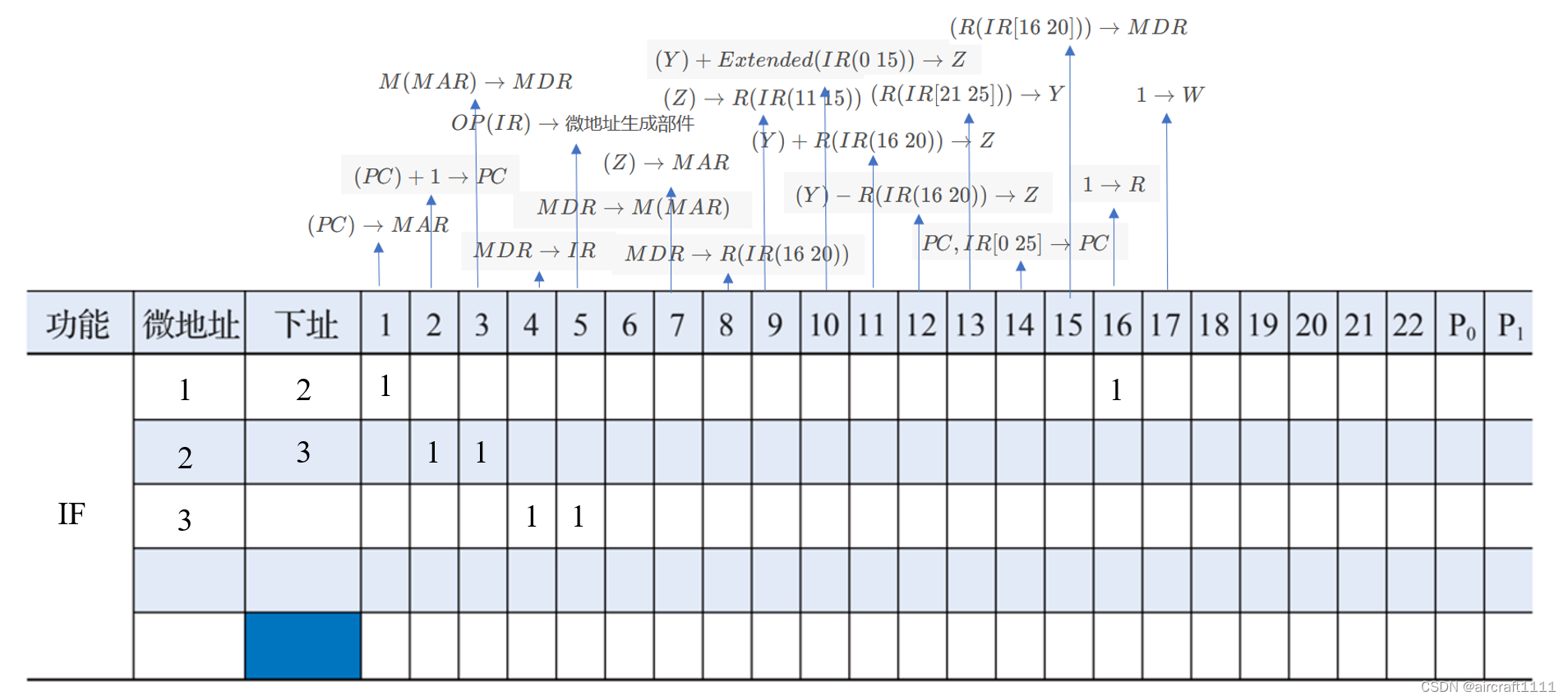

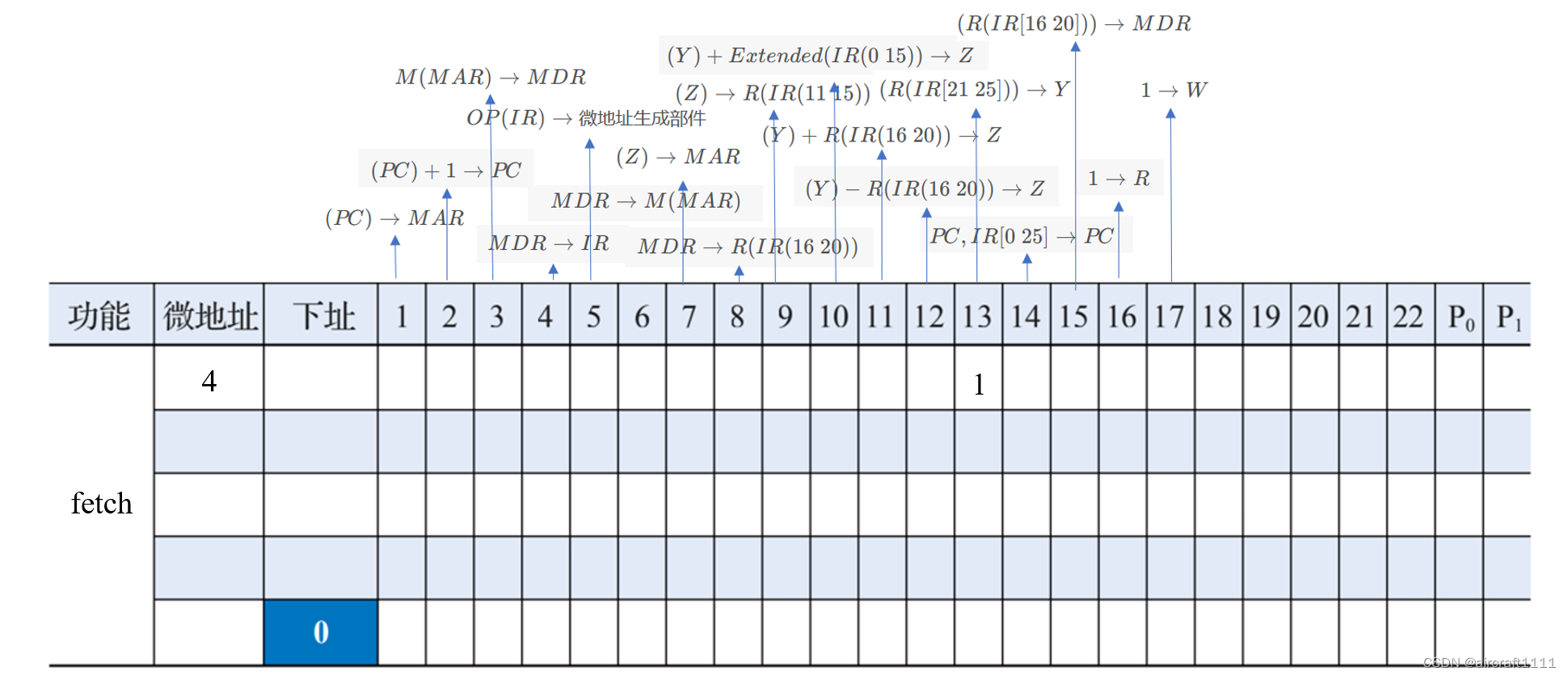

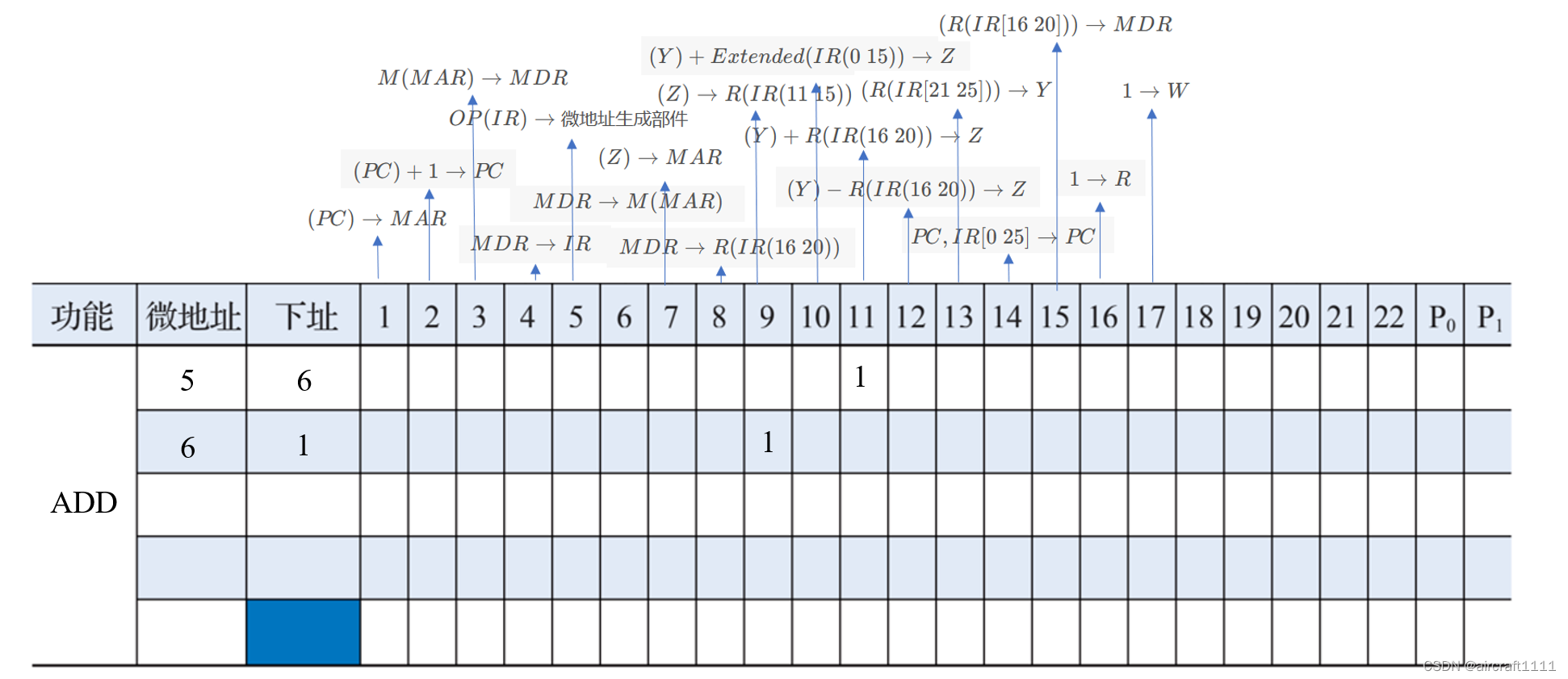

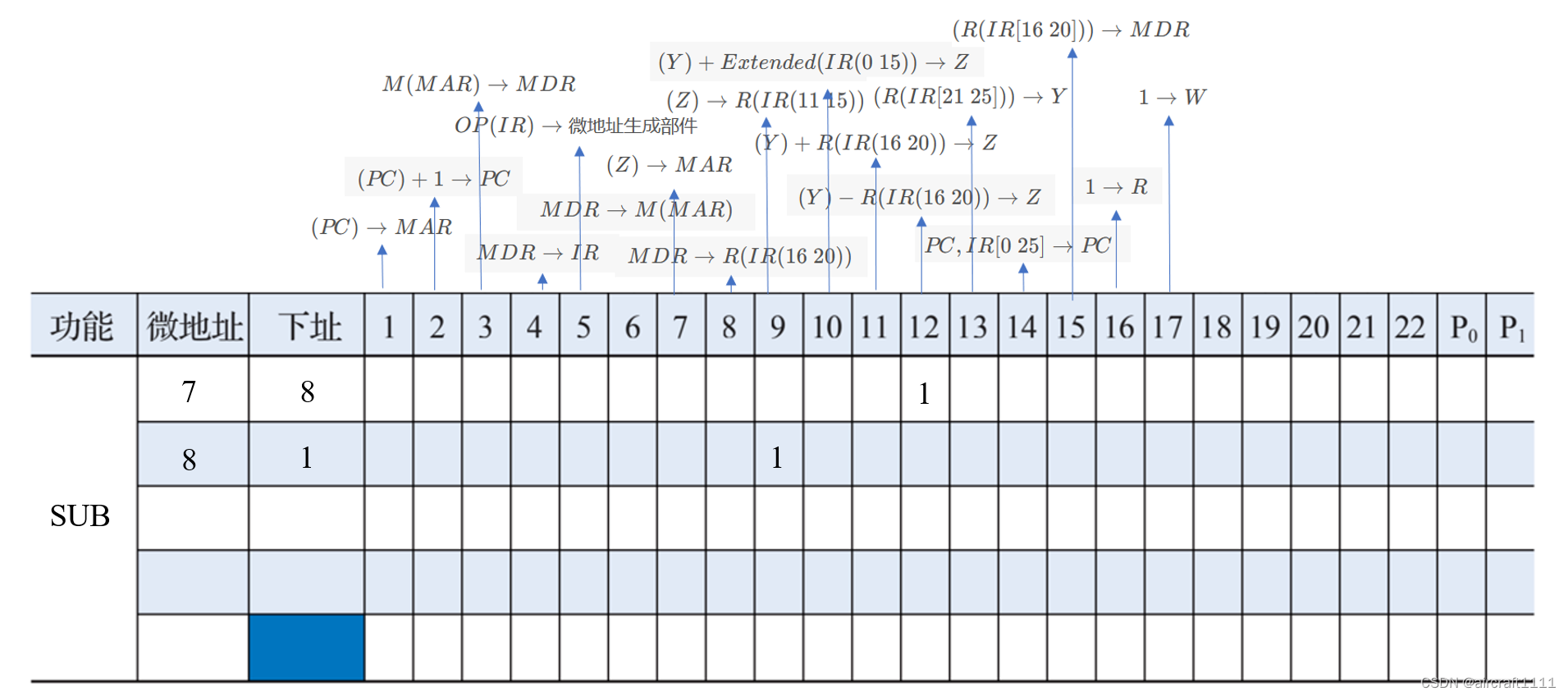

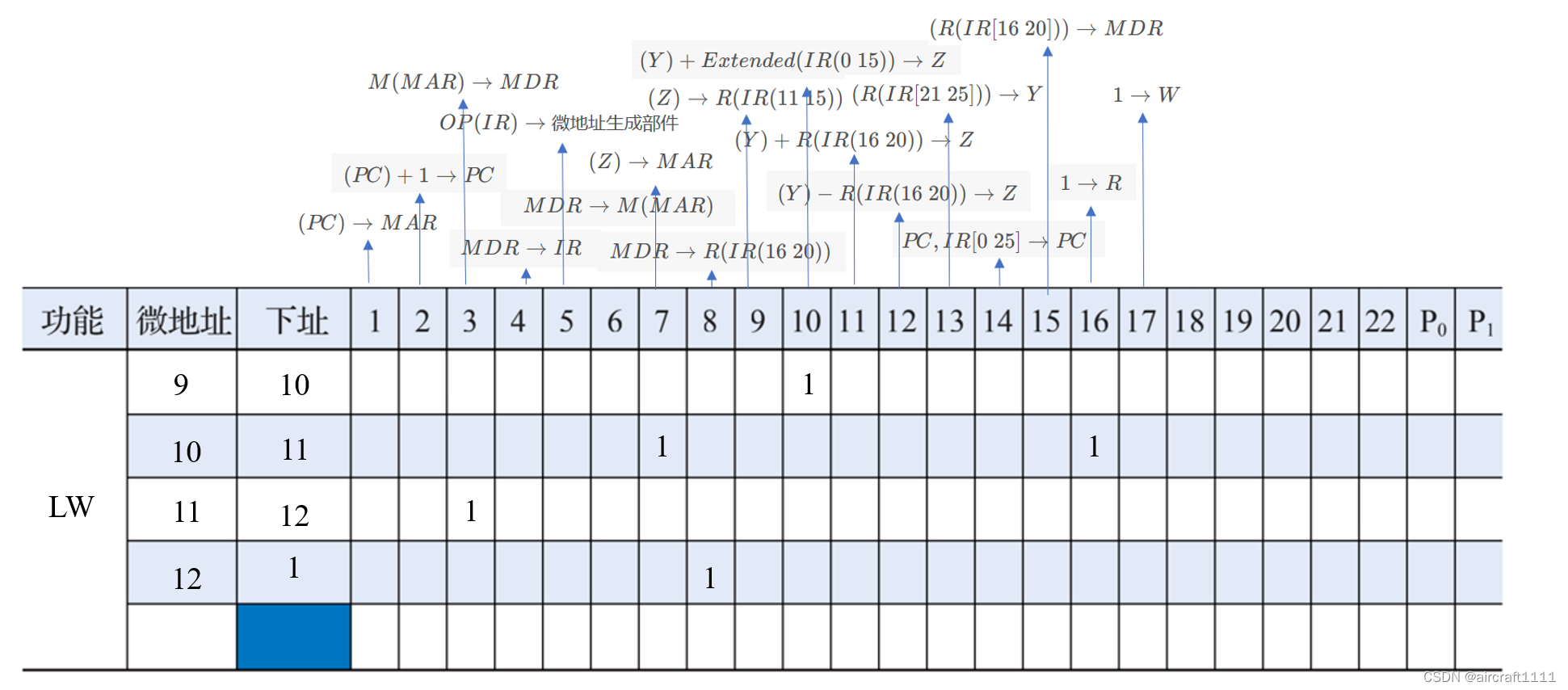

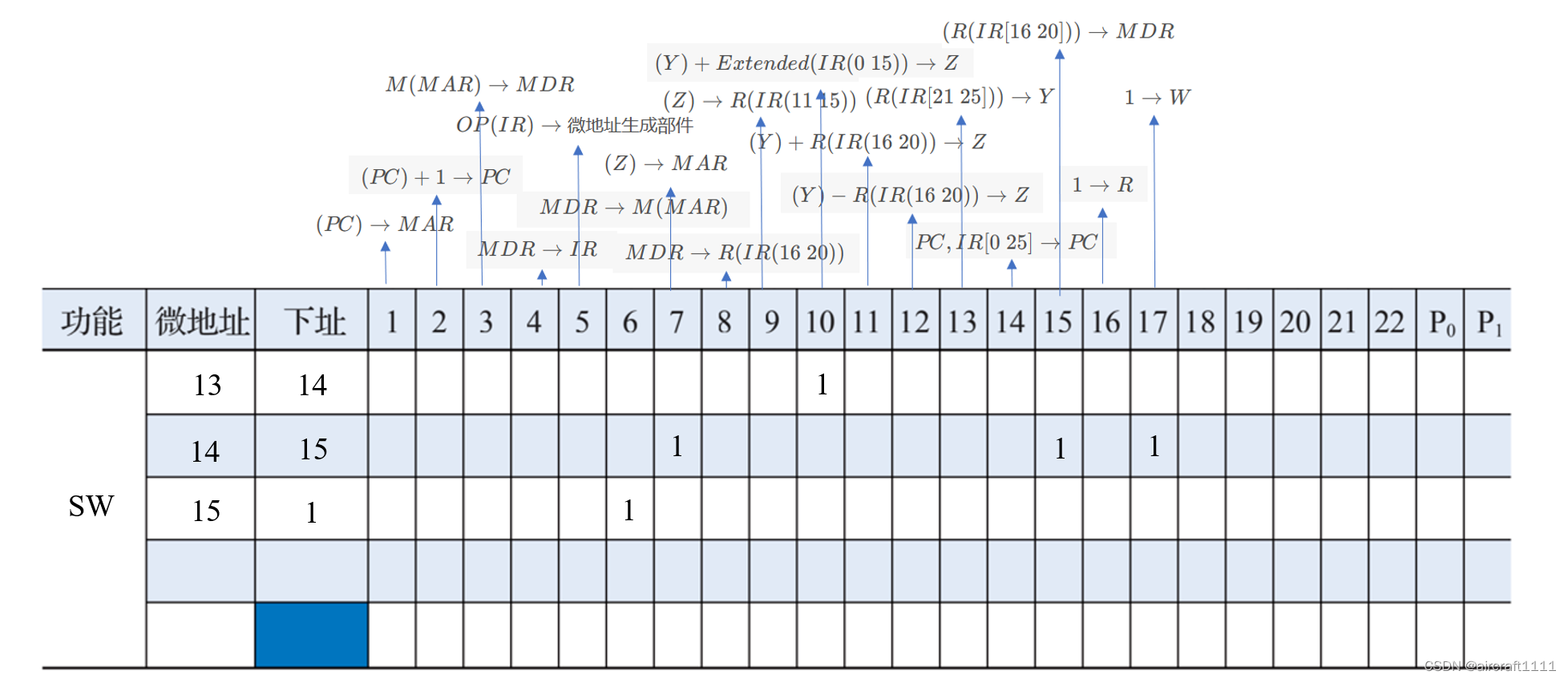

🥕 6 微程序设计

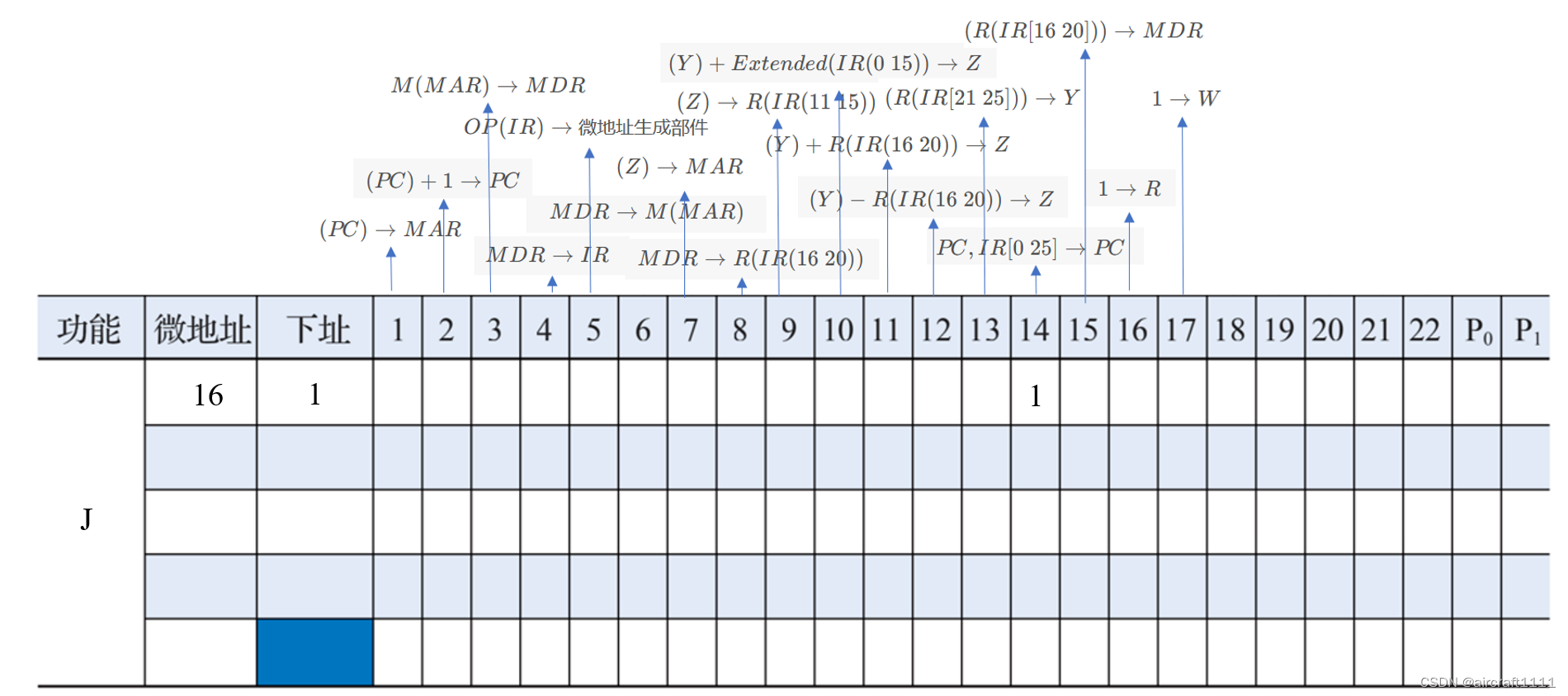

微命令编码方法:因为一共采用了17个微操作,故种类较少,采用直接编码的方式。

直接表示法:直接表示法的基本思想是:将微指令操作控制字段的每个二进制位定义为一个微命令,用“1”或“0”表示相应的微命令的“有”或“无”;一条微指令从控制存储器中取出时,它所包含的微命令可直接用于控制数据通路中的执行部件。这种方法的优点是简单、微操作的并行能力强、操作速度快;缺点是微指令过长,一般来说,有多少个微命令,微指令的操作控制字段就需要多少位。较为复杂的计算机系统微命令可能有上百个,此时就需要采用其他方法来缩短微指令字。

6.1 控制字段

因为一共采用了17个微操作,故种类较少,采用直接编码方式。

| 比特位的位置(从左向右) | 微操作 |

|---|---|

| 1 | ( P C ) → M A R (PC)→MAR (PC)→MAR |

| 2 | ( P C ) + 1 → P C (PC)+1 → PC (PC)+1→PC |

| 3 | M ( M A R ) → M D R M(MAR) → MDR M(MAR)→MDR |

| 4 | M D R → I R MDR → IR MDR→IR |

| 5 | O P ( I R ) → OP(IR) → OP(IR)→ 微地址生成部件 |

| 6 | M D R → M ( M A R ) MDR →M(MAR) MDR→M(MAR) |

| 7 | ( Z ) → M A R (Z)→MAR (Z)→MAR |

| 8 | M D R → R ( I R ( 16 20 ) ) MDR→R(IR(16~20)) MDR→R(IR(16 20)) |

| 9 | ( Z ) → R ( I R ( 11 15 ) ) (Z)→R(IR(11~15)) (Z)→R(IR(11 15)) |

| 10 | ( Y ) + E x t e n d e d ( I R ( 0 15 ) ) → Z (Y)+Extended(IR(0~15))→Z (Y)+Extended(IR(0 15))→Z |

| 11 | ( Y ) + R ( I R ( 16 20 ) ) → Z (Y)+R(IR(16~20))→Z (Y)+R(IR(16 20))→Z |

| 12 | ( Y ) − R ( I R ( 16 20 ) ) → Z (Y)-R(IR(16~20))→Z (Y)−R(IR(16 20))→Z |

| 13 | ( R ( I R [ 21 25 ] ) ) → Y (R(IR[21~25]))→Y (R(IR[21 25]))→Y |

| 14 | P C , I R [ 0 25 ] → P C {PC,IR[0~25]}→PC PC,IR[0 25]→PC |

| 15 | ( R ( I R [ 16 20 ] ) ) → M D R (R(IR[16~20]))→MDR (R(IR[16 20]))→MDR |

| 16 | 1 → R 1→R 1→R |

| 17 | 1 → W 1→W 1→W |

6.2 下地址字段与微指令序列的确定

本次设计32位MIPS模型机微指令

考虑到有17个微操作,可以设计操作控制字段22位,顺序控制之端10位包括3位判别测试位和7位下地址字段。

- 取指阶段

| 微指令序号 | 操作控制 | 下地址 |

|---|---|---|

| 1(0000) | 1000 0000 0000 0001 0 | 0001 |

| 2(0001) | 0110 0000 0000 0000 0 | 0010 |

| 3(0010) | 0001 1000 0000 0000 0 | 0011(有可能跳转) |

- 取数阶段

| 微指令序号 | 操作控制 | 下地址 |

|---|---|---|

| 4(0011) | 0000 0000 0000 1000 0 | 0100(有可能跳转) |

- ADD指令

| 微指令序号 | 操作控制 | 下地址 |

|---|---|---|

| 5(0100) | 0000 0000 0010 0000 0 | 0101 |

| 13(0101) | 0000 0000 1000 0000 0 | 0000 |

- SUB指令

| 微指令序号 | 操作控制 | 下地址 |

|---|---|---|

| 6(0110) | 0000 0000 0001 0000 0 | 0111 |

| 13(0111) | 0000 0000 1000 0000 0 | 0000 |

- LW指令

| 微指令序号 | 操作控制 | 下地址 |

|---|---|---|

| 7(1000) | 0000 0000 0100 0000 0 | 1001 |

| 9(1001) | 0000 0010 0000 0001 0 | 1010 |

| 10(1010) | 0010 0000 0000 0000 0 | 1011 |

| 14(1011) | 0000 0001 0000 0000 0 | 0000 |

- SW指令

| 微指令序号 | 操作控制 | 下地址 |

|---|---|---|

| 7(1100) | 0000 0000 0100 0000 0 | 1101 |

| 11(1101) | 0000 0010 0000 0010 1 | 1110 |

| 12(1110) | 0000 0100 0000 0000 0 | 0000 |

- J指令

| 微指令序号 | 操作控制 | 下地址 |

|---|---|---|

| 8(1111) | 0000 0000 0000 0100 0 | 0000 |