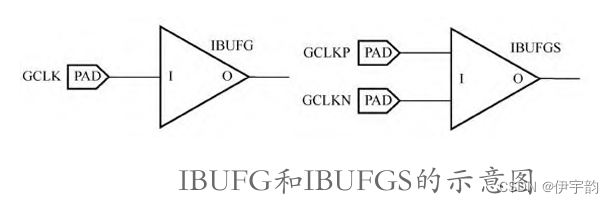

(1)时钟概述;时钟是具有周期性的脉冲信号,最常用的是占空比50%的方波。

(时钟相当于单片机的脉搏;STM32本身非常复杂,外设非常的多,为了保持低功耗工作,STM32 的主控默认不开启这些外设功能。用户可以根据自己的需要决定 STM32 芯片要使用的功能,这个功能开关在STM32主控中也就是各个外设的时钟)

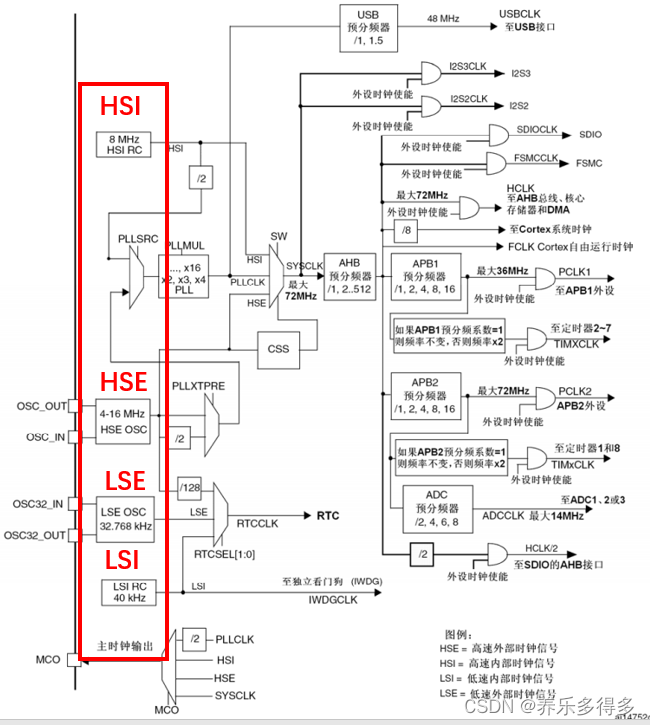

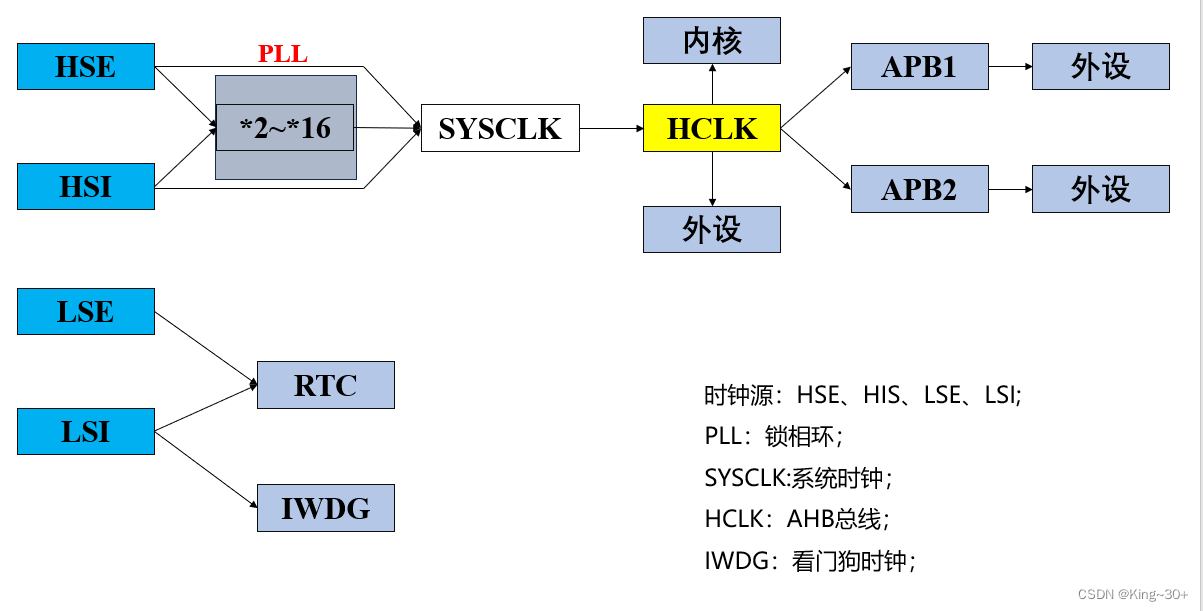

(2)时钟源;输入时钟源主要包括HSI、HSE、LSI、LSE。

2个外部时钟源: HSE (High Speed External)152 高速外部振荡器

外接石英/陶瓷谐振器,频率为4MHz-16MHz。常用是8MHz。

LSE (Low Speed External) 低速外部振荡器

外接32.768kHz石英晶体,主要作用于 RTC 的时钟源。

2个内部时钟源: HSI(High Speed Internal) 高速内部振荡器

由内部RC振荡器产生,频率8MHz。

LSI(Low Speed Internal) 低速内部振荡器

由内部RC振荡器产生,频率40kHz,可作独立看门狗时钟源。

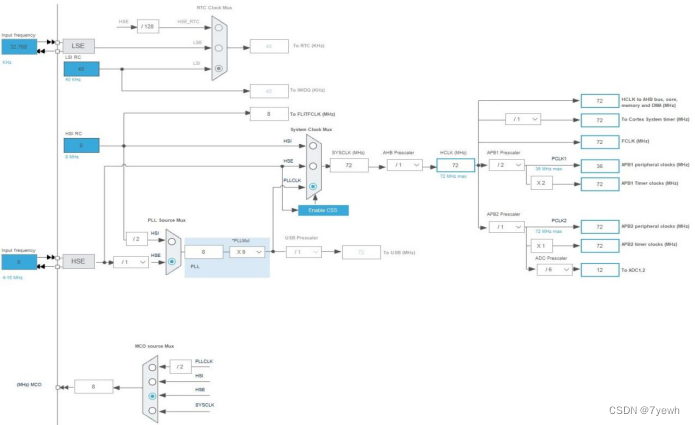

上图是STM32F103ZET6的时钟树图 请具体问题具体分析

A:表示其它电路需要的输入指定的源时钟信号以及可选的信号

往左边看为外部引脚OSC_IN(PD0)、OSC_OUT(PD1)、OSC32_IN(PC14)、OSC32_OUT(PC15)、MCO(PA8 用来可选主时钟输出)具体可查引脚图。

B:锁相环,为一个特殊的振荡电路“PLL”其PLLSRC为选择输入时钟源(选择外部还是内部高速时钟输入)、PLLMUL为PLL倍频系数(*2~*16)、PLLCLK为高速的倍频时钟(简而言之可以使其信号放大做效为了达到72MHZmax的效果)。

C:为我们重点需要关注的MCU内的主系统时钟“SYSCLK”;AHB也可以理解成HCLK预分频器将 SYSCLK分频或不分频后分发给其它外设进行处理。

D:APB1总线时钟,由HCLK 经过标号E的低速APB1预分频器得到,分频因子可以选择 1,2,4,8,16,这里我们选择的是2分频,所以 APB1 总线时钟为 36M。由于 APB1 是低速总线 时钟,所以APB1总线最高频率为 36MHz,片上低速的外设就挂载在该总线上,例如有看门狗定时器、定时器 2/3/4/5/6/7(通用定时器最好都72MHZ)、RTC 时钟、USART2/3/4/5、SPI2(I2S2)与SPI3(I2S3)、I2C1与I2C2、CAN、USB 设备和2个DAC。

E:APB2 总线时钟,由 HCLK 经过标号 F 的高速 APB2 预分频器得到,分频因子可以选择 1,2,4,8,16,这里我们选择的是 1 即不分频,所以 APB2 总线时钟频率为 72M。与 APB2 高速总线链接的外设有外部中断与唤醒控制、7 个通用目的输入/输出口(PA、PB、PC、PD、PE、PF和 PG)、定时器 1、定时器 8(高级定时器最好都72MHZ)、SPI1、USART1、3 个 ADC 和内部温度传感器。其中标号 G 是ADC 的预分频器在后面 ADC 实验中详细说明不超过14MHZ一般都是除于6。

F:Cortex-M内核系统的时钟,FCLK为自由运行时钟,用来采样中断和调试模块计时,休眠依然有效;顺便讲述CSS为时钟安全系统,如果HSE外部告诉时钟启动失败,切换HSI,可进NIMI中断。

G:是STM32的时钟输出功能,用来可选主时钟输出。

![[数据集][目标检测]中国象棋检测数据集VOC+YOLO格式300张12类别](https://img-blog.csdnimg.cn/direct/47d27f3b5ca84c6e9a3bc761e6c99e98.png)

![[数据集][目标检测]变电站火灾检测电力场景烟雾明火检测数据集VOC+YOLO格式140张2类别真实场景非PS合成](https://img-blog.csdnimg.cn/direct/d7cb87bec86644359a014885d391ec3e.png)