解决VIvado编程中遇到的bug 2

语言 :Verilg HDL

EDA工具: Vivado、modelsim

- 关键词: 调用,Verilog HDL,modelsim,bug

一、引言

此系列博客专门发表 博主在开发过程中遇到的各种bug,以及bug的思路分析以及解决方法,帮助诸君在开发过程中遇到类似的问题能迅速找到解决思路和方法。

二、问题、分析及解决方法

1. 在modelsim仿真时遇到报错

(1)错误

*Error (suppressible): (vsim-3009) [TSCALE] - Module ‘tb_top’ does

not have a timeunit/timeprecision specification in effect,

but other modules do.

(2)分析

tb 文件中 没有时间刻度,仿真时,没有时间刻度的参考

(3)解决办法

增加 时间刻度语句

`timescale 1ns / 1ps

2、vivado编译时报错

(1)错误

[Labtools 27-1429] XML parser encountered a problem in file

F:/prj/test2/test.hw/hw_1/hw.xml at line 1 : XML character encoding

not supported

(2)分析

hw.xml的第一行遇到了一个不被支持的XML字符编码。XML标准支持多种字符编码,包括但不限于UTF-8、UTF-16等。如果XML文件使用的编码格式不被Vivado工具支持,或者文件的编码声明与实际编码不一致,就可能会报这种错误。

(3)解决办法

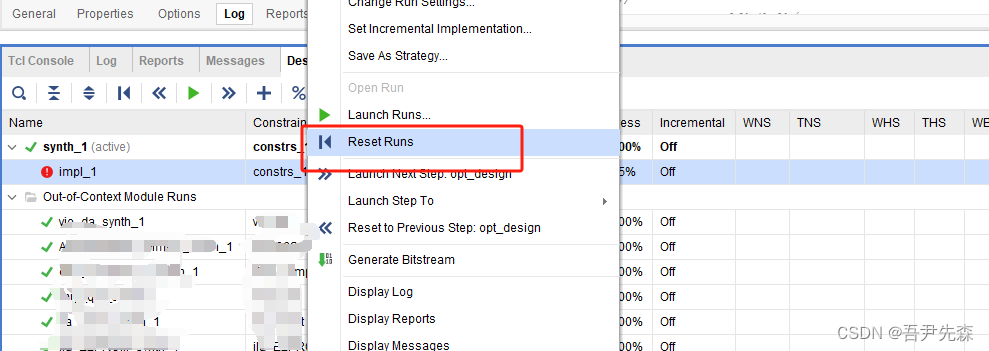

reset vivado工程的 综合和编译,然后重新编译生成比特流。

3、vivado编译时报错

(1)错误

[Place 30-73] Invalid constraint on register

‘Inst_dsp_core_wrapper/Inst_DSP_DCORE/axi_quad_spi_0/U0/NO_DUAL_QUAD_MODE.QSPI_NORMAL/IO0_I_REG’. It has the property IOB=TRUE, but it is not driving or driven by any

IO element.

(2)分析

在Vivado中进行布局(Place)阶段时,遇到了一个约束问题。具体来说,错误信息表明对寄存器Inst_dsp_core_wrapper/Inst_DSP_DCORE/axi_quad_spi_0/U0/NO_DUAL_QUAD_MODE.QSPI_NORMAL/IO0_I_REG有一个无效的约束,该寄存器具有属性IOB=TRUE,但它没有驱动或被任何IO元素驱动。

在FPGA设计中,IOB(Input/Output Block)属性通常用于指示某个寄存器应该被放置在FPGA芯片的I/O区域。然而,这个错误表明虽然指定了IOB=TRUE,但该寄存器并没有与任何输入/输出引脚连接,这违反了布局约束的逻辑。

(3)解决办法

将软核模块中多余的接口删除即可