Zynq 芯片架构由嵌入式处理器(Processing System, PS)与可编程逻辑(Programmable Logic, PL),以及 PS 与 PL 之间的互联总线组成。本文主要介绍 Xilinx Zynq 芯片开发所使用的软件,包括 Vivado IDE 与 Xilinx SDK 的介绍,以及 Zynq 芯片 PL 与 PS 两部分的基本开发流程。

目录

在上一篇博文中,我们知道了 Zynq 芯片的基本架构 —— 嵌入式处理器(Processing System, PS)与可编程逻辑(Programmable Logic, PL),以及 PS 与 PL 之间的互联总线,集成在单一 SoC 上。在这里,我们将 Zynq 芯片的开发流程分为 PL 和 PS 两部分。

1 PL 部分

1.1 Xilinx Vivado 介绍

Vivado IDE 是 Xilinx 公司(现在属于 AMD)推出的新一代集成开发环境,用于替代之前的 ISE 。Vivado 提供便捷、美观的用户图形界面,用于 Xilinx FPGA 的开发与应用。

Vivado IDE 是 Xilinx 公司(现在属于 AMD)推出的新一代集成开发环境,用于替代之前的 ISE 。Vivado 提供便捷、美观的用户图形界面,用于 Xilinx FPGA 的开发与应用。

Vivado 是多语言的设计输入与综合工具,支持 Verilog、System Verilog 与 VHDL 语言。同时,Vivado 也包括了设计实现、仿真验证、时序分析、功耗分析等工具,可以帮助工程师高效定位并解决复杂 FPGA 设计中的问题。

Vivado HLx Editions 开始界面

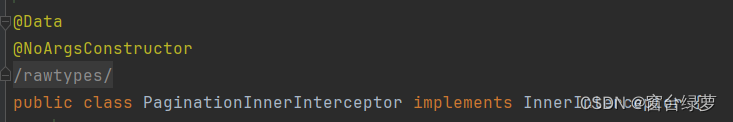

在 Zynq 的开发过程中,需要注意使用的 Vivado 版本,是否包含所需要的芯片型号。后续的 Zynq 开发介绍均使用 xc7z020clg 芯片,软件版本为 Vivado 2018.3。

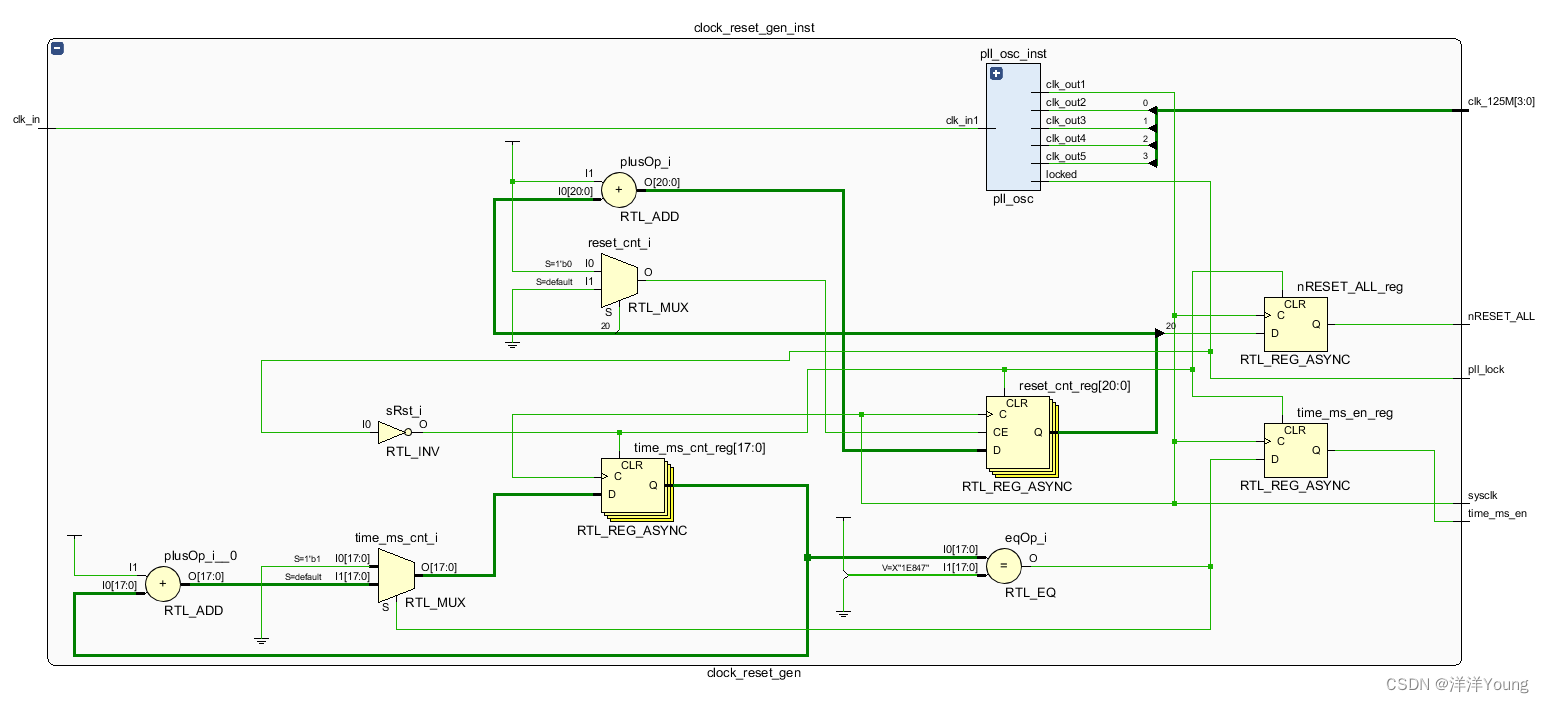

1.2 基于 RTL 代码的开发流程

RTL 是寄存器传输级(Register Transfer Level)的英文缩写,RTL 代码主要使用硬件描述语言(如 Verilog,VHDL)描述数字电路的输入输出,以及寄存器之间的传输关系。

在 RTL 代码中,寄存器用于暂存数据,而传输线则表示数据在各寄存器之间的流动。RTL 代码结构清晰、易于理解,适用于描述中等规模以下的数字电路。

基于 RTL 代码的开发流程如下:

1)新建 Vivado 工程;

2)添加 RTL 设计文件与所需要的 IP;

3)I/O 布局与时序约束;

4)逻辑综合、布局布线、生成比特流;

5)比特流配置。

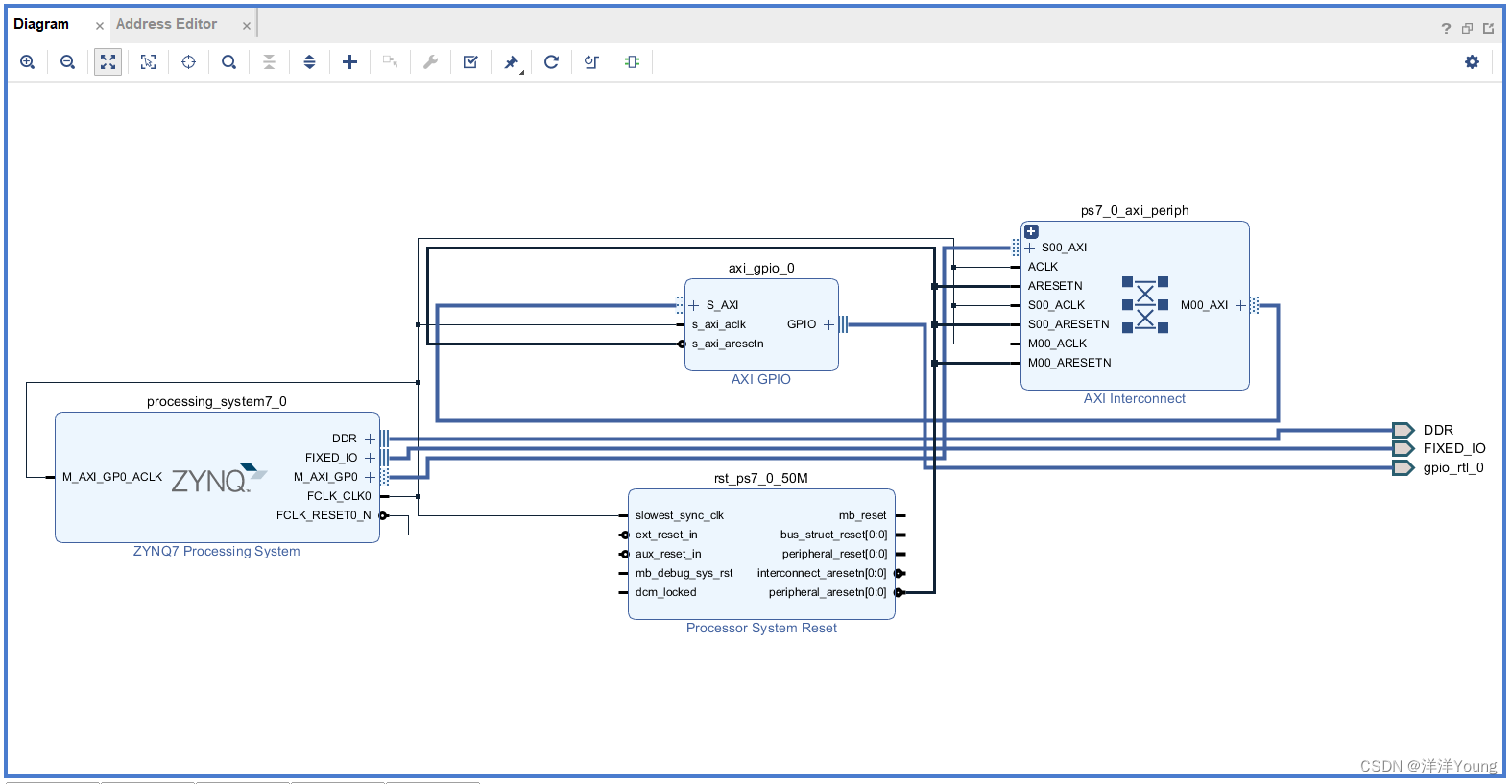

1.3 基于 Block Design 的开发流程

Vivado 提供一个叫做 IP Integrator 的工具,用于创建与设计 Block Design(.bd)文件。Block Design 可以理解为使用 IP 搭建的数字电路系统,主要通过可视化的操作(例如 IP 添加与位置移动、端口连线等方式)进行设计。

基于 Block Design 的开发流程如下:

1)新建 Vivado 工程;

2)创建新的 Block Design 文件,并添加所需要的嵌入式处理器或其他 IP;

3)连接 IP 核并进行必要的配置,如时钟频率、接口协议等;

4)右键点击 Block Design,选择 Create HDL Wrapper...,创建 HDL 文件;

5)I/O 布局与时序约束;

6)逻辑综合、布局布线、生成比特流;

7)比特流配置。

2 PS 部分

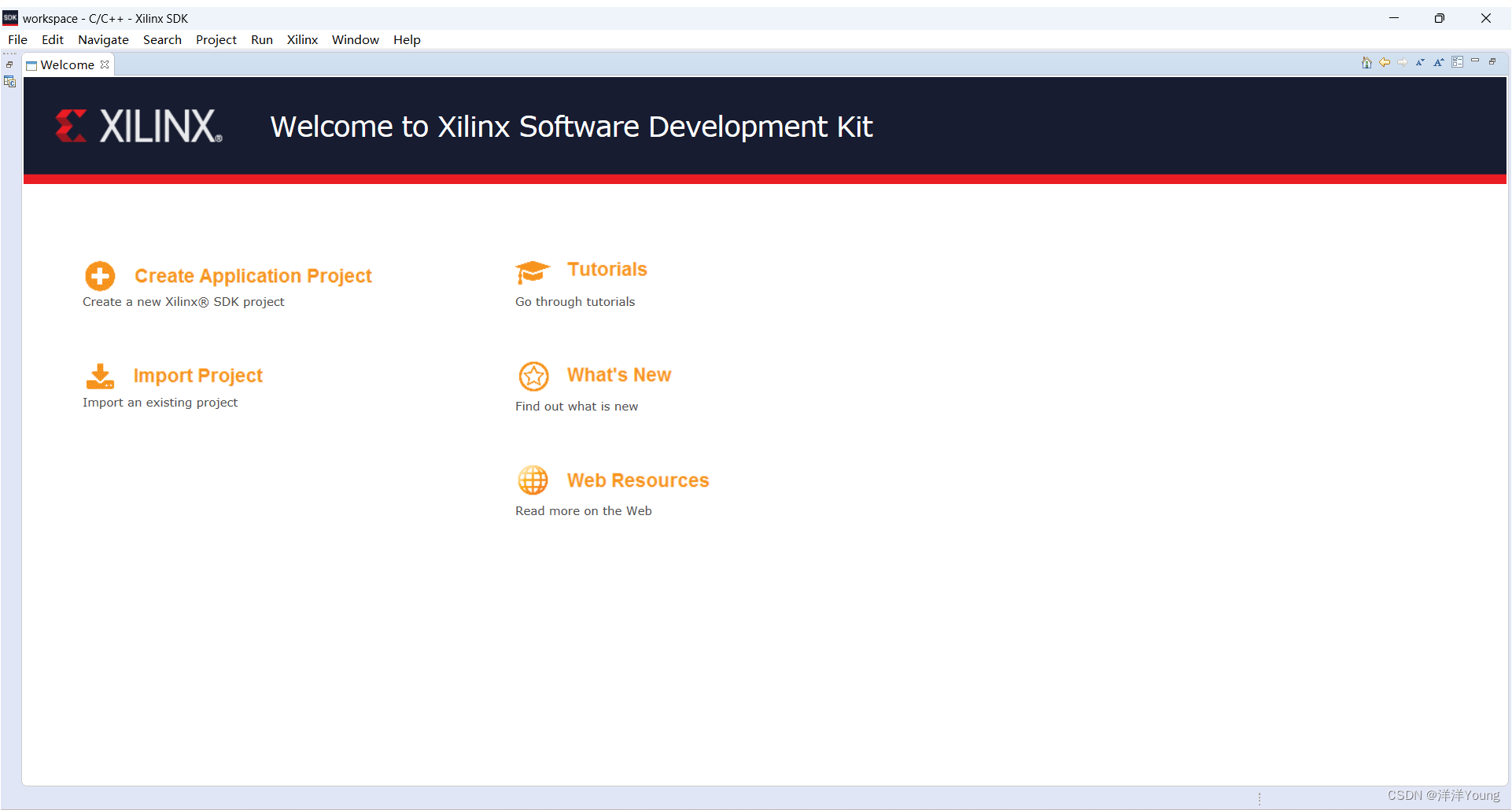

2.1 Xilinx SDK 介绍

Xilinx SDK 是 Xilinx 公司(现在属于 AMD)推出的集成开发环境,用于 Xilinx 嵌入式处理器(如 MicroBlaze,ARM Cortex-A9 等)的开发与应用,SDK 需要和 Vivado 创建的硬件设计配合使用。

Xilinx SDK 是 Xilinx 公司(现在属于 AMD)推出的集成开发环境,用于 Xilinx 嵌入式处理器(如 MicroBlaze,ARM Cortex-A9 等)的开发与应用,SDK 需要和 Vivado 创建的硬件设计配合使用。

Xilinx SDK 基于 Eclipse 开源标准,主要包括以下特性:

- C/C++ 代码编辑器和编译环境

- 应用程序构建配置和 Makefile 自动生成

- 集成调试与分析

- 源代码版本管理

- 专用的 FPGA 配置工具

Xilinx SDK 开始界面

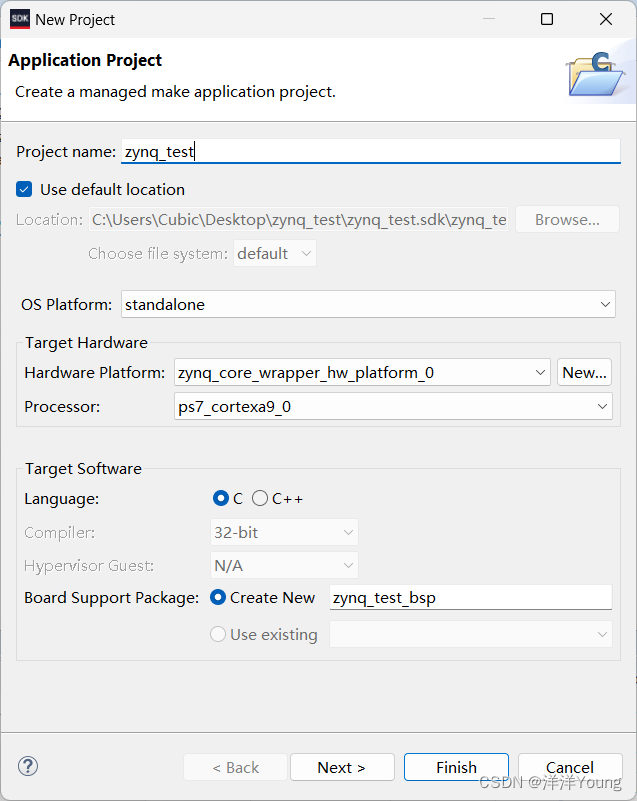

2.2 基于 C/C++ 代码的开发流程

在前面提到,SDK 程序需要和 Vivado 硬件设计配合使用。因此,SDK 程序的开发从导出硬件设计开始。

1)在 Vivado 工程中,选择 File -> Export -> Export Hardware...,勾选“Include bitstream”,导出硬件设计;

2)选择 File -> Launch SDK,启动 SDK 开发环境;

3)在 SDK 中,选择 File -> New -> Application Project,新建 SDK 应用工程;

4)编写 SDK 程序,选择 Project -> Build Project,编译工程;

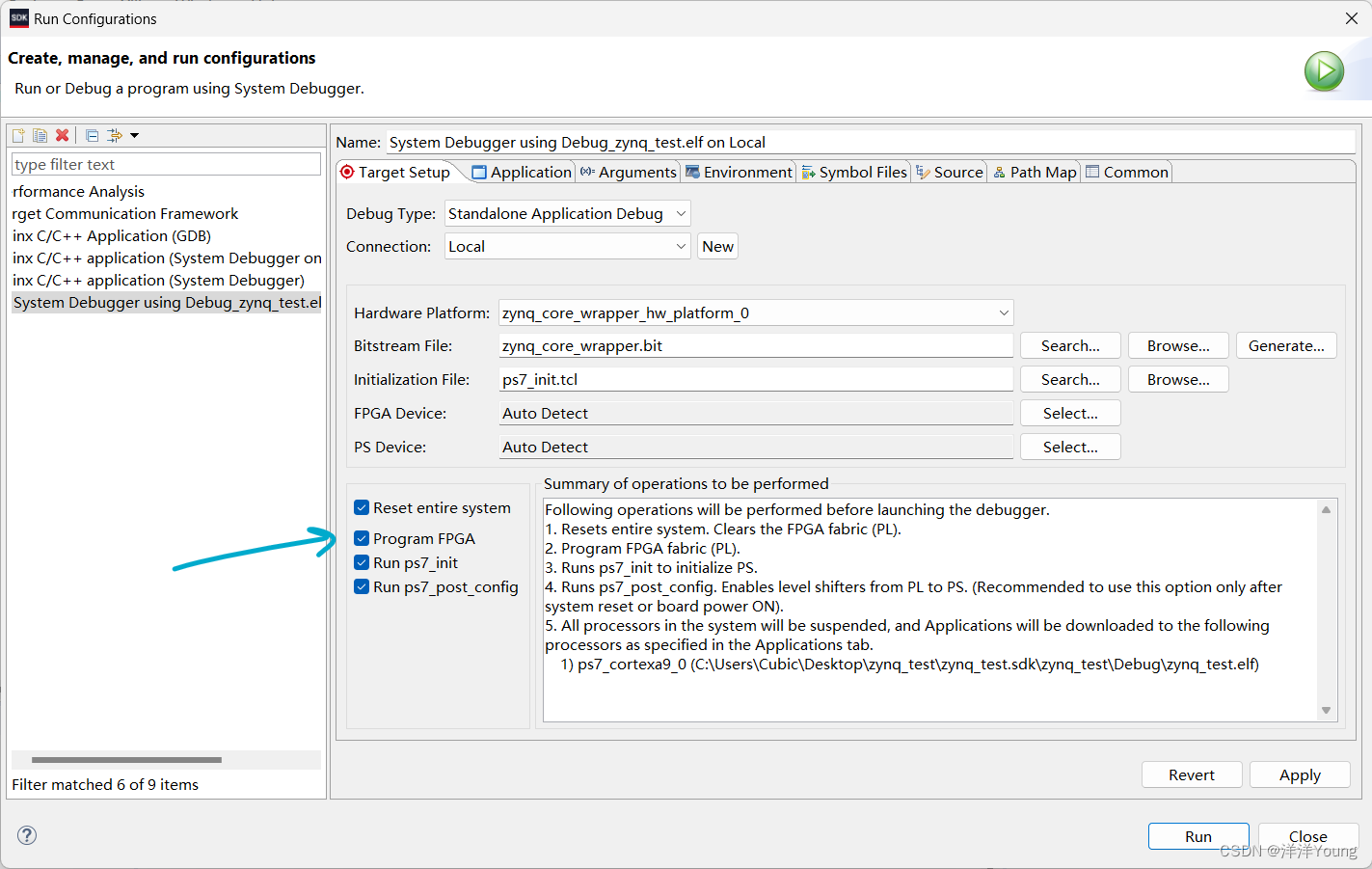

5)最后配置 Run Configurations,勾选 “Program FPGA”,并运行 SDK 程序,就可以上板调试了。