本次实验(一)见博客:【数字电路与系统】【北京航空航天大学】实验:时序逻辑设计——三色灯开关(一)、实验指导书

说明:本次实验的代码使用verilog编写,文章中为阅读方便,故采用matlab代码格式。

实验二、时序逻辑设计——三色灯开关(实验报告部分)

2、实验报告

2.1、需求分析

本次实验要求设计一种通过操作开关的时间控制灯光颜色的开关,该灯具含有两组LED白光灯芯和两组LED黄光灯芯,且开关的功能大致分为四种情况:

1、 如果灯具发出白光时断开开关,且在1秒之内再次闭合开关,则灯具发出日光;

2、 如果灯具发出日光时断开开关,且在1秒之内再次闭合开关,则灯具发出黄光;

3、 如果灯具发出黄光时断开开关,则再次闭合开关之后,灯具发出白光;

4、 如果开关断开的时间超过1秒,则开关闭合后,灯具发出白光。

因此可以总结出该灯具大致的工作流程为:白光——日光——黄光——白光,且时延Δt = 1秒,故可以设置cnt变量用于计时。

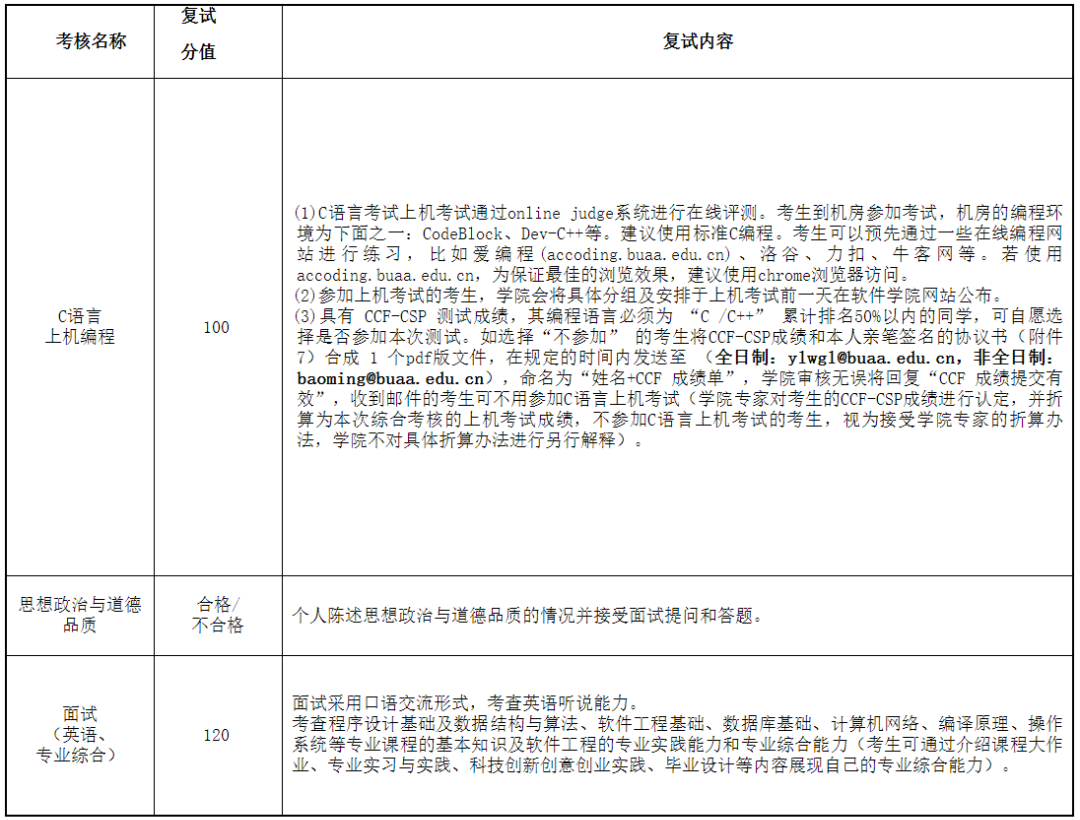

扩展实验要求:

开发时序逻辑电路,将按动开关的操作(“开”、“关”)以及按动开关之间的时间间隔(以

10ms为单位,进行0~127编码,分别代表0s至1.27s,超过1.27s均算作1.27s)以数码的形式“录制”下来,记录深度至少为16条操作序列(至少能保存16次操作);

按动实验板上的一个按键,可以将记录的内容用UART依次上传并显示到PC机终端上。

2.2、系统设计

2.2.1、总体设计思路

模块:按照设计需求,分为 “mode_run” 模块 & “mode_demo” 模块以及用于按键去抖的debounce模块。

由于题目要求延时一定时间后重新设定状态,故可以设置一cnt变量用于计时;使用RESET进行复位。

拓展实验:

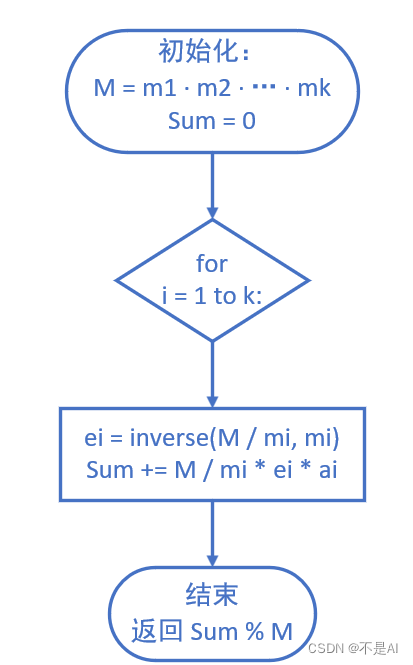

通过Uart_ClkDiv进行时钟分频,Key进行按键消抖,Uart_Tx作为上传数据模块,time_cnt作为记录数据并依次上传模块。

2.2.2、接口设计

mode_run:

input clk (系统时钟), rst (重置);

key0 (按键0) LOC = P2;

key1 (按键1) LOC = P3;

NET "led[0]" LOC = P79;

NET "led[1]" LOC = P83;

NET "led[2]" LOC = P84;

NET "led[3]" LOC = P85;

NET "clk" LOC = P36;

NET "rst" LOC = P11;

NET "key0" LOC = P2;

NET "key1" LOC = P3;

mode_demo:

NET "light[0]" LOC = P23;

NET "light[1]" LOC = P18;

NET "light[2]" LOC = P15;

NET "light[3]" LOC = P16;

NET "light[4]" LOC = P17;

NET "light[5]" LOC = P22;

NET "light[6]" LOC = P24;

NET "clk" LOC = P36;

NET "dp" LOC = P12;

NET "com[0]" LOC = P27;

NET "com[1]" LOC = P26;

NET "key0" LOC = P2;

NET "key1" LOC = P3;

NET "rst" LOC = P11;

Uart_time:

NET "Sys_CLK" LOC = P36;

NET "Key_In[0]" LOC = P32;

NET "Key_In[1]" LOC = P2;

NET "Sys_RST" LOC = P11;

NET "Sys_RST" PULLUP;

NET "Signal_Tx" LOC = P10;

2.2.3、mode_run模块

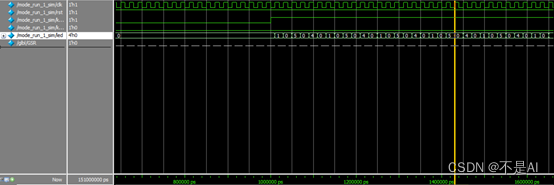

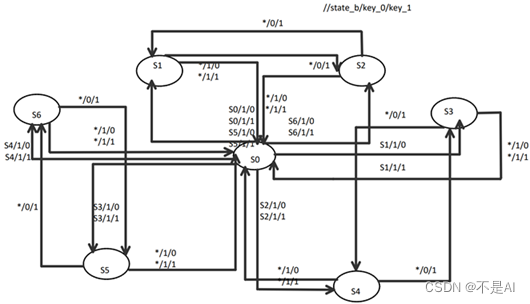

图 1 状态机流程图

module mode_run_1(

clk,

rst,

key0,

key1,

led

);

input clk ;

input rst ;

input key0 ;

input key1 ;

wire key_0 ;

wire key_1 ;

output reg [3:0] led ;

debounce instance_name0 (

.clk(clk),

.rst(rst),

.key(key0),

.key_pulse(key_0)

);

debounce instance_name1 (

.clk(clk),

.rst(rst),

.key(key1),

.key_pulse(key_1)

);

reg [24:0] cnt ;

parameter C_25M = 25'd24_999_999;

//信号定义

reg [3:0] state_b ;

//状态机参数

parameter S0 = 4'b0000 ;

parameter S1 = 4'b0001 ;

parameter S2 = 4'b0011 ;

parameter S3 = 4'b0101 ;

parameter S4 = 4'b1111 ;

parameter S5 = 4'b0100 ;

parameter S6 = 4'b1100 ;

initial begin

state_b <= S0;

led <= S0;

cnt <= 25'b0;

end

//一段式状态机

always@(posedge clk or negedge rst) begin

if(!rst) begin

state_b <= S0;

led <= S0;

cnt <= 25'b0;

end

else begin

if(key_0 == 1) cnt <= 25'b0;

else cnt <= cnt + 1;

if(cnt >= C_25M && led == S0)

state_b <= S0;

else state_b <= state_b;

case(led)

S0: begin

if(key_0 == 1) begin

case(state_b)

S0: begin

state_b <= S1;

led <= S1;

end

S1: begin

state_b <= S3;

led <= S3;

end

S2: begin

state_b <= S4;

led <= S4;

end

S3: begin

state_b <= S5;

led <= S5;

end

S4: begin

state_b <= S6;

led <= S6;

end

S5: begin

state_b <= S1;

led <= S1;

end

S6: begin

state_b <= S2;

led <= S2;

end

default: begin

state_b <= state_b;

led <= led;

end

endcase

end

else begin

led <= S0;

end

end

S1: begin

if(key_0 == 1) begin

state_b <= S1;

led <= S0;

end

else if(key_1 == 1) begin

state_b <= S2;

led <= S2;

end

end

S2: begin

if(key_0 == 1) begin

state_b <= S2;

led <= S0;

end

else if(key_1 == 1) begin

state_b <= S1;

led <= S1;

end

end

S3: begin

if(key_0 == 1) begin

state_b <= S3;

led <= S0;

end

else if(key_1 == 1) begin

state_b <= S4;

led <= S4;

end

end

S4: begin

if(key_0 == 1) begin

state_b <= S4;

led <= S0;

end

else if(key_1 == 1) begin

state_b <= S3;

led <= S3;

end

end

S5: begin

if(key_0 == 1) begin

state_b <= S5;

led <= S0;

end

else if(key_1 == 1) begin

state_b <= S6;

led <= S6;

end

end

S6: begin

if(key_0 == 1) begin

state_b <= S6;

led <= S0;

end

else if(key_1 == 1) begin

state_b <= S5;

led <= S5;

end

end

default: begin

state_b <= state_b;

led <= led;

end

endcase

end

end

endmodule

2.2.4、debounce模块

该模块为防抖模块。对按键KEY进行消抖,达到输入信号稳定且有效的目的。

2.2.5、mode_demo模块

module mode_demo_1(

clk,

rst,

key0,

key1,

dp,

light,

com

);

input clk ;

input rst ;

input key0 ;

input key1 ;

wire key_0 ;

wire key_1 ;

output reg [1:0] com ;

output reg dp ;

output reg [6:0] light ;

debounce instance_name0 (

.clk(clk),

.rst(rst),

.key(key0),

.key_pulse(key_0)

);

debounce instance_name1 (

.clk(clk),

.rst(rst),

.key(key1),

.key_pulse(key_1)

);

//信号定义

reg [3:0] state_b ;

reg [3:0] state_c ;

//状态机参数

parameter S0 = 4'b0000 ;

parameter S1 = 4'b0001 ;

parameter S2 = 4'b0011 ;

parameter S3 = 4'b0101 ;

parameter S4 = 4'b1111 ;

parameter S5 = 4'b0100 ;

parameter S6 = 4'b1100 ;

//数码管译码

parameter DATA0 = 7'b0111111 ;

parameter DATA1 = 7'b0000110 ;

parameter DATA2 = 7'b1011011 ;

parameter DATA3 = 7'b1001111 ;

parameter DATA4 = 7'b1100110 ;

parameter DATA5 = 7'b1101101 ;

parameter DATA6 = 7'b1111101 ;

parameter DATA7 = 7'b0000111 ;

parameter DATA8 = 7'b1111111 ;

parameter DATA9 = 7'b1101111 ;

reg sec_pls; //产生秒脉冲

reg [25:0] sec_cnt;

always@(posedge clk or negedge rst) begin

if(key_0 == 1) begin

sec_pls <= 1'b0;

sec_cnt <= 26'b0;

end

else begin

sec_pls <= sec_pls;

sec_cnt <= sec_cnt;

end

if(!rst) begin

sec_pls <= 1'b0;

sec_cnt <= 26'b0;

end

else if(sec_cnt == 26'd50_000_000) begin

sec_pls <= 1'b1;

sec_cnt <= 26'b0;

end

else begin

sec_pls <= 1'b0;

sec_cnt <= sec_cnt + 1;

end

end

reg [6:0] sec;

reg [3:0] tmp;

reg [3:0] num;

reg [3:0] buf0;

reg [3:0] buf1;

reg dp1;

//计数器,约10ms扫描一次,用于数码管动态显示

reg [16:0] cnt;

always@(posedge clk or negedge rst) begin

if(!rst) cnt <= 17'b0;

else if(cnt == 17'b11111111111111111) begin

cnt <= 17'b0;

end

else cnt <= cnt + 1;

end

always@(posedge clk or negedge rst) begin

if(!rst) begin

state_c <= S0;

state_b <= S0;

dp <= 0;

end

else begin

if(sec >= 10 && state_c == S0)

state_b <= S0;

else state_b <= state_b;

case(state_c)

S0: begin

if(key_0 == 1) begin

case(state_b)

S0: begin

state_b <= S1;

state_c <= S1;

end

S1: begin

state_b <= S3;

state_c <= S3;

end

S2: begin

state_b <= S4;

state_c <= S4;

end

S3: begin

state_b <= S5;

state_c <= S5;

end

S4: begin

state_b <= S6;

state_c <= S6;

end

S5: begin

state_b <= S1;

state_c <= S1;

end

S6: begin

state_b <= S2;

state_c <= S2;

end

default: begin

state_b <= state_b;

state_c <= state_c;

end

endcase

end

else begin

state_b <= state_b;

state_c <= S0;

end

end

S1: begin

if(key_0 == 1) begin

state_b <= S1;

state_c <= S0;

end

else if(key_1 == 1) begin

state_b <= S2;

state_c <= S2;

end

end

S2: begin

if(key_0 == 1) begin

state_b <= S2;

state_c <= S0;

end

else if(key_1 == 1) begin

state_b <= S1;

state_c <= S1;

end

end

S3: begin

if(key_0 == 1) begin

state_b <= S3;

state_c <= S0;

end

else if(key_1 == 1) begin

state_b <= S4;

state_c <= S4;

end

end

S4: begin

if(key_0 == 1) begin

state_b <= S4;

state_c <= S0;

end

else if(key_1 == 1) begin

state_b <= S3;

state_c <= S3;

end

end

S5: begin

if(key_0 == 1) begin

state_b <= S5;

state_c <= S0;

end

else if(key_1 == 1) begin

state_b <= S6;

state_c <= S6;

end

end

S6: begin

if(key_0 == 1) begin

state_b <= S6;

state_c <= S0;

end

else if(key_1 == 1) begin

state_b <= S5;

state_c <= S5;

end

end

default: begin

state_c <= state_c;

state_b <= state_b;

end

endcase

end

if(key_0 == 1) begin

sec <= 7'b0;

num <= 4'b0;

com <= 2'b00;

light <= DATA0;

end

else sec <= sec;

if(!rst) begin

sec <= 7'b0;

light <= DATA0;

end

else if(sec_pls) begin

if(sec == 7'd99) begin

sec <= 7'b0;

num <= 4'b0;

light <= DATA0;

end

else begin

sec <= sec + 1;

case(state_c) //dp位表示状态

S0: begin

if(sec >= 7'd10) state_b <= S0;

else state_b <= state_b;

end

S2: begin

dp1 <= ~dp1;

end

S4: begin

dp1 <= ~dp1;

end

S6: begin

dp1 <= ~dp1;

end

endcase

end

end

//显示模块

if(!rst) begin

num <= 4'b0;

com <= 2'b00;

end

else begin

if(sec >= 0 && sec < 10) begin //数码管显示数字

buf1 <= 0;

buf0 <= sec[3:0];

end

else if(sec >= 10 && sec < 20) begin

buf1 <= 4'd1;

tmp <= (sec - 7'd10);

buf0 <= tmp[3:0];

end

else if(sec >= 20 && sec < 30) begin

buf1 <= 4'd2;

tmp <= sec - 7'd20;

buf0 <= tmp[3:0];

end

else if(sec >= 30 && sec < 40) begin

buf1 <= 4'd3;

tmp <= sec - 7'd30;

buf0 <= tmp[3:0];

end

else if(sec >= 40 && sec < 50) begin

buf1 <= 4'd4;

tmp <= sec - 7'd40;

buf0 <= tmp[3:0];

end

else if(sec >= 50 && sec < 60) begin

buf1 <= 4'd5;

tmp <= sec - 7'd50;

buf0 <= tmp[3:0];

end

else if(sec >= 60 && sec < 70) begin

buf1 <= 4'd6;

tmp <= sec - 7'd60;

buf0 <= tmp[3:0];

end

else if(sec >= 70 && sec < 80) begin

buf1 <= 4'd7;

tmp <= sec - 7'd70;

buf0 <= tmp[3:0];

end

else if(sec >= 80 && sec < 90) begin

buf1 <= 4'd8;

tmp <= sec - 7'd80;

buf0 <= tmp[3:0];

end

else if(sec >= 90 && sec < 100) begin

buf1 <= 4'd9;

tmp <= sec - 7'd90;

buf0 <= tmp[3:0];

end

case(cnt[16])

1'b0: begin

com <= 2'b01;

num <= buf0;

case(state_c)

S0: dp <= 0;

S1: dp <= 1;

S2: dp <= dp1;

S3: dp <= 1;

S4: dp <= dp1;

S5: dp <= 0;

S6: dp <= 0;

default: dp <= 0;

endcase

end

1'b1: begin

com <= 2'b10;

num <= buf1;

case(state_c)

S0: dp <= 0;

S1: dp <= 0;

S2: dp <= 0;

S3: dp <= 1;

S4: dp <= dp1;

S5: dp <= 1;

S6: dp <= dp1;

default: dp <= 0;

endcase

end

endcase

case(num) //个位

4'd0: light <= DATA0;

4'd1: light <= DATA1;

4'd2: light <= DATA2;

4'd3: light <= DATA3;

4'd4: light <= DATA4;

4'd5: light <= DATA5;

4'd6: light <= DATA6;

4'd7: light <= DATA7;

4'd8: light <= DATA8;

4'd9: light <= DATA9;

default: light <= DATA0;

endcase

end

end

endmodule

2.2.6、time_cnt模块

module time_cnt(Sys_CLK,Sys_RST,Idle,Key_In,send_data,send_en

);

input Sys_CLK;

input Sys_RST;

input Idle;

input [1:0]Key_In;

output reg [7:0] send_data;

output reg send_en;

reg key0_d1;

reg key0_d2;

reg key1_d1;

reg key1_d2;

reg [7:0] time_cnt;

reg [3:0] send_cnt;

reg [17:0]Div_Cnt = 18'd0; //

reg Div_CLK_10ms = 1'b0;

reg Div_CLK_10ms_d1 = 1'b0;

reg Div_CLK_10ms_d2 = 1'b0;

reg cnt_flag;

reg send_flag;

reg [7:0] send_data_reg [0:15];

always@(posedge Sys_CLK or negedge Sys_RST)

begin

if(!Sys_RST)begin

key0_d1 <= 1'b0;

key0_d2 <= 1'b0;

Div_CLK_10ms_d1 <= 1'b0;

Div_CLK_10ms_d2 <= 1'b0;

end

else

begin

key0_d1 <= Key_In[0];

key0_d2 <= key0_d1;

Div_CLK_10ms_d1 <= Div_CLK_10ms;

Div_CLK_10ms_d2 <= Div_CLK_10ms_d1;

end

end

always@(posedge Div_CLK_10ms or negedge Sys_RST)

begin

if(!Sys_RST)begin

key1_d1 <= 1'b0;

key1_d2 <= 1'b0;

end

else

begin

key1_d1 <= Key_In[1];

key1_d2 <= key1_d1;

end

end

always@(posedge Sys_CLK)

begin

if(Div_Cnt == 18'd250000)

begin

Div_Cnt = 18'd0;

Div_CLK_10ms = ~Div_CLK_10ms;

end

else

Div_Cnt = Div_Cnt + 1'd1;

end

always@(posedge Sys_CLK or negedge Sys_RST)

begin

if(!Sys_RST)begin

time_cnt <= 8'd0;

cnt_flag <= 1'b0;

end

else if(key0_d1 && !key0_d2) //rise

begin

time_cnt <= 8'd0;

cnt_flag <= 1'b1;

end

else if(!key0_d1 && key0_d2) //fall

begin

time_cnt <= 8'd0;

cnt_flag <= 1'b0;

end

else if(cnt_flag && Div_CLK_10ms_d1 && !Div_CLK_10ms_d2)

begin

time_cnt <= time_cnt + 8'd1;

end

end

always@(posedge Sys_CLK or negedge Sys_RST)begin

if(!Sys_RST)

begin

send_data_reg[0] <= 8'd0;

send_data_reg[1] <= 8'd0;

send_data_reg[2] <= 8'd0;

send_data_reg[3] <= 8'd0;

send_data_reg[4] <= 8'd0;

send_data_reg[5] <= 8'd0;

send_data_reg[6] <= 8'd0;

send_data_reg[7] <= 8'd0;

send_data_reg[8] <= 8'd0;

send_data_reg[9] <= 8'd0;

send_data_reg[10] <= 8'd0;

send_data_reg[11] <= 8'd0;

send_data_reg[12] <= 8'd0;

send_data_reg[13] <= 8'd0;

send_data_reg[14] <= 8'd0;

send_data_reg[15] <= 8'd0;

// send_data_reg[12] <= 8'd31;

// send_data_reg[13] <= 8'd42;

// send_data_reg[14] <= 8'd53;

// send_data_reg[15] <= 8'd64;

end

else if(!key0_d1 && key0_d2)

begin

send_data_reg[0] <= time_cnt;

send_data_reg[1] <= send_data_reg[0];

send_data_reg[2] <= send_data_reg[1];

send_data_reg[3] <= send_data_reg[2];

send_data_reg[4] <= send_data_reg[3];

send_data_reg[5] <= send_data_reg[4];

send_data_reg[6] <= send_data_reg[5];

send_data_reg[7] <= send_data_reg[6];

send_data_reg[8] <= send_data_reg[7];

send_data_reg[9] <= send_data_reg[8];

send_data_reg[10] <= send_data_reg[9];

send_data_reg[11] <= send_data_reg[10];

send_data_reg[12] <= send_data_reg[11];

send_data_reg[13] <= send_data_reg[12];

send_data_reg[14] <= send_data_reg[13];

send_data_reg[15] <= send_data_reg[14];

end

end

always@(posedge Div_CLK_10ms or negedge Sys_RST)

begin

if(!Sys_RST)begin

send_data <= 8'd0;

send_en <= 1'b0;

send_flag <= 1'b0;

end

else if(key1_d1 && !key1_d2)

begin

send_data <= send_data_reg[0];

send_en <= 1'b1;

send_flag <= 1'b1;

end

else if(send_flag && !Idle && send_en == 1'b0 && send_cnt < 4'd15)

begin

send_data <= send_data_reg[send_cnt];

// send_data <= send_data_reg[0];

send_en <= 1'b1;

send_flag <= 1'b1;

end

else if(send_flag && !Idle && send_en == 1'b0 && send_cnt == 4'd15)

begin

// send_data <= send_data_reg[send_cnt];

send_data <= send_data_reg[15];

send_en <= 1'b1;

send_flag <= 1'b0;

end

else

begin

send_en <= 1'b0;

end

end

always@(posedge Div_CLK_10ms or negedge Sys_RST)

begin

if(!Sys_RST)begin

send_cnt <= 4'd0;

end

else if(send_cnt < 4'd15 && send_en )

begin

send_cnt <= send_cnt + 4'd1;

end

end

endmodule

其他模块都已经在用例中给出,此处不再赘述。

(未完待续)