Chapter 3 Single-Stage Amplifiers

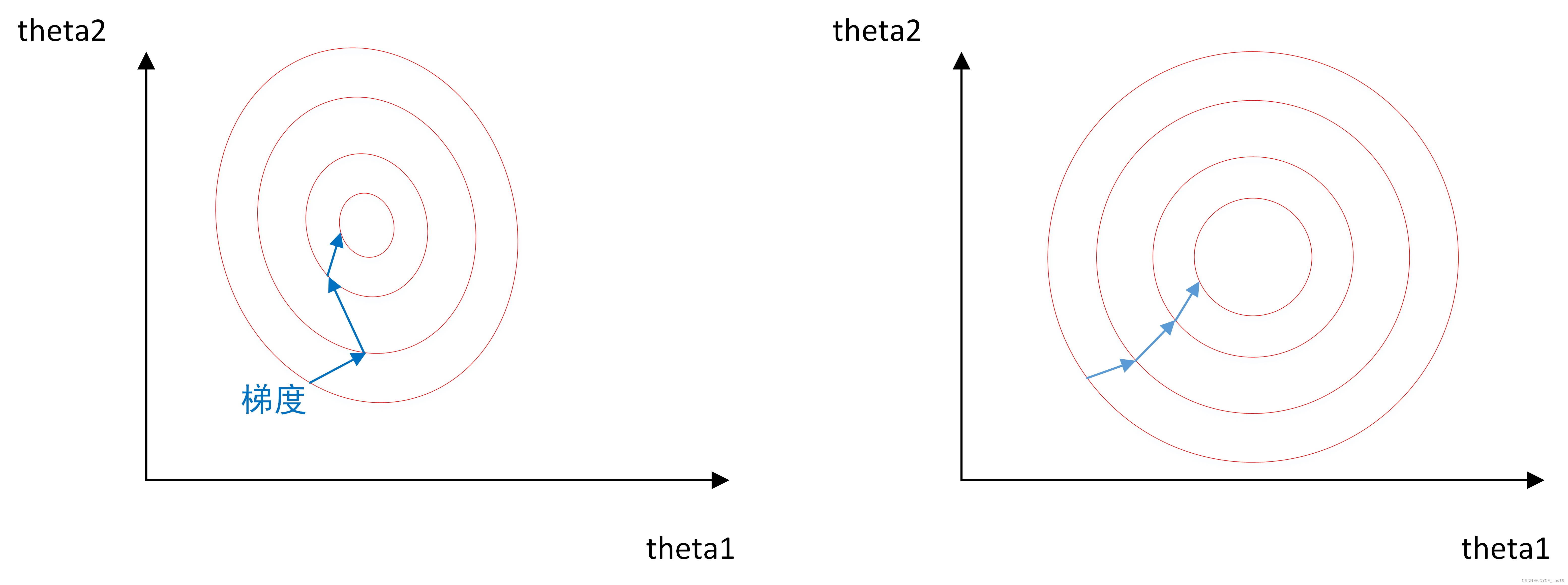

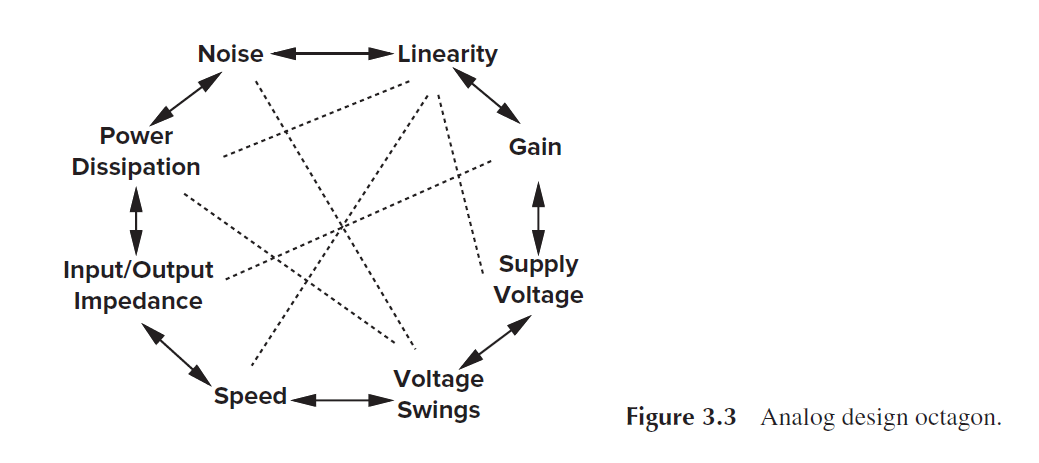

模拟设计, 各个性能指标之间的权衡:

3.3 Common-Source Stage

3.3.1 Common-Source Stage with Resistive Load

Common-Source 即gate为输入, drain为输出, source接DC源, 即AC=0. 如下图所示

小信号增益:

如果输入电压变化是大信号, 那么gm会变化, 导致非线性.

CS小信号模型

A v = − g m ( r o ∥ R D ) A_{v}=-g_{m}(r_{o}\parallel R_{D}) Av=−gm(ro∥RD)

对于单管 “intrinsic gain" = gm*Ro. 现代CMOS工艺, 短沟道器件gm *ro 降低到5~10. 因此认为1/gm << ro.

要增加CS的增益, 就必须增大输出阻抗.

3.3.2 CS Stage with Diode-Connected Load

现在工艺, 电阻Rd的阻值常常变化20%-30%, 我们常用“diode-connected”的MOS替代电阻, 因为其小信号模型类似一个电阻(1/gm).

小信号模型如下: 两端看进去的阻抗为1/gm

考虑body effect, 两端看进去的阻抗为1/(gm+gmb).

从大信号的角度, diode-connected的MOS永远处于饱和区, 因此电压和电流关系成平方根关系, 即V=sqrt(I).

在不考虑channel length modulation下,即Ro= ∞ (which is not the case), 从source看进去的阻抗永远为1/gm.

考虑下图CS带diode-connected MOS as load:

输出-输入小信号增益

A v = − g m 1 g m 2 1 η A_{v}=-\frac{g_{m1}}{g_{m2}}\frac{1}{\eta} Av=−gm2gm1η1

由于ID1=ID2, 两者都处于饱和区

A v = − ( W / L ) 1 ( W / L ) 2 1 η A_{v}=-\sqrt{\frac{(W/L)_1}{(W/L)_2}}\frac{1}{\eta} Av=−(W/L)2(W/L)1η1

来看大信号, Vout vs Vin如下图所示

当Vin<Vth1时, Vout=VDD-Vth2

当Vin>Vth1时, Vout=VDD-Vgs2

当VIn>Vout+Vth1(A点), M1进入线性区.

CS with Diode-Connected PMOS如下图所示

小信号增益Gain为

想要大增益, 就需要weak PMOS和strong NMOS. 但是weak PMOS意味着Vgs2大, 因此输出摆幅会减小.

在现代CMOS工艺, 都需要考虑Ro, 因此CS的增益为:

A v = − g m 1 ( 1 g m 2 ∥ r o 1 ∥ r o 2 ) A_{v}=-g_{m1}(\frac{1}{g_{m2}}\parallel r_{o1}\parallel r_{o2}) Av=−gm1(gm21∥ro1∥ro2)

3.3.3 CS Stage with Current-Source Load

采用电流源作为负载, 提高输出阻抗和增益:

好处是 Vout的摆幅可以达到Vds2,min=Vgs2-Vth2, 即override voltage, 一般为200mV (通过增加M2的W/L). 要增加输出阻抗ro, 就增加M2的L.

λ ∝ 1 L \lambda\propto \frac{1}{L} λ∝L1

输出阻抗

r o ∝ L I D r_o\propto \frac{L}{I_D} ro∝IDL

M1 intrinsic gain:

可看到 gain和L成正比 (由于lambda和L成反比), 和ID成反比.

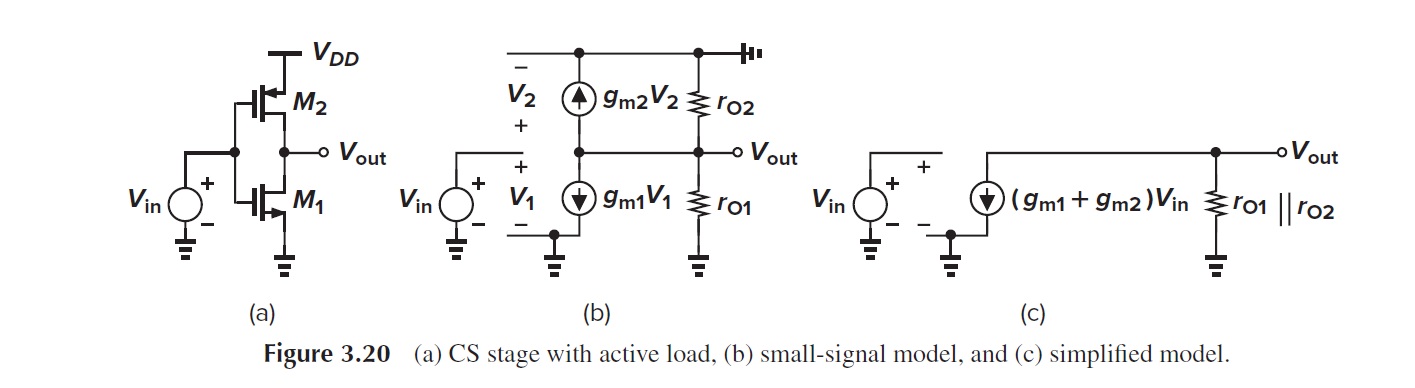

3.3.4 CS Stage with Active Load

把PMOS也做成放大级, NMOS和PMOS接成inverter形式, 如下图所示, 为complementary CS stage

Gain为:

A v = − ( g m 1 + g m 2 ) ( r O 1 ∥ r O 2 ) A_{v}=-(g_{m1}+g_{m2})(r_{O1}\parallel r_{O2}) Av=−(gm1+gm2)(rO1∥rO2)

这个电路需要处理两个问题:

1, bias 电流和PVT强相关, VDD=VGS_P+VGS_N, 因此VDD直接决定ID电流.

2, 这个电路放大VDD的噪声:

VDD到Vout的gain为

差不多为Vin到Vout Gain的一半.

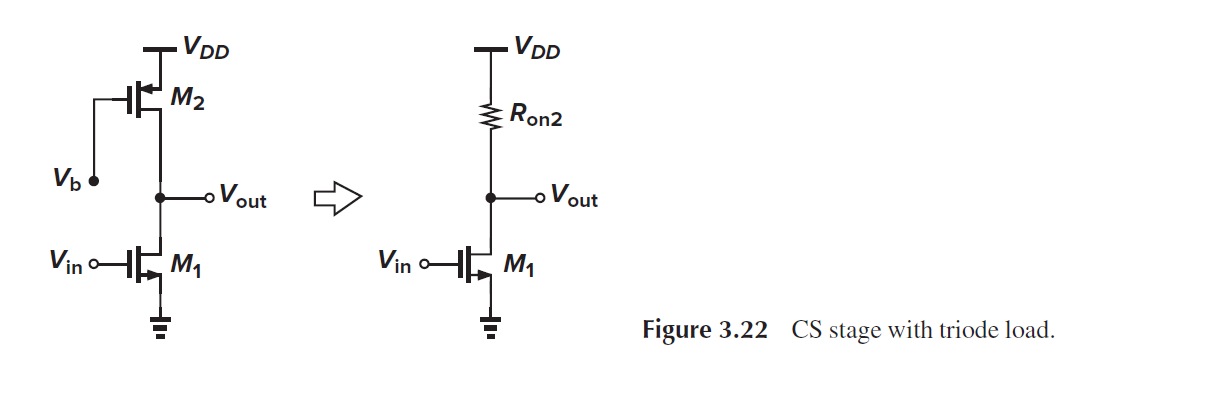

3.3.5 CS Stage with Triode Load

我们还可以用一个工作在线性区deep triode region的MOS作为CS输出电阻, 如下图所示: M2的gate足够低, 因此M2在线性区.

Up工艺偏差导致Ron2变化较大, 但是Triode loads的headroom更好.

3.3.6 CS Stage with Source Degeneration

对于饱和区管子, 电流和电压的变化是非线性的(平方律), 即gm不是常量. 为了得到相对constant gm, 我们可以在source上加resistor, 让输入管子more linear. Rs上电压=Vin-Vgs1, 因此ID=(Vin-Vgs1)/Rs, 电流随电压变化更加linear.

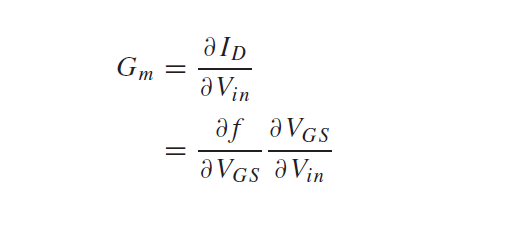

输出电流/输入电压的Gm为

G m = g m 1 + g m R S G_m=\frac{g_m}{1+g_mR_S} Gm=1+gmRSgm

小信号增益为:

A v = − G m R D = − g m R D 1 + g m R s A_v=-G_mR_D=-\frac{g_mR_D}{1+g_mR_s} Av=−GmRD=−1+gmRsgmRD

当Rs >> 1/gm, Gm=1/Rs, 因此gm约为常量, Drain电流随着输入电压线性变化.

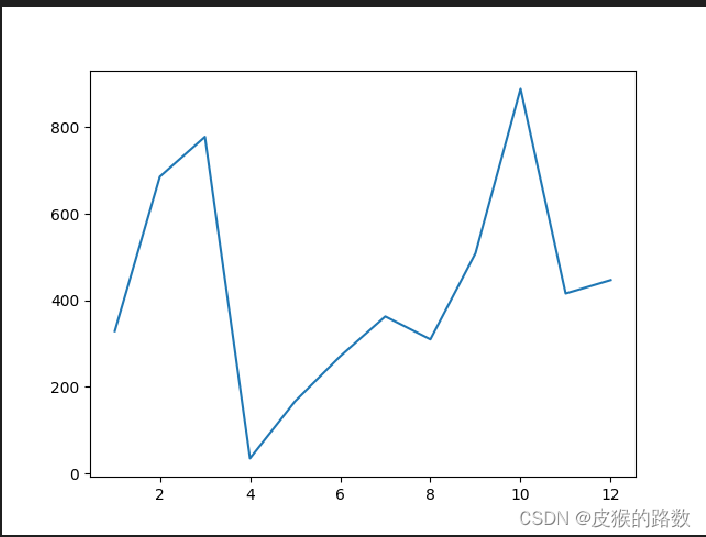

不带/带source degeneration的CS的ID和gm随着Vin的变化如下图, 可以看到ID很小时, 1/gm>> Rs, 因此Gm=gm, 当Vin变大后, ID vs Vin变得线性, Gm=1/Rs.

Gain还可以写为:

A v = − R D 1 g m + R s A_{v}=-\frac{R_D}{\frac{1}{g_m}+R_s} Av=−gm1+RsRD

即分母是source看进去的impedance=1/gm+Rs, 分子是drain的impedance=Rd.

CS的gain可认为是 (- 负的) drain的阻抗/sourc的阻抗, 这样极大简化了电路分析

V o u t V i n = − resistance in the drain resistance in the source \frac{V_{out}}{V_{in}}=-\frac{\text{resistance in the drain}}{\text{resistance in the source}} VinVout=−resistance in the sourceresistance in the drain

Output Resistance

degenerated CS stage的输出阻抗小信号模型如下:

从drain看进去的输出阻抗为

R o u t = [ 1 + ( g m + g m b ) R S ] r O R_{out}=[1+(g_m+g_{mb})R_S]r_O Rout=[1+(gm+gmb)RS]rO

Rout从Rs增大了gm*ro倍

直观理解可见下图

在Drain上变化V和I, 在Rs变化I, 但是Rs的V变小了, 因此Rs相对阻抗变大了.

在电路设计中, 采用casecode来增加输出阻抗是很常见和有效的!!!

3.4 Source Follower

对于CS, 要提高增益, 得增加输出阻抗. 如果需要驱动low-impedance load, 那么可以添加buffer, 这样就不会有gain的损失. source follower (或者称“common-drain” stage)就可作为一个电压buffer. 如下图所示.

M1工作在饱和区, 小信号Gain为, Gain约等于1

A v = g m R S 1 + ( g m + g m b ) R S A_{v}=\frac{g_mR_S}{1+(g_m+g_{mb})R_S} Av=1+(gm+gmb)RSgmRS

source用电阻会导致随着Vin变化, ID变化, Vout不能很好的跟随 Vin, 因此实际中把source接电流源, 如下图所示:

另外注意source follower的衬偏效应, 最好source和body接到一起.

source follower的输出阻抗:

R o u t = 1 g m + g m b R_{out}=\frac{{1}}{g_m+g_{mb}} Rout=gm+gmb1

和CS类似, 从source看进去的阻抗为1/gm.

Source follower driving load resistance:

A v = R e q R e q + 1 g m A_{v}=\frac{R_{eq}}{R_{eq}+\frac{1}{g_m}} Av=Req+gm1Req

其中

R e q = ( 1 / g m b ) ∥ r O 1 ∥ r O 2 ∥ R L R_{eq}=(1/g_{mb})\parallel r_{O1}\parallel r_{O2}\parallel R_{L} Req=(1/gmb)∥rO1∥rO2∥RL

Source followers 作为电压buffer, 优点是输入阻抗大, 输出阻抗较小. 缺点为非线性和voltage headroom.

非线性可用local tie也就是把body和source接到一起解决(确保有双阱工艺)

source follower将输出电压shift了一个Vgs, 因此减小了headroom.

Common-Gate Stage

Common-Gate (CG) 即source为输入, drain为输出, gate接DC源, 即AC=0

如下图所示

当Vin从大变小时, 输出变化. 当Vin > Vb-Vth, M1 off. 当Vin < Vb-Vth, M1进入饱和区, 随着Vin继续减小, M1进入线性区. 注意Vin和Vout变化同方向.

CG增益Gain, 注意CG的增益是正值, 输出输入方向相同, 而CS的gain是反的, 增益形式类似

A v = g m R D A_v=g_mR_D Av=gmRD

带Rs的CG小信号模型

CG增益Gain为, 和degenerated CS类似

考虑Source Follower (M1)再加上M2 as Common Gate放大器

M2 source可转化为Thevenin等效电路

因此Gain为

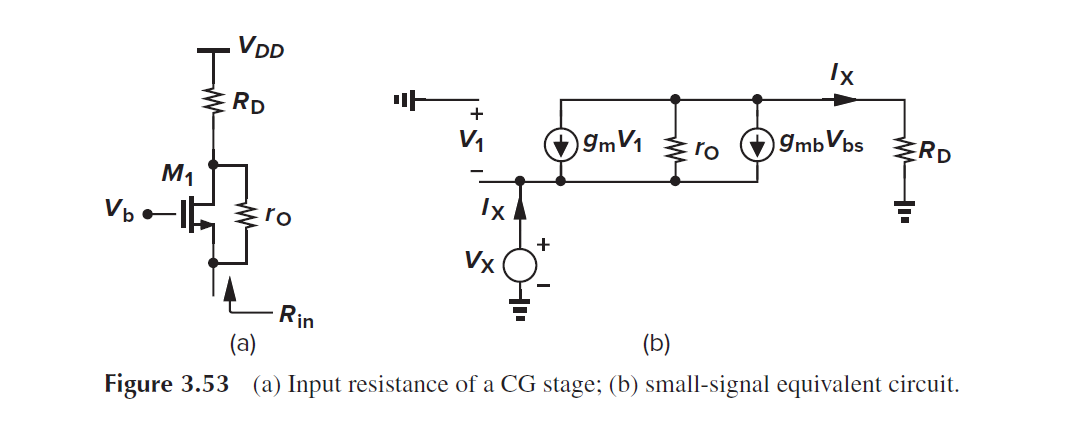

考虑CG的输入阻抗

Rin输入阻抗:

当RD=0, Rin=1/gm, 即CG从source看进去的阻抗为1/gm.

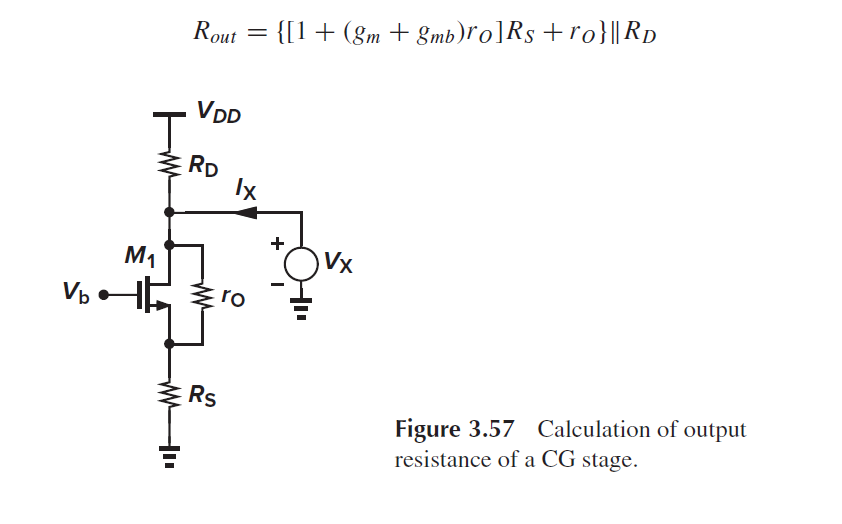

计算CG的输出电阻, 可认为是casecode(gm*ro *rs)并联RD

3.6 Cascode Stage

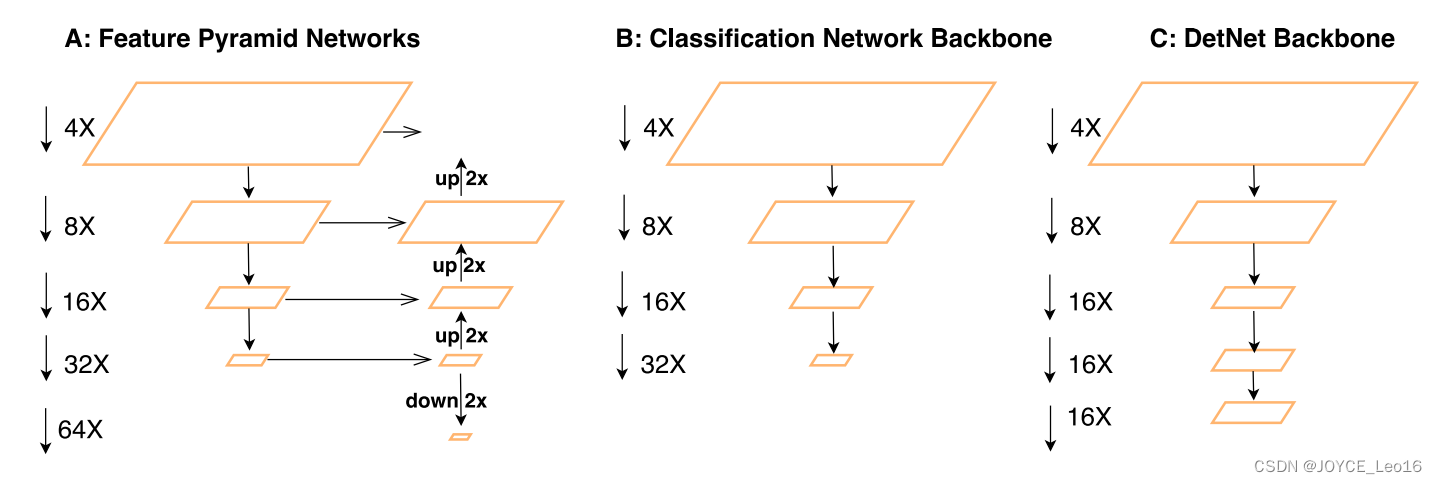

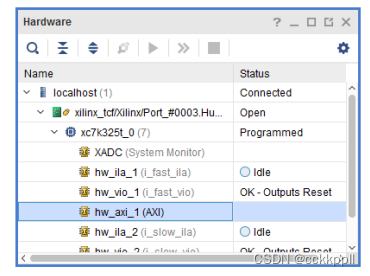

一个典型的cascode结构如下图所示. Vin通过M1转换为电流, 流过M2和RD. M1称为 input device, M2称为 cascode device.

输入Vin变化V, 输出电流变化gm1*V, X电压变化gm1/gm2 *V.

Output Resistance

R o u t = g m r o 2 r O 1 R_{out}=g_mr_{o2}r_{O1} Rout=gmro2rO1

最低电压值: 2Vdsat=2(Vgs-Vth)

对于cascode电流镜, 如下图所示

电压增益

注意, 两个电流镜直接硬怼到一起, Vout DC工作点肯定偏的很厉害, 需要负反馈环路来调节Bias来控制.

Poor Man’s Cascode 极简主义cascode如下图所示. M2处于线性区. 因为Vgs1>Vth1, Vds2=Vgs2-Vgs1<Vgs2-Vth2. 当然如果M1和M2尺寸相同, 那么相当于M1的W/L减小一倍 (L double).

在现代CMOS工艺中, M1和M2的阈值可以不同. 选取M1为low Vth管子, M2为normal Vth管子, 即Vth1<Vth2, 而且Vgs1<Vth2, 就可以让M2工作在饱和区. 例如Vth2-Vth1=150mV, Vgs1-Vth1<100mV, 那么M2工作在饱和区了.

Shielding Property

如下图所示, cascode的高阻抗在于, 当输出变化V时, M1的source变化幅度远小于V, 因此cascode管子“屏蔽”了输出电压对输入电压的影响. 这一点在实际电路设计中很有用.

a) 没有cascode X和Y电压变化对电流的影响

b) 考虑casecode结构, X Y电压变化导致电流变化的值减小了gm3*ro3倍

当输出电压过低, 导致cascode管M3,M4进入线性区, 那么“屏蔽”效应会大打折扣, M3和M4的source会随着输出X和Y变化, 那么channel length modulation效应就能体现了.

3.6.1 Folded Cascode

folded cascode指的是cascode的input device和cascode device是不同类型的MOS, 例如一个NMOS, 一个PMOS. 为了保证正常工作, 相比传统套筒式telescopic cascode, folded cascode需要用更多的电流偏置, 如下图所示:

3.7 Choice of Device Models

gain, Vout的表达式可以很简单, 例如degerated cs, gain=-RD/(Rs+1/gm)也可以很复杂. 在实际电路设计分析中, 先把复杂电路分解为一个个小的熟悉的模块, 对于小的模块就用最简单的gm*Vgs模型 (不带ro). 如果drain连接高阻节点, 就添加ro. 这样大部分电路的基本原理都能知道了. 如果还要更准确, 就迭代body effect.

对于bias计算, 一般可以忽略channel-length modulation和body effect, 就算引入误差, 也可以通过下一步迭代来更正.

先思考想清楚电路原理, 再通过仿真看电路performance, “Don’t let the computer think for you.” & “Don’t be a SPICE monkey.”