一、设备概述

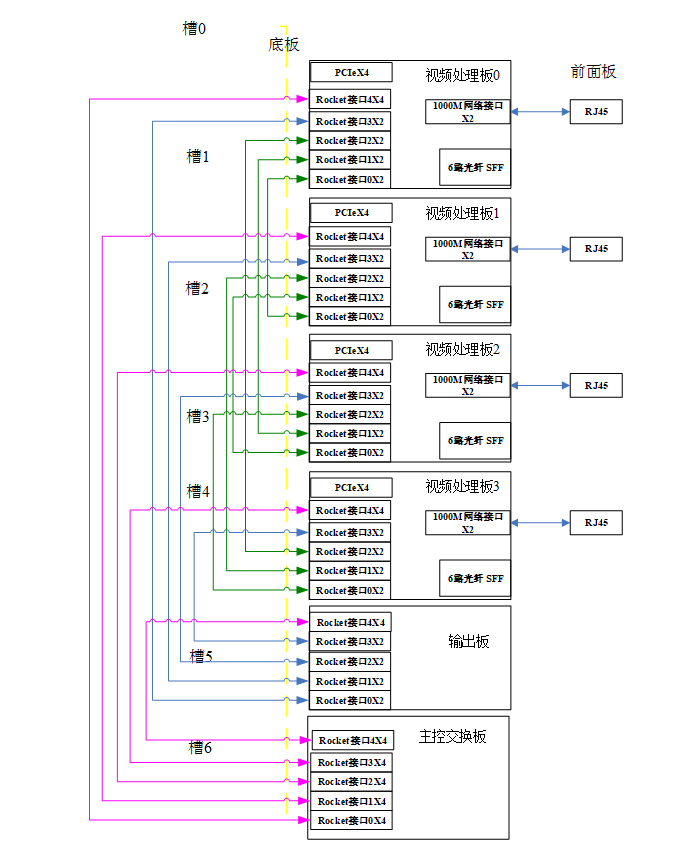

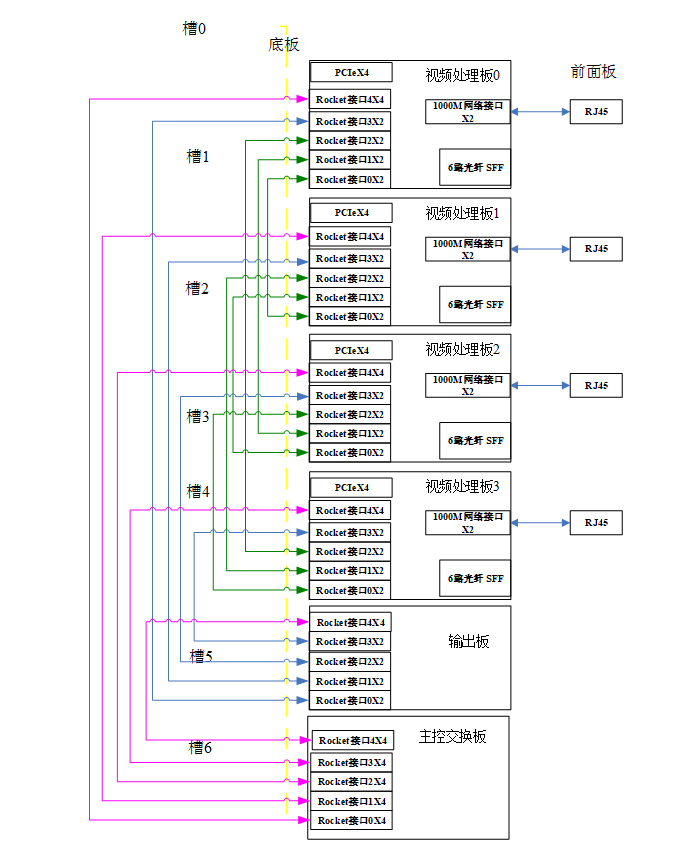

设备基于6U CPCIe架构,通过背板交换实现4片信号处理板卡的互联传输,每个信号处理板卡支持双TMS320C6678,支持2路光纤的图像处理,实现FPGA的预处理和备份工作。

二、6U CPCIe的双DSP信号处理板

处理板技术指标 1.板卡要求采用双片TI DSP TMS320C6678芯片,8核,主频1G。 2.板卡采用Xilinx公司FPGA XC7K420T-1FFG1156 芯片。 3.前面板 两个DSP各出一个千兆网口,另外2个网络连于背板。 4.前面板FPGA出两个千兆网口,6个SFF模块光纤,支持5Gbps 5.前面板出4个指示灯,1个复位按钮。 6.DSP与FPGA之间 RapidIOX4互联,DSP的Uart,SPI,I2C连接于FPGA。 7.DSP 之间 Hyperlink X4 互联。 8.FPGA 提供12个GTX连于背板,支持4个X2,1个X4的工作模式配置。GTX高工作频率为6.25Gbps。 9.每颗DSP外接1GB的DDR3,64bit位宽;32MB Nor Flash. 10.FPGA 外接2组DDR3,各512MB,64bit位宽,32MB Nor Flash,在原理图设计阶段,如FPGA的I/O引脚资源不够,则可将DDR3位宽调整为32BIT宽。 11.DSP 支持远程网络加载,PCIe加载;FPGA支持Master SelectMAP和Master BPI加载,同时支持DSP0或者DSP1的SPI口对FPGA进行动态加载和对配置芯片程序更新。 12.FPGA连接不少于160根普通IO到CPCIe的P4,P5连接器。 13.FPGA能读取背板槽位信息,ID[3:0]。 14.FPGA 外接E2PROM。 15.板卡芯片要求工业级。 16.供电 采用 +5V +12V 双电源。 17.板卡结构标准CPCIe 6U大小。 18.整板冷却,支持加固。 三、软件内容

|