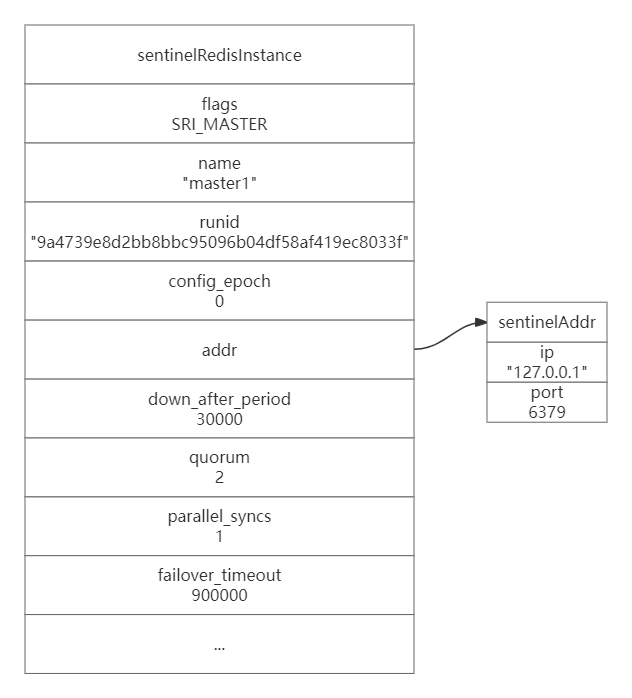

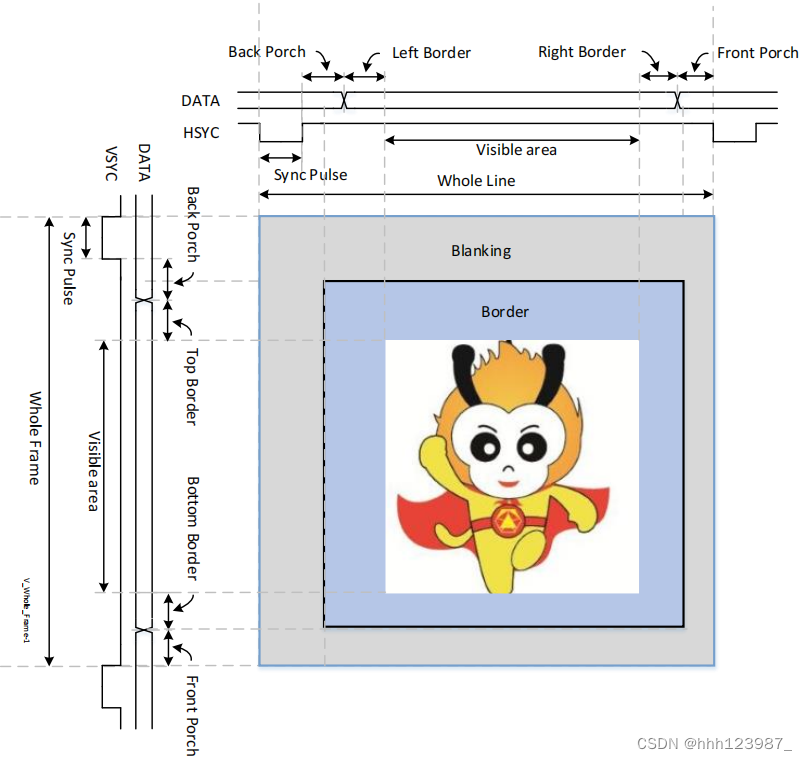

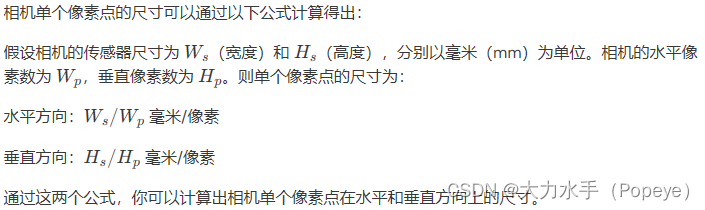

1. VGA 时序标准

| 小梅哥视频链接:23A VGA成像原理与时序详解_哔哩哔哩_bilibili |

|

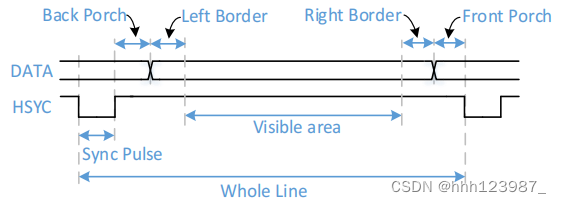

| 行扫描时序图 |

|

| 场扫描时序图 |

|

| 具体参数自己查表 |

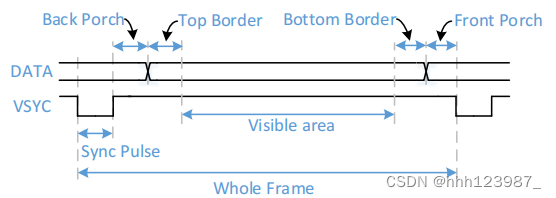

2. 640*480 分辨率 VGA 控制器时序分析

2.1 行扫描区间构成

|

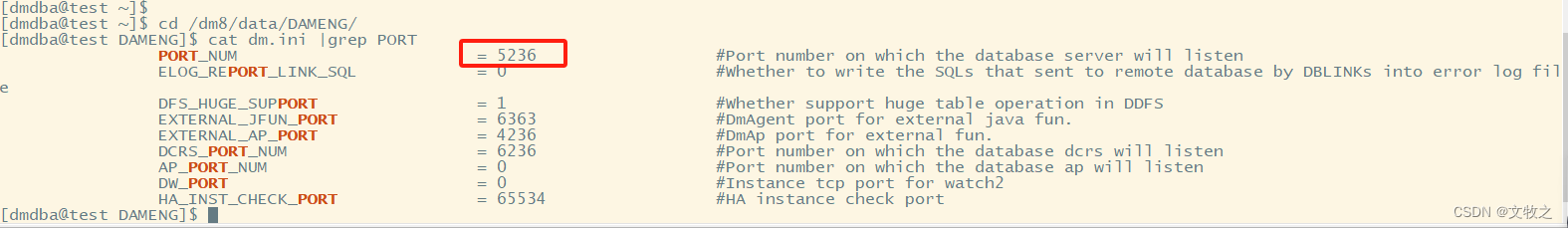

H Sync Time

|

H Bach Porch | H Left Border | H Data Time | H Right Border | H Front Porch |

| 96 vclk | 40 vclk | 8 vclk | 640 vclk | 8 vclk | 8 vclk |

行计数器: HS 脉冲信号结束 (VGA_HS_end)

图像数据开始输出(hdat_begin)

图像结束 输出(hdat_end),

行扫描停止(hpixel_end)

| 时间节点参数 | VGA_HS_end | hdat_begin | hdat_end | hpixel_end |

| 节点值clk | 95 | 143 | 783 | 799 |

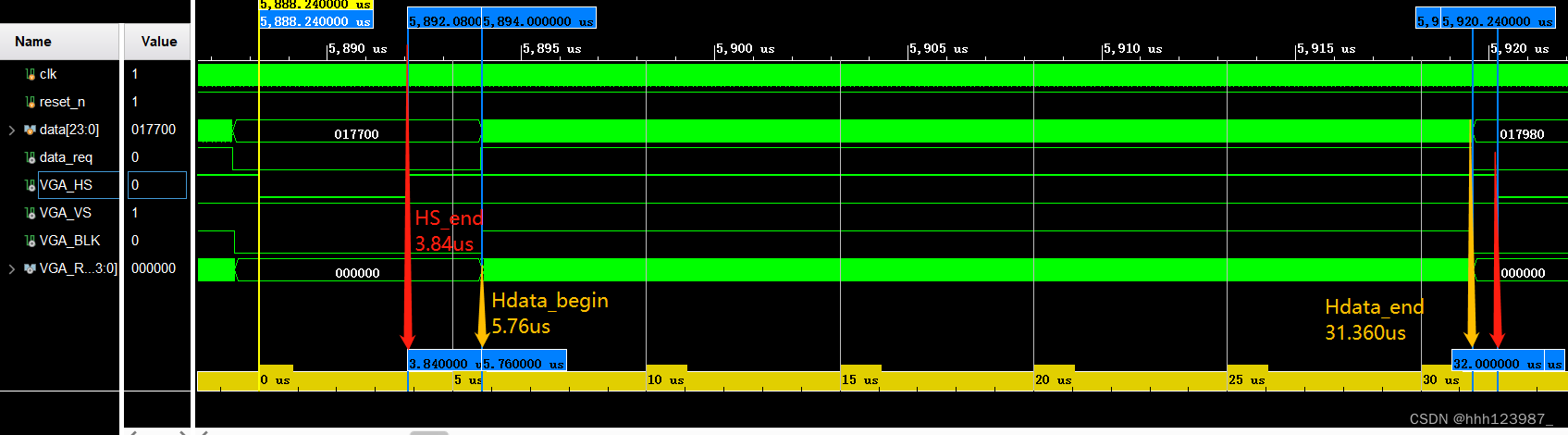

2.2 场扫描区间构成

|

V Sync Time

|

V Bach Porch | V Left Border | V Data Time | V Right Border | V Front Porch |

|

2 lines

|

25 lines | 8 lines | 480 lines | 8 lines | 2 lines |

场扫描 是以一次行扫描的时间为单位。

场计数器: VS 脉冲信号结束 (VGA_VS_end)

图像数据开始输出(vdat_begin)

图像结束 输出(vdat_end),

行扫描停止(vline_end)

| 时间节点参数 | VGA_VS_end | vdat_begin | vdat_end |

vline_end

|

| 节点值line | 1 | 34 | 514 | 524 |

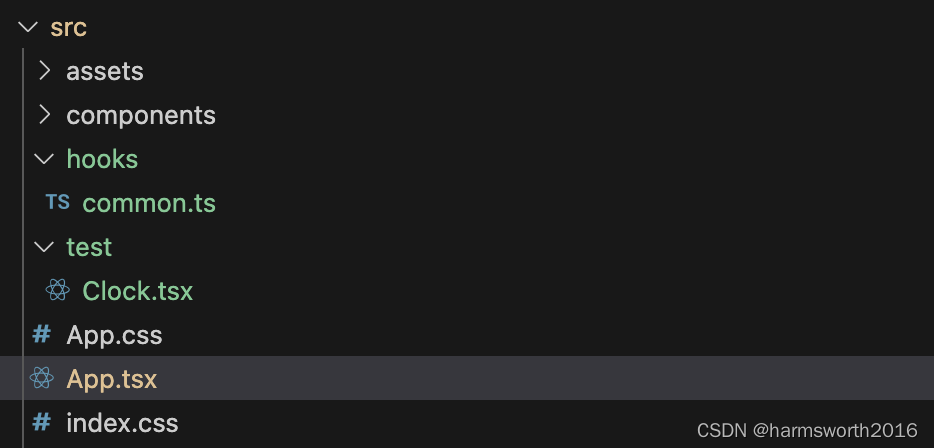

3. Verilog 实现

3.1 design sources

module vga(

input clk ,

input reset_n ,

input [23:0]data ,

output reg data_req ,

output reg VGA_HS ,

output reg VGA_VS ,

output reg VGA_BLK ,

output reg [23:0]VGA_RGB

);

parameter VGA_HS_end = 95 ;

parameter Hdat_begin = 143 ;

parameter Hdat_end = 783 ;

parameter Hpixel_end = 799 ;

parameter VGA_VS_end = 1 ;

parameter Vdat_begin = 34 ;

parameter Vdat_end = 514 ;

parameter Vline_end = 524 ;

//行计数器

reg[9:0]H_cnt;

always@(posedge clk or negedge reset_n)

if(!reset_n) H_cnt <= 0 ;

else if(H_cnt == Hpixel_end)

H_cnt <= 0 ;

else

H_cnt <= H_cnt + 1'b1 ;

// 场计数器

reg[9:0]V_cnt;

always@(posedge clk or negedge reset_n)

if(!reset_n) V_cnt <= 0 ;

else if(H_cnt == Hpixel_end)

if(V_cnt == Vline_end)

V_cnt <= 0 ;

else

V_cnt <= V_cnt + 1'b1 ;

else

V_cnt <= V_cnt ;

// VGA_HS

always@(posedge clk or negedge reset_n)

if(!reset_n) VGA_HS <= 1;

else if(H_cnt == 0) VGA_HS <= 0;

else if(H_cnt > VGA_HS_end) VGA_HS <= 1;

// VGA_VS

always@(posedge clk or negedge reset_n)

if(!reset_n) VGA_VS <= 1;

else if(V_cnt == 0) VGA_VS <= 0;

else if(V_cnt > VGA_VS_end) VGA_VS <= 1;

// data_req

always@(posedge clk or negedge reset_n)

if(!reset_n) data_req <= 0 ;

else data_req <= ((H_cnt >= Hdat_begin)&&(H_cnt < Hdat_end)&&(V_cnt >= Vdat_begin)&&(V_cnt <= Vdat_end)) ? 1 : 0;

// VGA_BLK

always@(posedge clk or negedge reset_n)

if(!reset_n) VGA_BLK <= 0 ;

else VGA_BLK <= data_req ;

// VGA_RGB

always@(posedge clk )

if(data_req) VGA_RGB <= data ;

else VGA_RGB <= 0 ;

endmodule

3.2 vga_tb

`timescale 1ns / 1ns

module vga_tb( );

reg clk , reset_n;

reg [23:0]data;

wire data_req ,VGA_HS ,VGA_VS ,VGA_BLK;

wire [23:0]VGA_RGB;

vga vga_(

clk ,

reset_n ,

data ,

data_req ,

VGA_HS ,

VGA_VS ,

VGA_BLK ,

VGA_RGB

);

initial clk = 1 ;

always#20 clk = ~clk ;

initial

begin

reset_n = 0 ;

#201 ;

reset_n = 1 ;

#40000000;

$stop;

end

always@(posedge clk or negedge reset_n)

if(!reset_n) data <= 0 ;

else if(data_req) data <= data + 1'b1 ;

else data <= data ;

endmodule

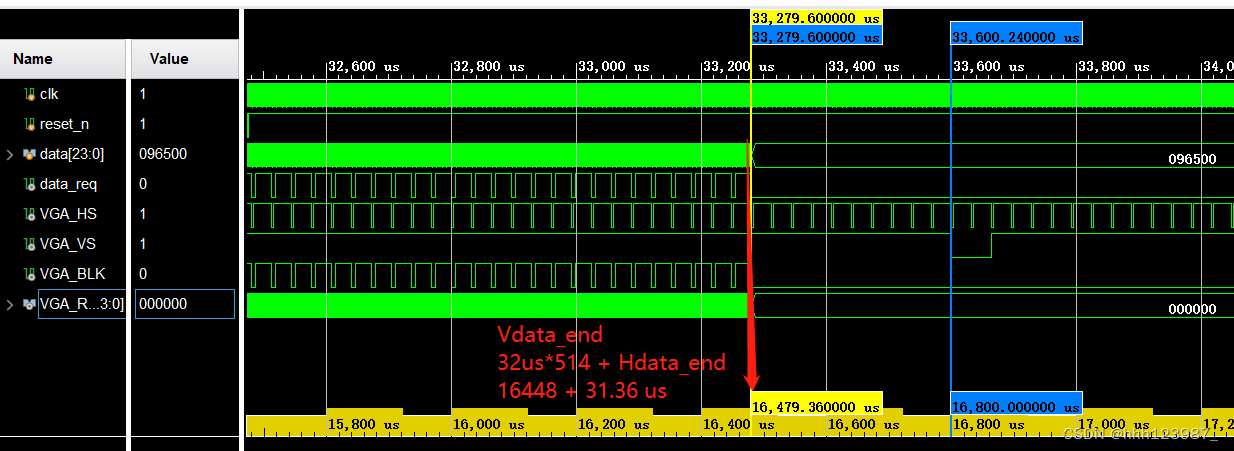

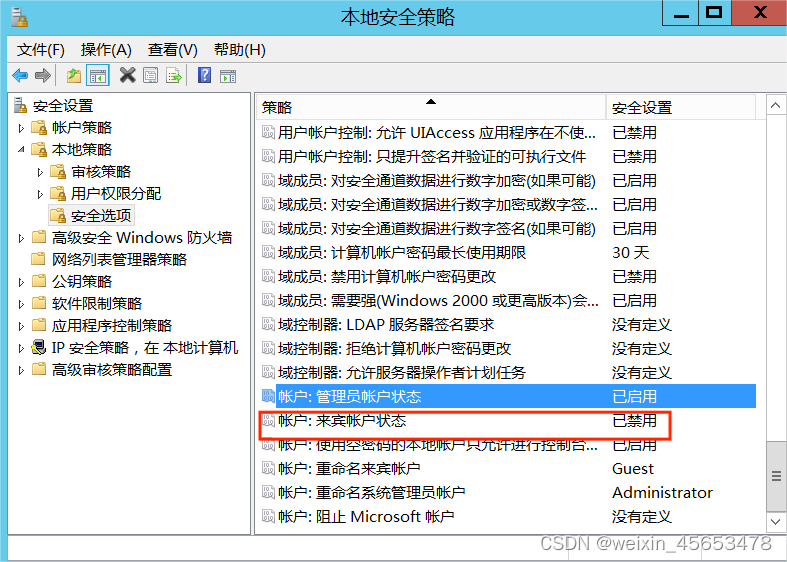

3.3 测试结果

| 行扫描 周期32us |

|

| 场扫描 周期16.8ms |

|

|

| 调试data_req算了好久,下班班哩~ |

![[数据结构初阶]堆的应用](https://img-blog.csdnimg.cn/direct/faa70bbff9c846f5ad09ff9c11c00c4c.webp)

![[VulnHub靶机渗透] pWnOS 2.0](https://img-blog.csdnimg.cn/direct/0a9aee202e9941888ac104ec7fb071fb.png)