一、计算机层次化结构存储

计算机层次化结构存储是基于 存储速度、内存大小、成本高低等条件的综合性价比考量的结构理念。

1.Cache

Cache:

存在于CPU与内存之间,提高CPU的输入输出速率,突破冯诺依曼瓶颈(即CPU与存储系统之间数据传送的带宽限制)

在计算机测存储体系中Cache是除寄存器外访问速度最快的层次

使用Cache改善系统性能的依据是程序的局部性原理

2.Cache相关计算

t1:表示Cache的周期时间

t2:表示主存储器的周期时间

h:表示对Cache的访问命中率(1-h)表示失效率或未命中率

t3:表示Cache+主存储器的系统的平均周期

t3 = h*t1+(1-h)*t2

例如:Cache的访问命中率为 h=95%,Cache的周期时间为 t1=1s,主存储器的周期时间为 t2=1000s,Cache+主存储器的体统平均周期 t3 为?

t3=95%*1s+(1-95%)*1000s=50.95s

3.局部性原理

局部性原理分为 时间局部性 和 空间局部性

工作集理论:进程运行时被频繁访问的部分集合,即将频繁运行的部分打包调入高速运算存储中短时间内内不被替换

由上述可知,速度快的部件往往成本高所以一般只能用于操作小容量,例如寄存器,而存储容量大且成本低的部件往往速度慢,所以出于最佳性价比考虑,引入局部性原理,将需要频繁访问的局部调到速度快的部件中参与快速运算,以此提高效率。

时间局部性:例如循环体中,条件部分需要频繁执行,所以将其放入Cache中快速调取参与计算以提高效率。

(可理解为刚刚访问完的部分后面需要紧接着多次访问)。

空间局部性:例如数组 a[ ] 中,将数组 a[ ] 初始化,将a[0]初始化后紧接着需要将a[1],a[2],a[3]等紧邻部分分别初始化,

(可以理解为访问部分空间后紧接着访问多个邻近空间)。

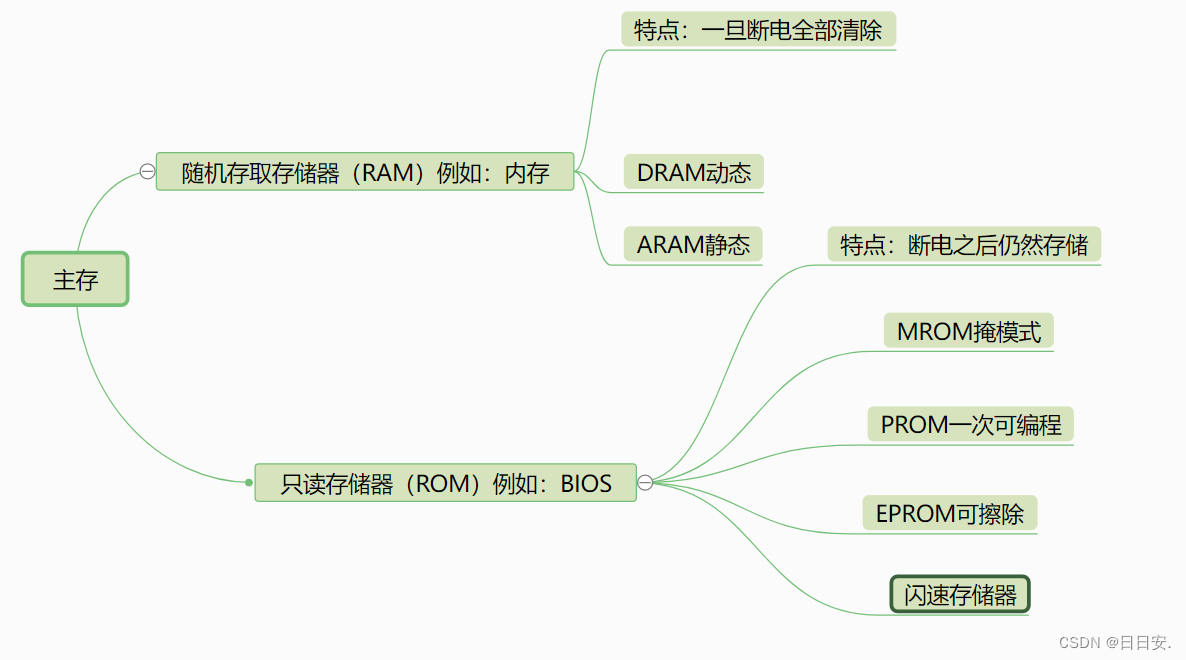

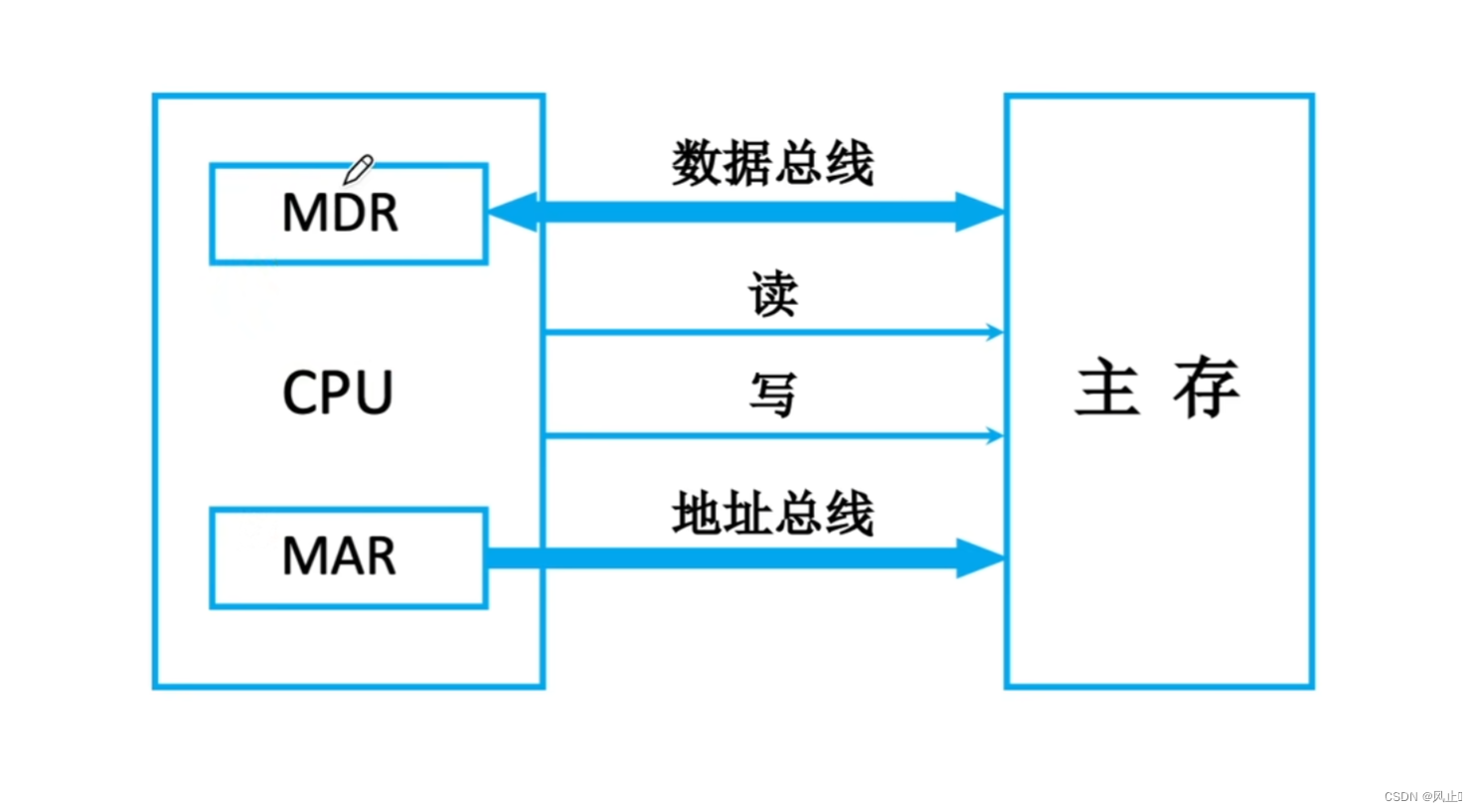

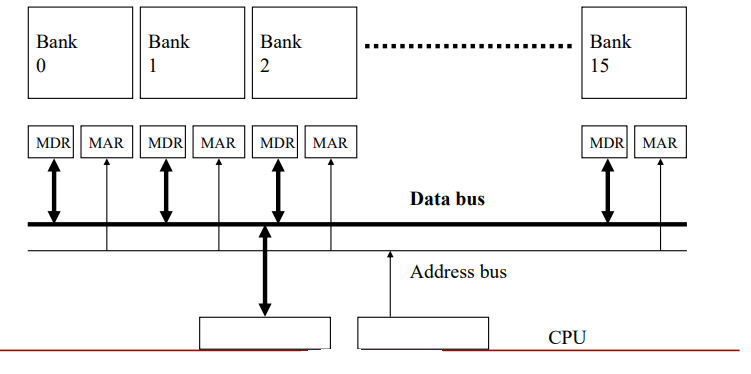

二、主存(又称 内存/主存储器)

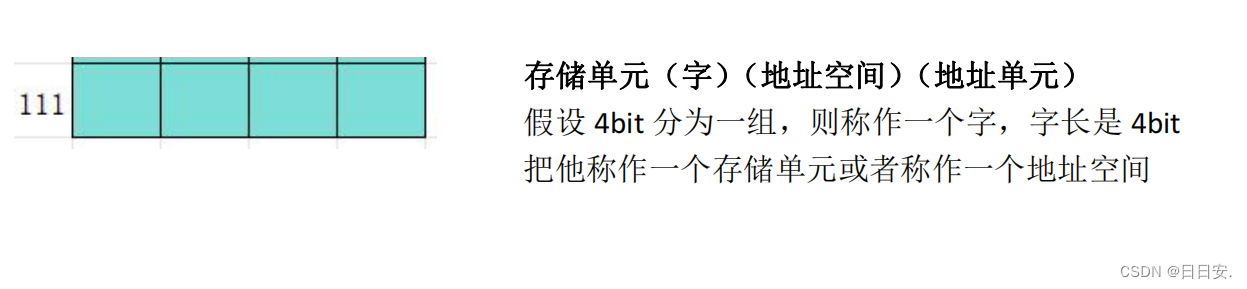

1.编址

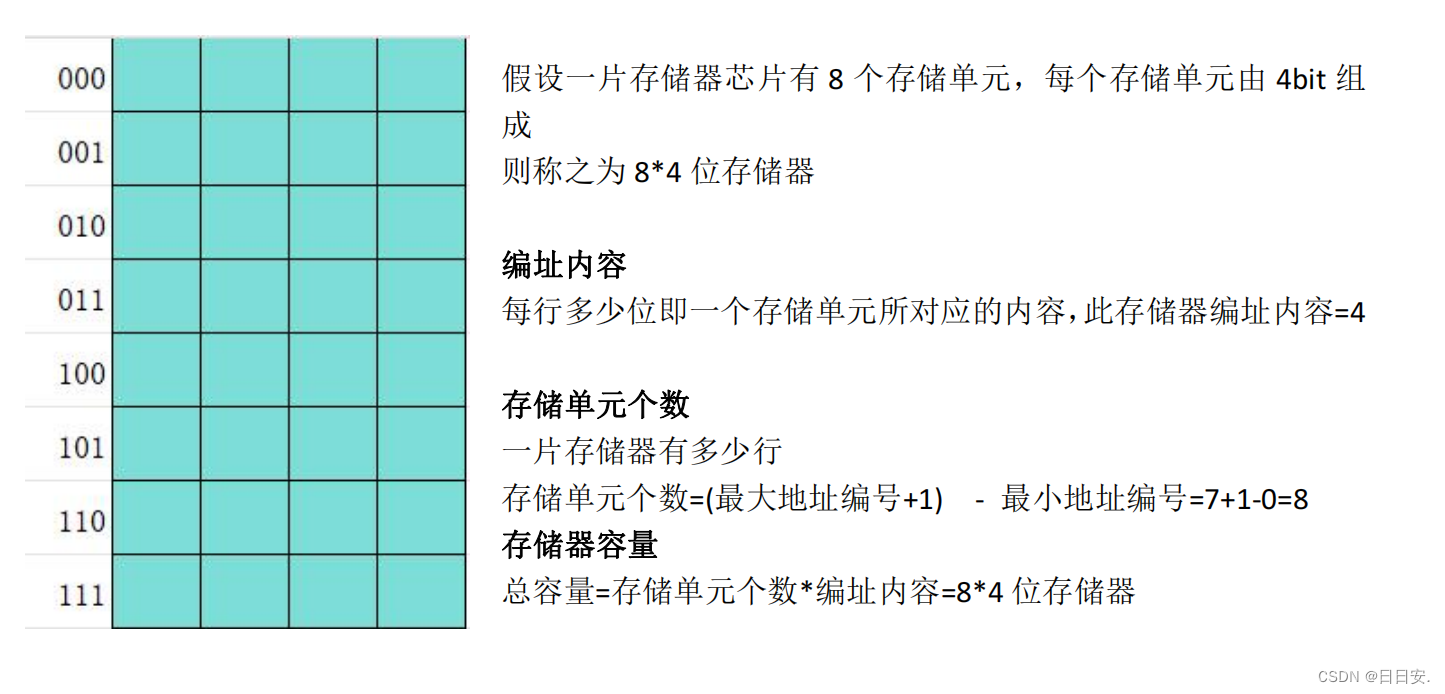

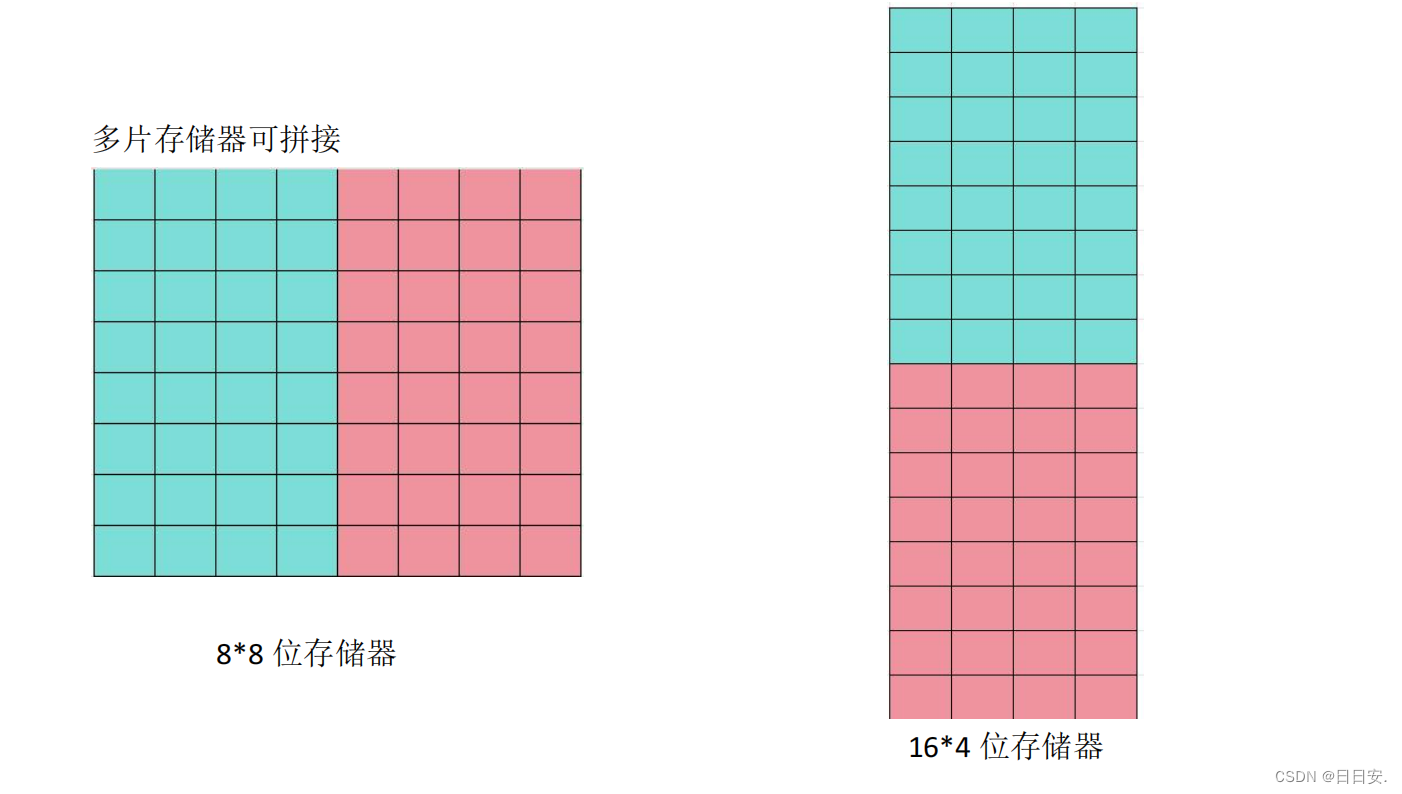

将单个存储器组成相应大小的存储器(什么规格的存储器,需要多少块,组成多大的存储器)

例题

内存地址从AC000 H到C7FFF H,共有__112___K个地址单元,如果该内存地址按字(16bit)编址,由28片存储器芯片构成。已知构成此内存的芯片每片16K个存储单元,则该芯片每个存储单元存储__4___位。

解:

此题中AC000 H,C7FFF H为地址编号

求地址单元个数(存储单元个数)= (最大地址编号+1)- 最小地址编号

地址单元个数 = (C7FFF+1) - AC000 = C8000-AC000 = 1C000 H(十六进制运算)

1C000(十六进制)=1 * +C *

=1*65536 + 12 * 4096 = 114688(十进制)

注:题中单位是K需进行转化 114688 B / 1024 = 112K

地址单元个数 = 112K

内存有112K个存储单元,每个存储单元字长是16bit(即编址内容为16)

题中需求存储器总容量=存储单元个数*编址内容 = 112K*16

设每片存储器芯片存储单元有x位(xbit)

此存储器芯片每片16K个存储单元

一片存储器芯片总容量=存储单元个数*编址内容=16K*x

28片存储器芯片总容量=28*16K*x

自题目中知:题中需求芯片由28片16K*x容量的存储器芯片构成,所以

题中需求存储器总容量=28片存储器芯片总容量

即112K*16=28*16K*x

解得x=4

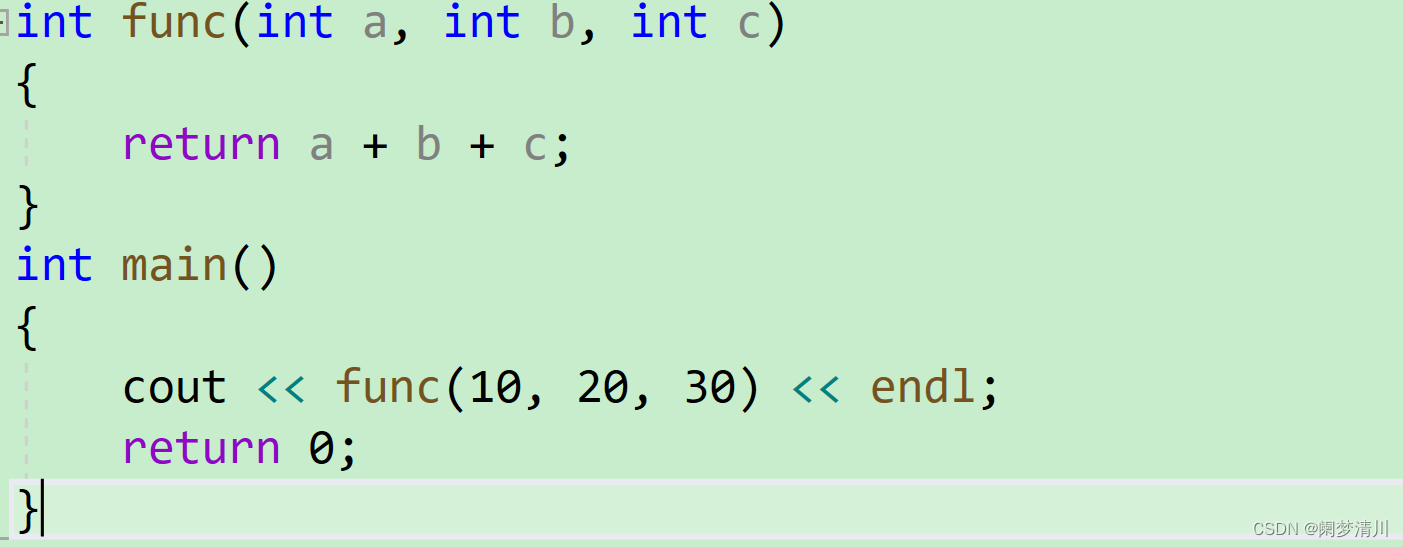

![[lesson02]C到C++的升级](https://img-blog.csdnimg.cn/direct/658846ad55964eb7b8ad801e2be8c177.png#pic_center)