目录

一、概述

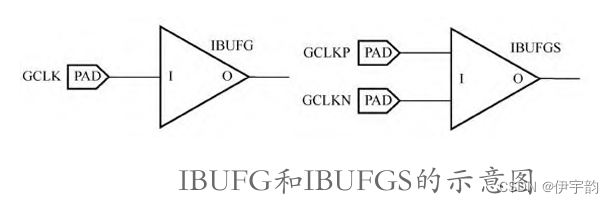

在 FPGA 设计中,将外部用户时钟引入 FPGA 是一项重要的任务,对整个系统的性能和稳定性有着直接影响。为了实现这一点,外部时钟必须通过称为时钟可用(Clock-Capable, CC)输入的差分时钟引脚对引入。

1.1 为什么使用CC

CC提供了到内部全局和区域时钟资源的专用、高速访问路径。这是因为它们使用专用的布线,最小化了信号传播延迟和抖动,从而确保了时钟信号的质量和时序精度。

保证时序:为了保证各种时钟特性的时序,必须使用时钟能力输入作为时钟信号的输入。这些特性可能包括时钟分频、时钟选择、时钟门控等复杂的时钟管理功能。

避免使用通用I/O:通用I/O引脚通过局部互连接入FPGA,这些互连并不为高速时钟信号设计,使用它们传输时钟信号可能会导致时序问题、增加信号抖动,从而影响系统的稳定性和性能。

1.2 如何使用CC

差分信号:为了最大限度地减少噪声和提高信号完整性,外部时钟通常应该以差分形式引入FPGA。差分时钟信号可以有效地抵消电磁干扰(EMI)和跨越电源或地线引起的电压波动。

专用引脚:设计时,应确保外部时钟信号连接到 FPGA 上指定的时钟能力输入引脚。这些引脚在 FPGA 的数据手册或引脚配置文件中有明确的标识。

布局考虑:在 PCB 设计阶段,应该小心布局差分时钟线,并尽量减少它们的长度和弯曲,以保持信号的完整性。同时,注意避免时钟线与高速数据线或其他可能产生干扰的信号线过于靠近。

通过正确使用CC,设计师可以确保外部时钟信号以最高的质量进入 FPGA,为设计提供稳定可靠的时钟资源。这对于满足严格时序要求、优化性能和保证系统稳定性至关重要。

二、Clock-Capable Inputs

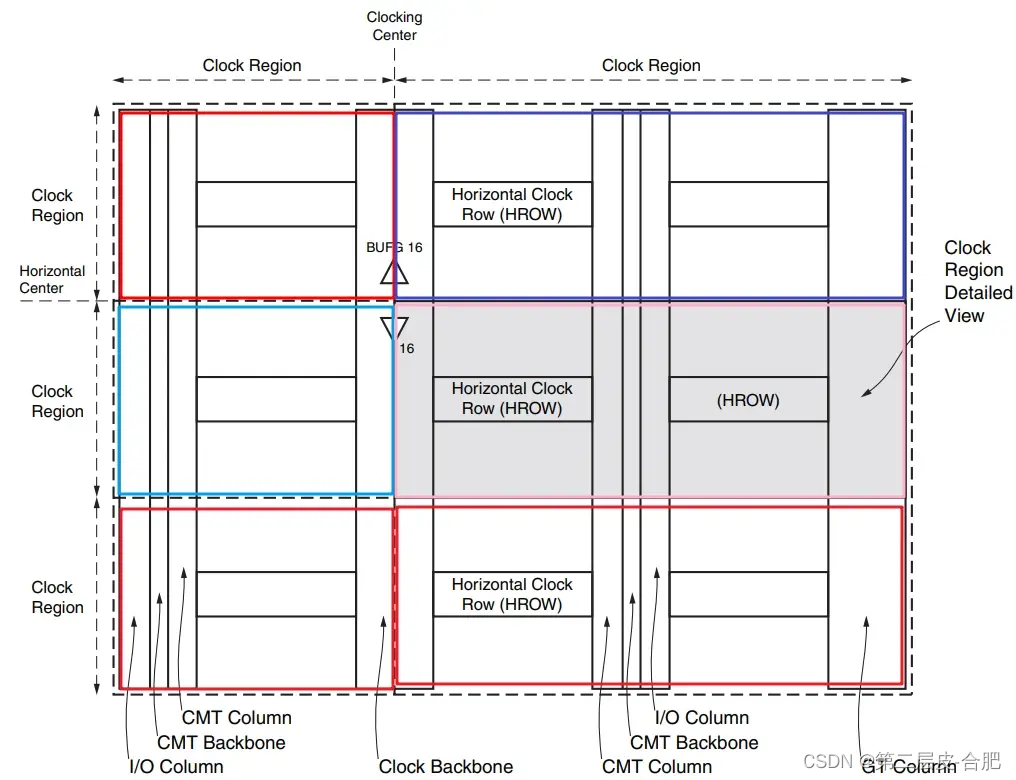

每个 I/O bank位于一个时钟域内,它包含有50个 I/O 引脚。在这50个 I/O 引脚中,有4组CC inputs 引脚对(共8个)。每个 CC input 引脚具有如下的特性:

- 可以连接到PCB上的差分或单端时钟(单端时钟输入必须连接到P端)

- 可以配置成任何I/O标准(包括差分I/O标准)

- 具有P侧(主)和N侧(从)

在 I/O bank 中的这4组CC引脚被划分成2类:2个MRCC和2个SRCC。

2.1 SRCC

SRCC(Single Region Clock Controller)在 Xilinx FPGA 设计中是用于时钟管理的一个重要组件。SRCC 能够访问单个时钟区域(Clock Region)内的资源,同时还能够管理连接到全局时钟树以及位于同一列上下的其他 CMT(Clock Management Tile)的时钟信号。这种设计使得 SRCC 能够支持灵活而高效的时钟分配策略,适应复杂的设计需求。SRCC 能够驱动的时钟线如下:

区域时钟线(BUFR, BUFH, BUFIO):在同一个时钟区域内,SRCC 可以驱动这些区域性的时钟缓冲器。这允许设计师在局部区域内实现精确的时钟分配和管理,优化时钟网络的性能和资源利用。

同一时钟区域及相邻时钟区域内的 CMT:SRCC 能够控制同一区域内及相邻区域的 CMT,提供对更广泛时钟资源的访问和管理能力。这增强了设计的灵活性,允许更复杂的时钟管理方案。

全局时钟线(BUFG):在设备的上半部或下半部,SRCC 可以驱动全局时钟缓冲器(BUFG)。这使得 SRCC 不仅限于局部或区域性的时钟分配,也能够影响整个设备的全局时钟策略,从而实现广泛的时钟网络设计。

2.2 MRCC

MRCC(Multi-Region Clock Controller)是一种在 Xilinx FPGA 设计中用于管理时钟信号的高级组件。与 SRCC(Single Region Clock Controller)类似,MRCC 能够访问和控制时钟信号,但其功能扩展到了多个时钟区域,提供了更广泛的覆盖范围和灵活性。这种设计使得 MRCC 特别适合于那些需要跨越多个时钟区域进行时钟分配和管理的复杂应用。MRCC 的功能如下:

多时钟区域访问:MRCC 能够访问多个时钟区域以及全局时钟树,这使得设计师可以在 FPGA 设计的更广泛区域内实施统一的时钟管理策略。

驱动多时钟区域缓冲器(BUFMR):MRCC 可以驱动 BUFMR,这是一种特殊的时钟缓冲器,用于跨越多达三个时钟区域的时钟信号分配。这种能力对于大型 FPGA 设计至关重要,特别是当设计需要跨越多个逻辑区域协同工作时。

与 SRCC 相同的基本功能:在提供多区域时钟管理的同时,MRCC 保持了与 SRCC 相同的基本功能,包括访问和控制连接到全局时钟树的时钟信号。

2.3 其他用途

Clock-capable inputs是 FPGA 设计中非常灵活的资源,能够根据设计需求作为时钟输入或普通的I/O使用。这种灵活性提供了重要的设计优势,特别是在I/O资源紧张或需要精简设计以节省成本和空间时。下面详细介绍这些功能及其应用:

2.3.1 作为普通I/O使用

I/O标准配置:当不作为时钟使用时,时钟能力输入引脚可以配置为任何单端或差分I/O标准,使其能够兼容不同的电气接口和信号要求。这为设计提供了极大的灵活性,允许设计师根据需要调整每个引脚的功能。

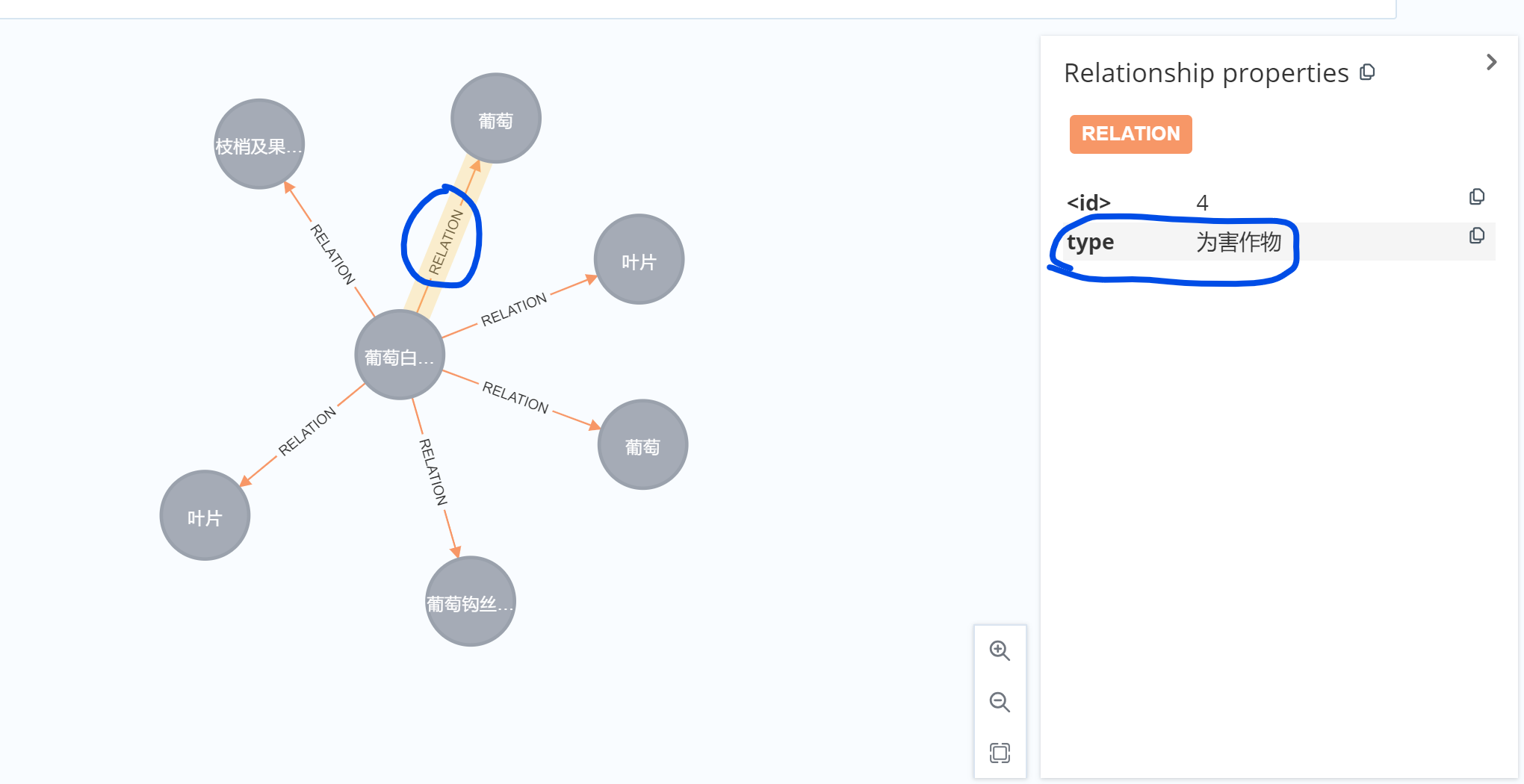

2.3.2 连接到CMT

同一时钟区域的CMT连接:CC input 可以直接连接到同一时钟区域内的时钟管理单元(CMT,Clock Management Tile)。这种连接提供了高效的时钟信号传输路径,有助于实现稳定和精确的时钟分配。

跨区域的CMT连接:CC input 还可以连接到上下相邻时钟区域内的CMT,尽管存在一些限制。这种跨区域的连接能力使得设计师可以更灵活地规划时钟网络,特别是在需要跨越多个时钟区域分配时钟信号的复杂设计中。

![[激光原理与应用-77]:基于激光器加工板卡的二次开发软件的系统软硬件架构](https://img-blog.csdnimg.cn/direct/75d3902fa2004c8b8958bcde2740ffdf.png)