简单双口RAM有两个端口Port A和port B,其中Port A用于写数据,Port B用于读数据,读写接口可以独立时钟工作。这一点和真双口RAM是有区别的,真双口RAM的A B两个Port都可以进行读写操作。

RAM是FPGA中重要的数据结构,可用于数据的缓存和跨时钟域信号处理。本文就xilink 的简单双口RAM 进行读写测试。

本文对简单双口RAM做如下仿真:先对Port A进行连续写操作128次,每次数据和地址加1,结束后开始从Port B口读对应128个地址的数据,读写时钟独立,对比读写数据是否一致。

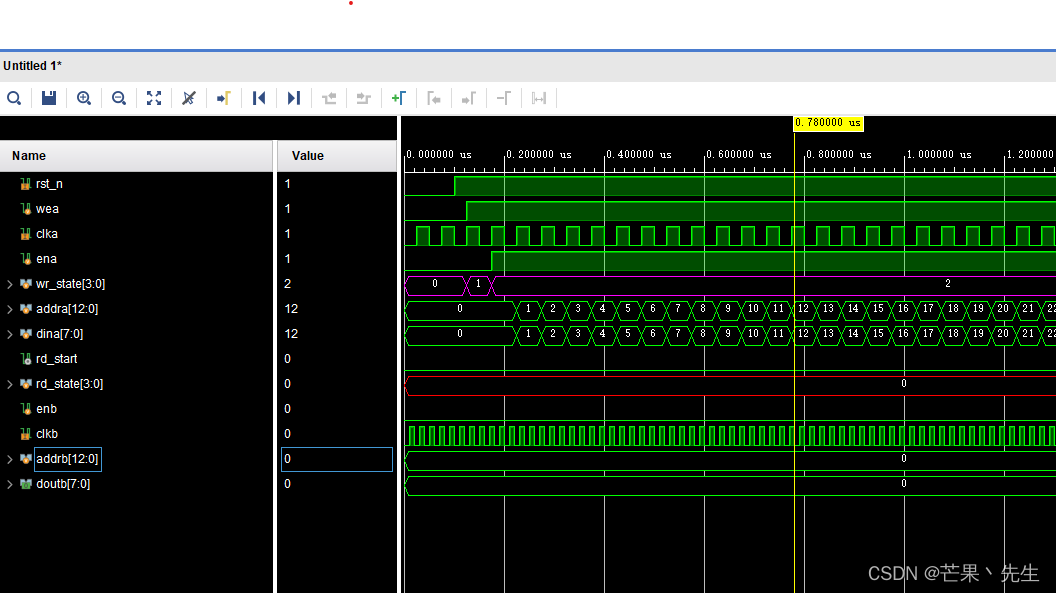

仿真结果如下:

数据写入仿真

数据读出仿真,数据在地址变化后延迟一个时钟输出。

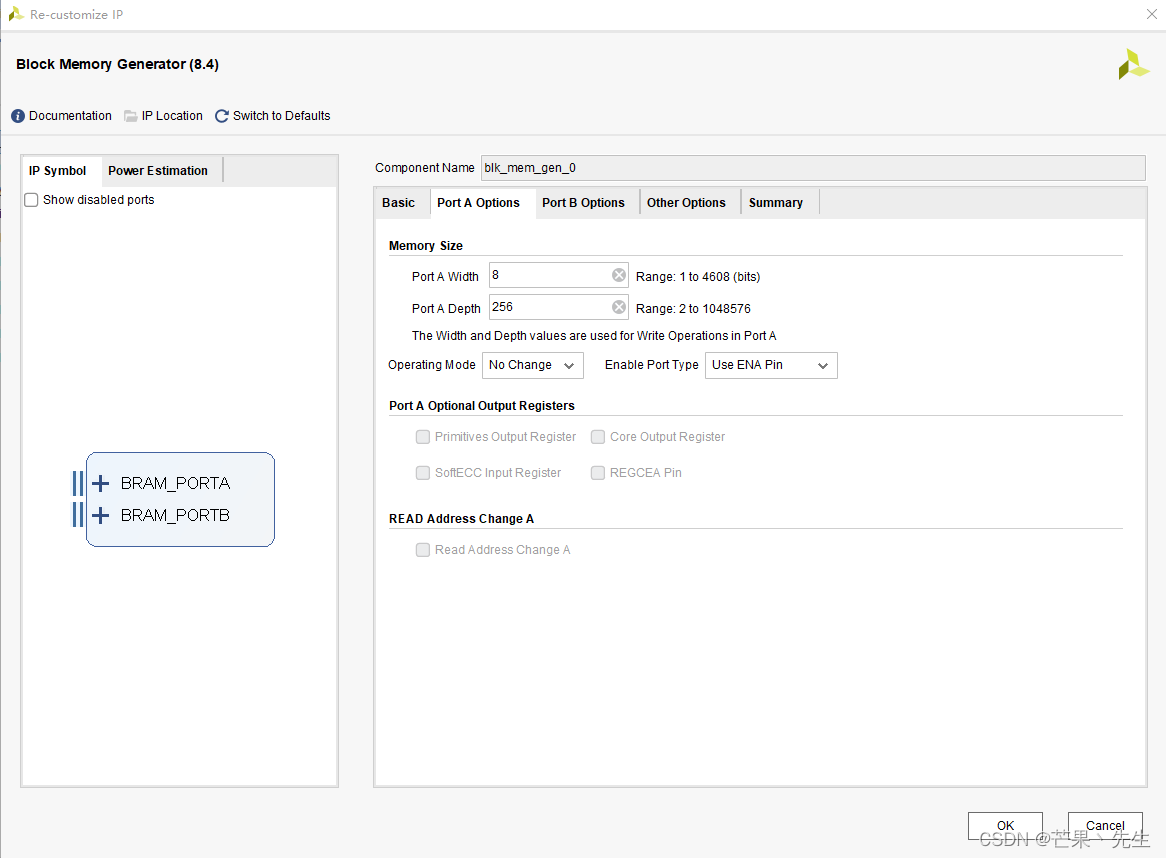

ram ip的设置如下