Q:上一篇里我们创建了全加器,接下来我们使用ModelSim软件对全加器进行仿真。

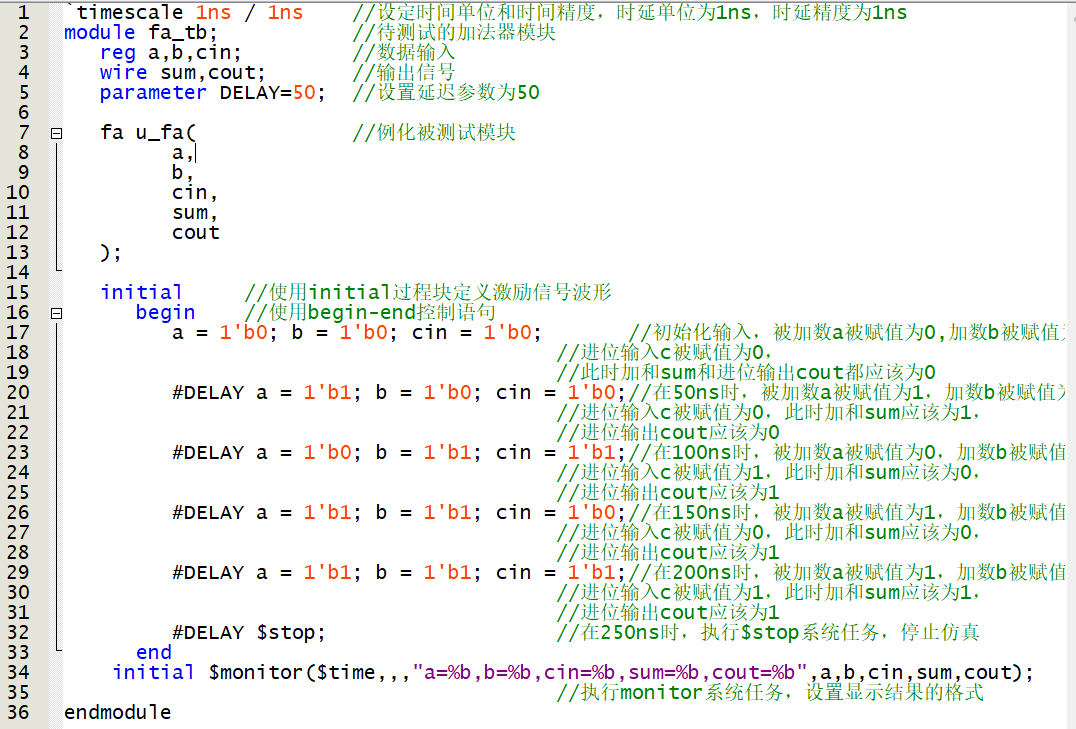

A:编写仿真脚本(Test Bench)文件进行仿真,Test Bench主要是为测试或仿真Verilog程序搭建了一个平台,给被测试的模块施加激励信号,通过观察被测试模块的输出响应,来判断其逻辑功能和时序关系是否正确。

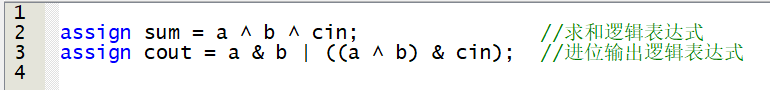

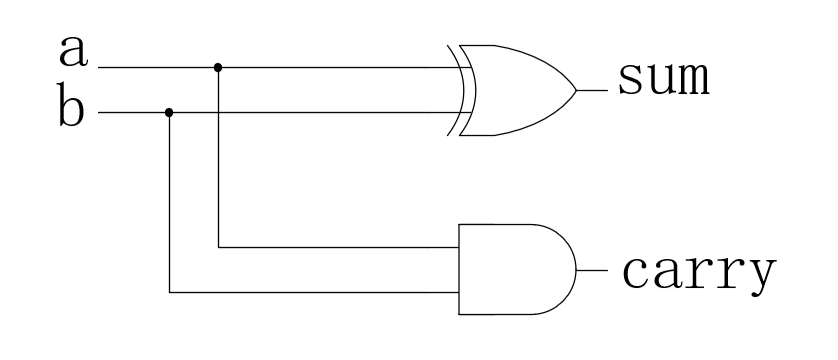

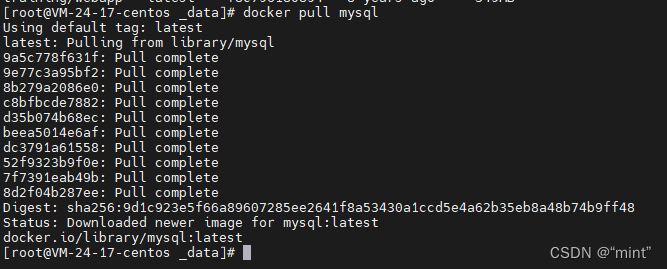

创建全加器的Test Bench文件.v文件:

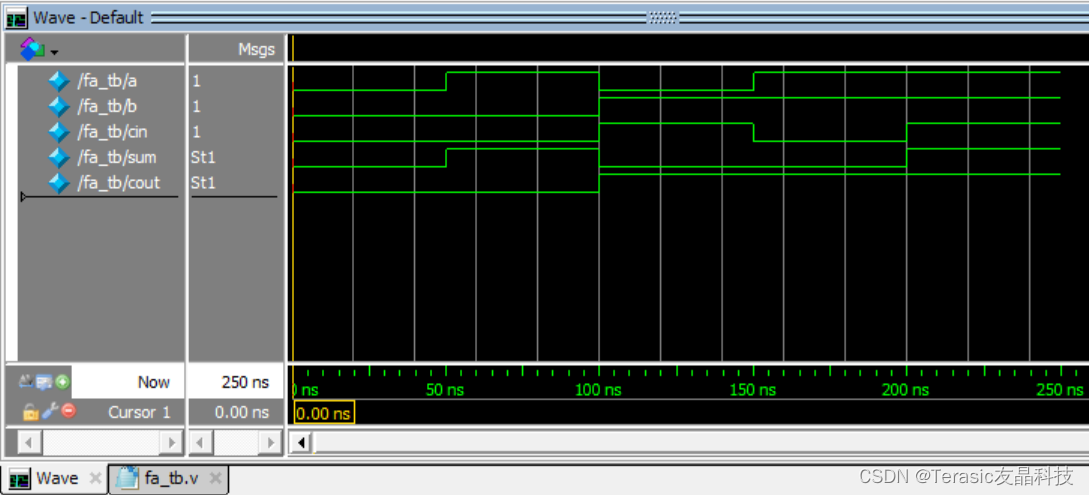

从仿真后的波形图可以看出结果与预期一致,说明全加器功能已实现。

注:还可以参考《University Program VWF仿真步骤__全加器》进行仿真。