Q:上一篇里我们创建了半加器,接下来我们再创建1位二进制数全加器。

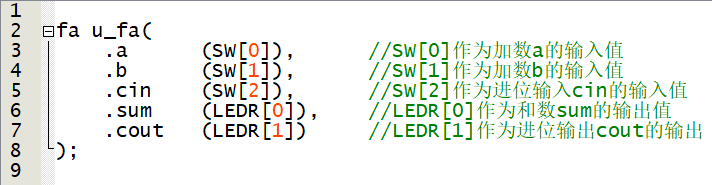

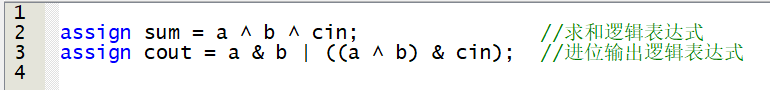

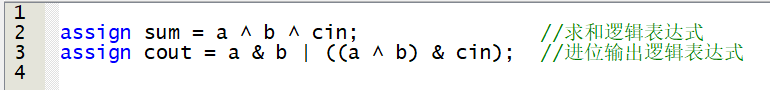

A:基本原理:与半加器不同,全加器要考虑进位输入cin。用Verilog连续赋值语句assign表示为:

全加器真值表:

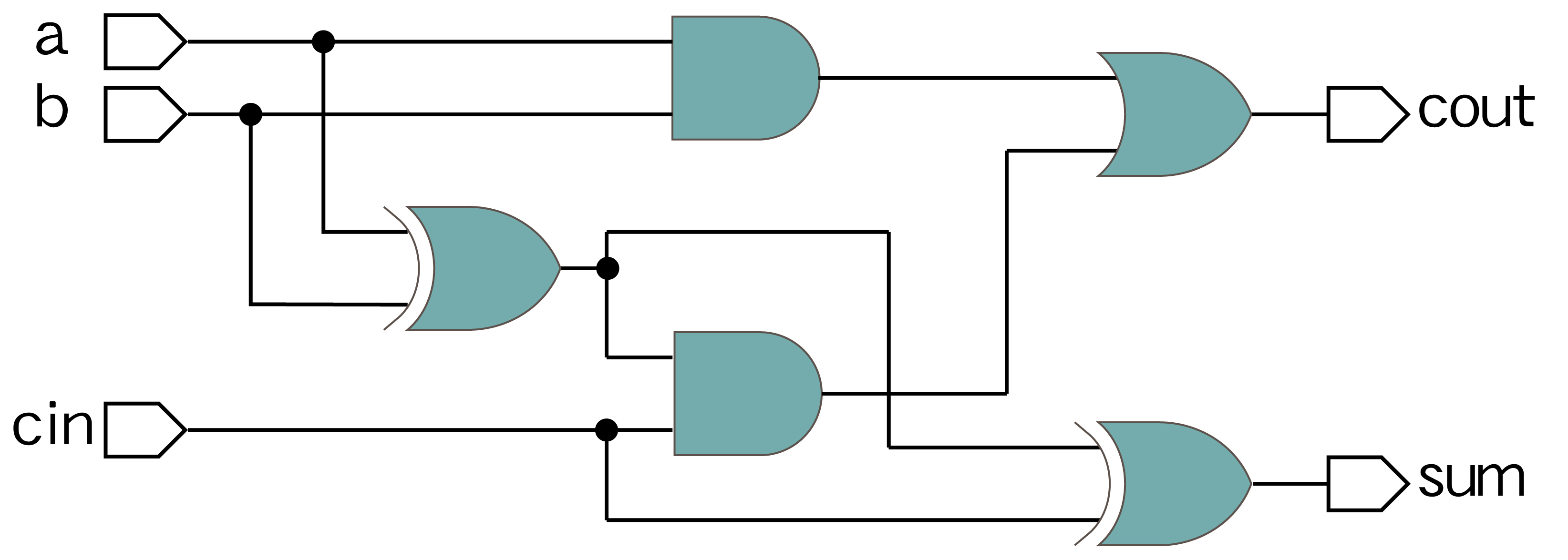

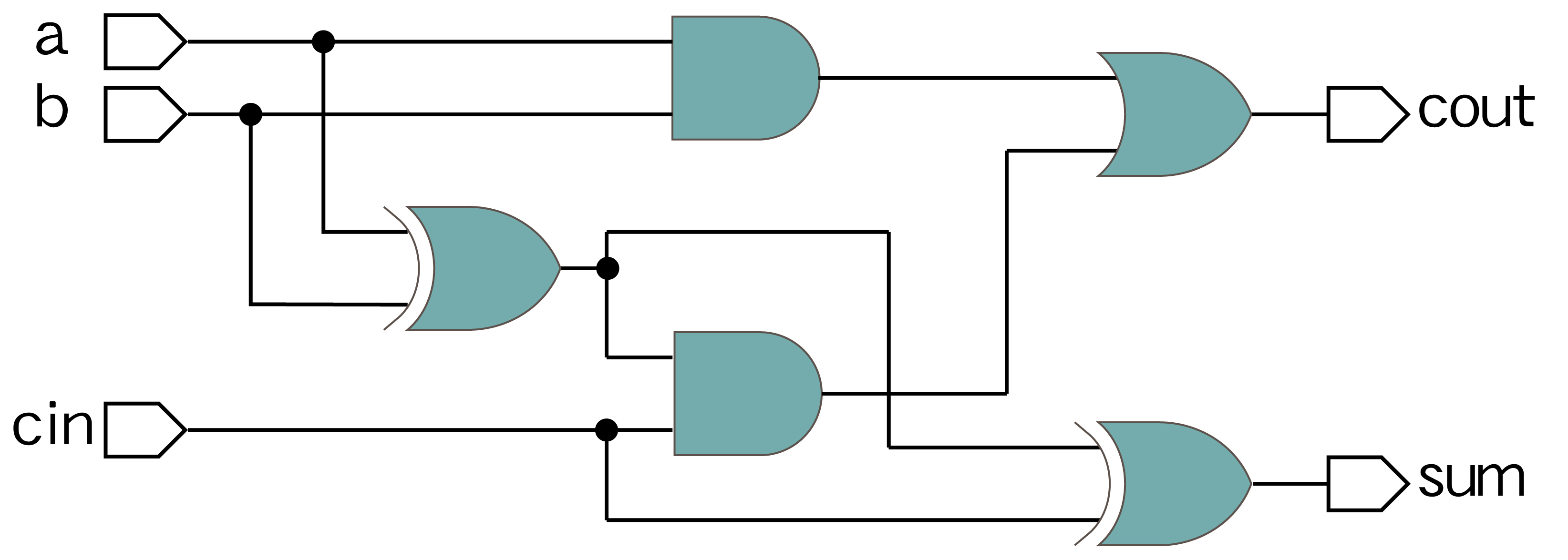

对应的全加器逻辑图:

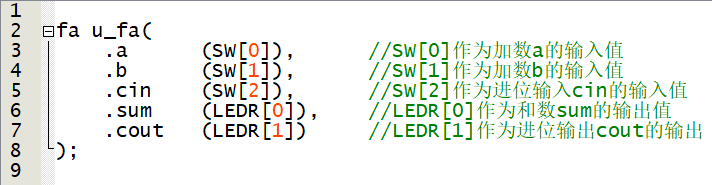

使用DE2-115开发板的SW[0]作为加数a,SW[1]作为加数b,SW[2]作为进位输入cin;LEDR0显示和sum的值,LEDR1显示进位输出cout的值。在顶层.v文件中例化全加器:

Q:上一篇里我们创建了半加器,接下来我们再创建1位二进制数全加器。

A:基本原理:与半加器不同,全加器要考虑进位输入cin。用Verilog连续赋值语句assign表示为:

全加器真值表:

对应的全加器逻辑图:

使用DE2-115开发板的SW[0]作为加数a,SW[1]作为加数b,SW[2]作为进位输入cin;LEDR0显示和sum的值,LEDR1显示进位输出cout的值。在顶层.v文件中例化全加器: