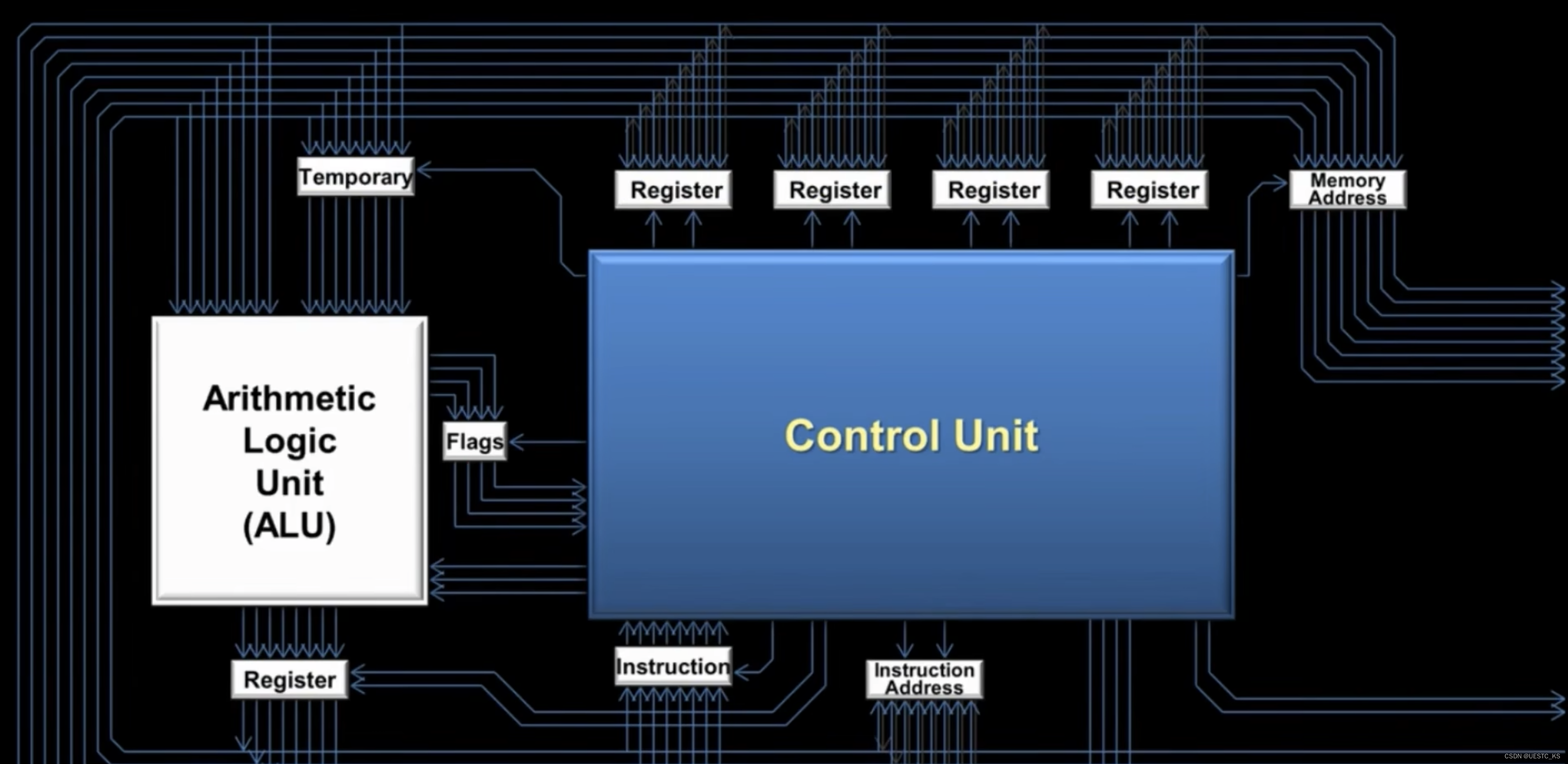

这是一个简单的16位CPU(中央处理单元)的设计实验。这个CPU包括指令存储器、数据存储器、ALU(算术逻辑单元)、寄存器文件和控制单元。

设计一个简单的16位CPU的实验通常可以分为以下几个步骤:

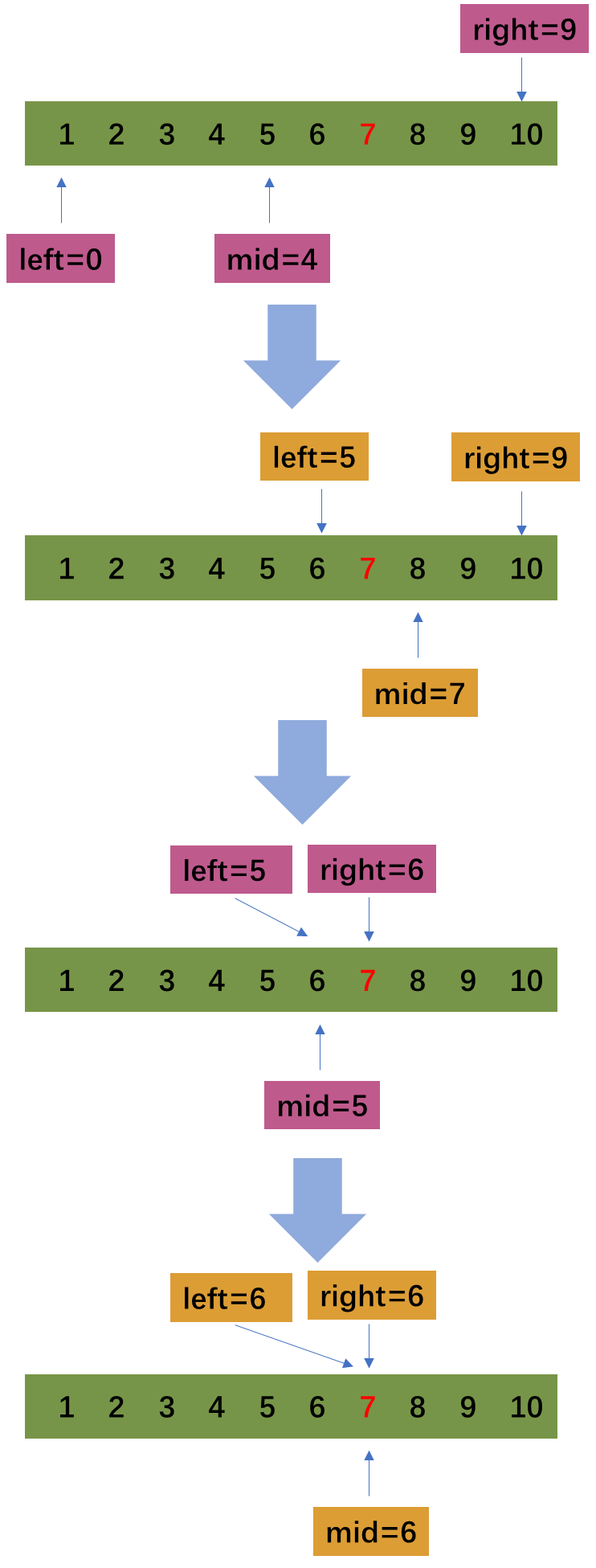

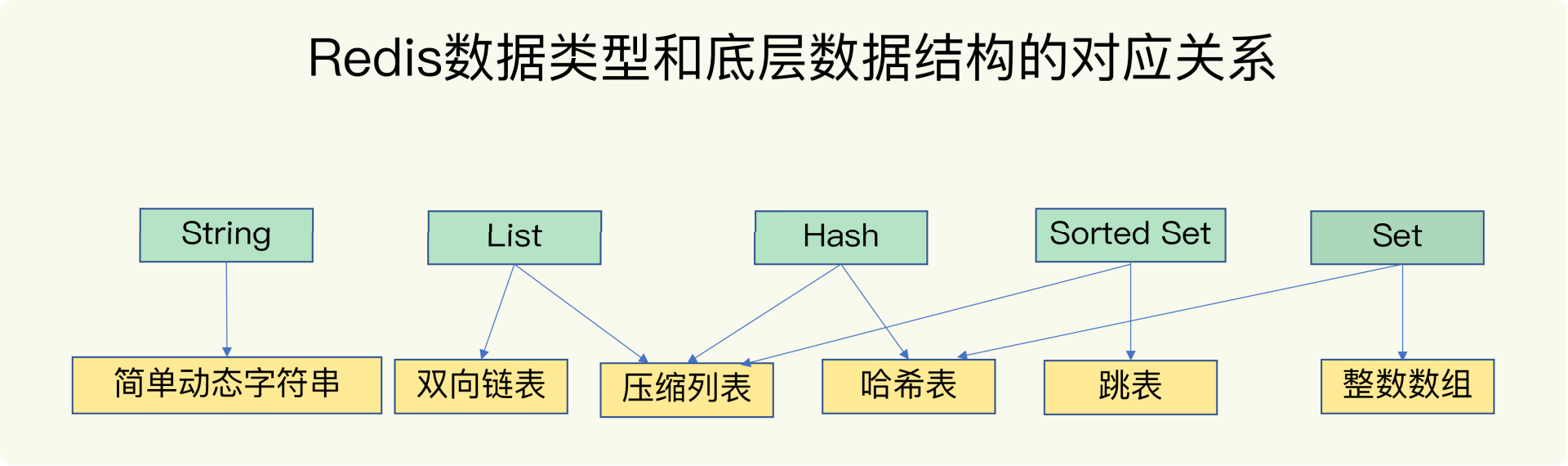

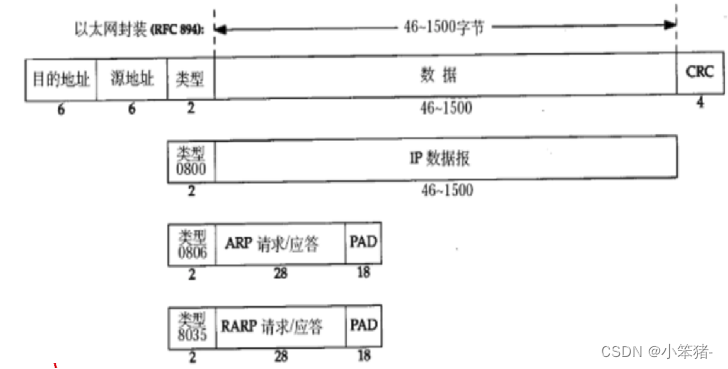

指令集设计:首先确定CPU支持的指令集架构,包括指令格式、寄存器组织、地址模式等。常见的指令包括算术逻辑运算指令(加法、减法、与、或等)、数据传输指令(加载、存储)、控制指令(跳转、分支)、以及其他特定功能的指令。

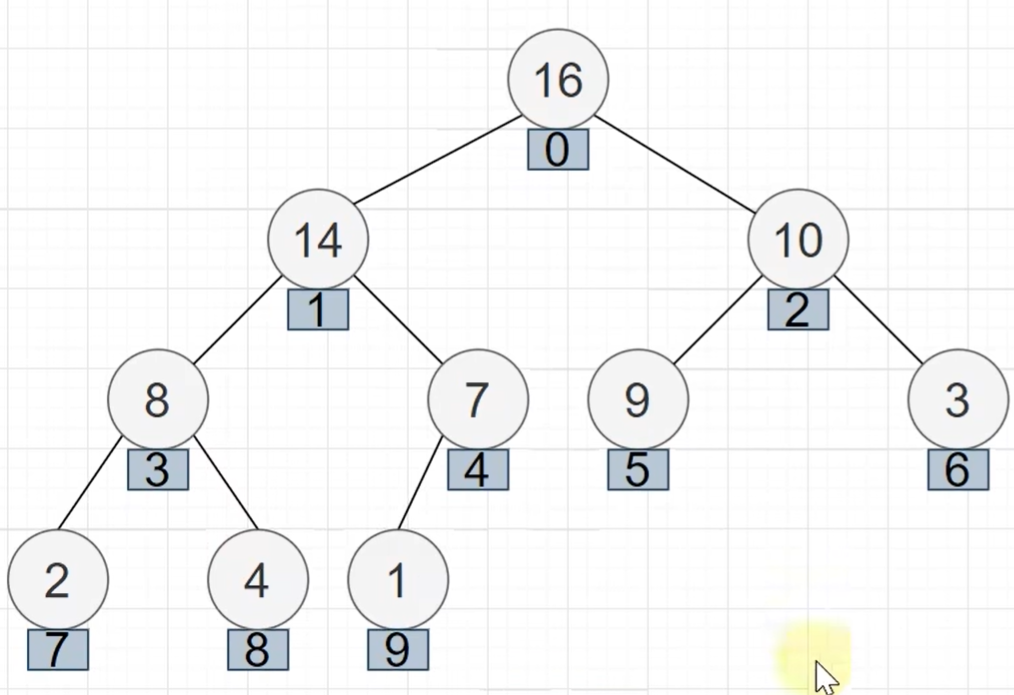

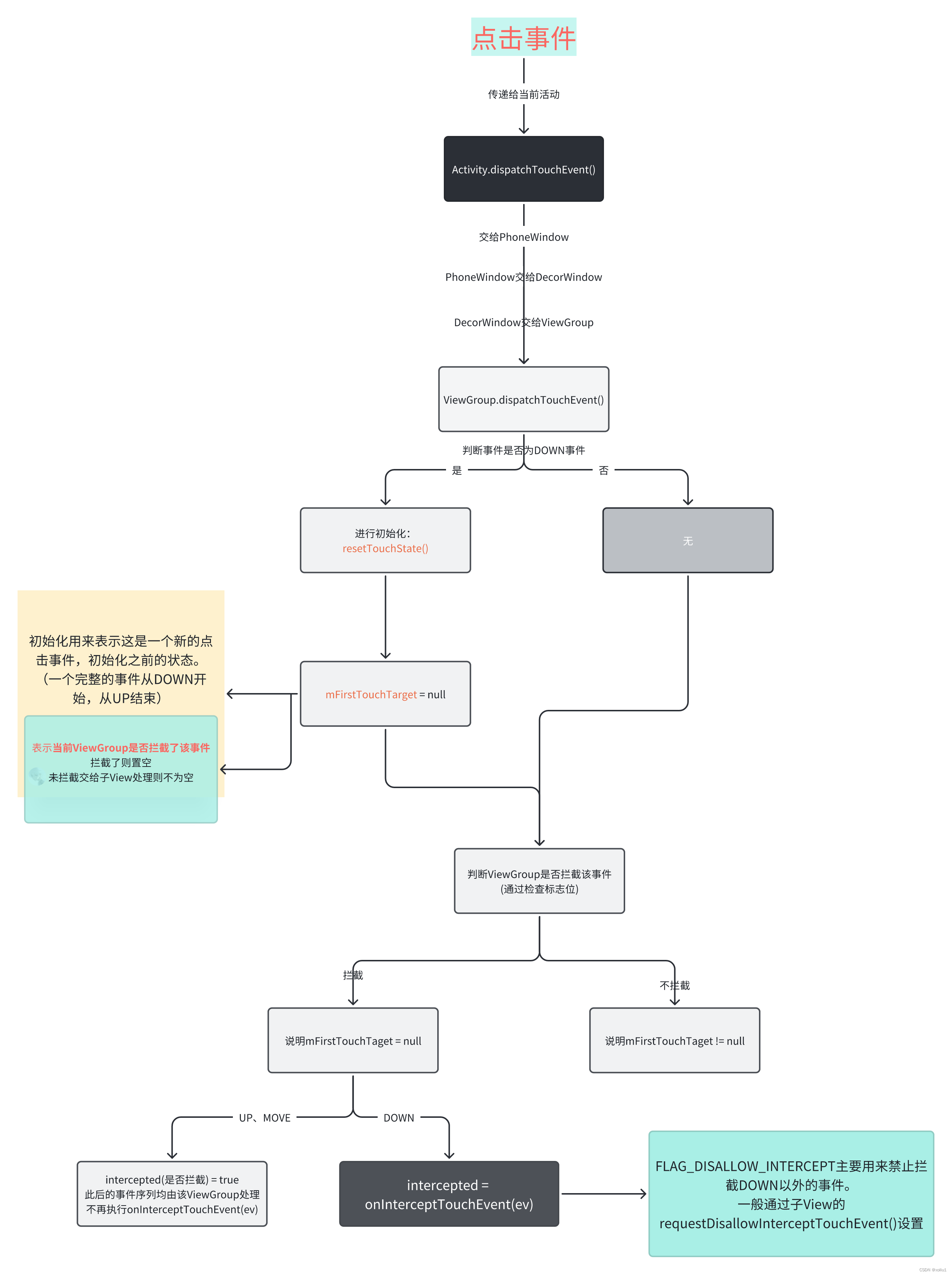

CPU结构设计:根据设计的指令集,设计CPU的整体结构,包括运算单元、寄存器文件、指令译码单元、控制单元等。确定CPU的数据通路和控制信号传输路径,并设计相应的模块。

编写Verilog代码:根据CPU结构设计,编写对应的Verilog代码,包括各个模块的实现以及模拟器。

功能验证:通过编写Testbench对CPU进行功能验证,测试各种指令的执行、数据传输等功能是否正确。可以通过仿真工具验证CPU的功能。

时序验证:设计Testbench对CPU进行时序验证,测试CPU在不同时钟频率和不同输入信号的情况下能否正常工作。

集成调试:将CPU的各个模块集成在一起,进行整体功能验证和调试。确保所有模块协同工作正常。

性能优化:根据需要对CPU进行性能优化,包括减少延迟、减小面积、降低功耗等