说明

由于Intel Agilex® 7 FPGA I 系列收发器-SoC 开发套件的时钟控制器 GUI 存在问题,当您需要配置芯片 Si5332 的 OUT1 时钟频率时,您可能会发现 F-tile Serial Lite IV 英特尔® FPGA IP设计示例失败。这是因为此 Si5332 GUI 存在问题;无法准确配置 OUT1 频率。

如果您使用 Intel Agilex® 7 FPGA 系列收发器-SoC 开发套件,您的设计使用 Si5332 OUT1 时钟,并且需要更改默认频率 166.66 MHz,则所有 Intel Agilex® 7 F-tile IP 设计都可能会出现类似的故障。

解决方法

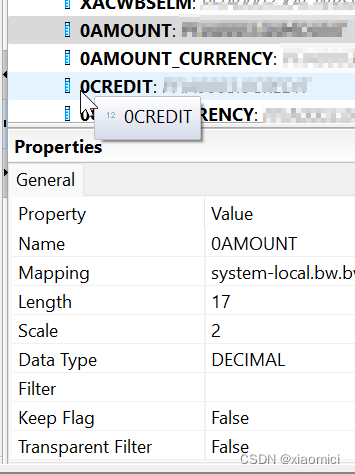

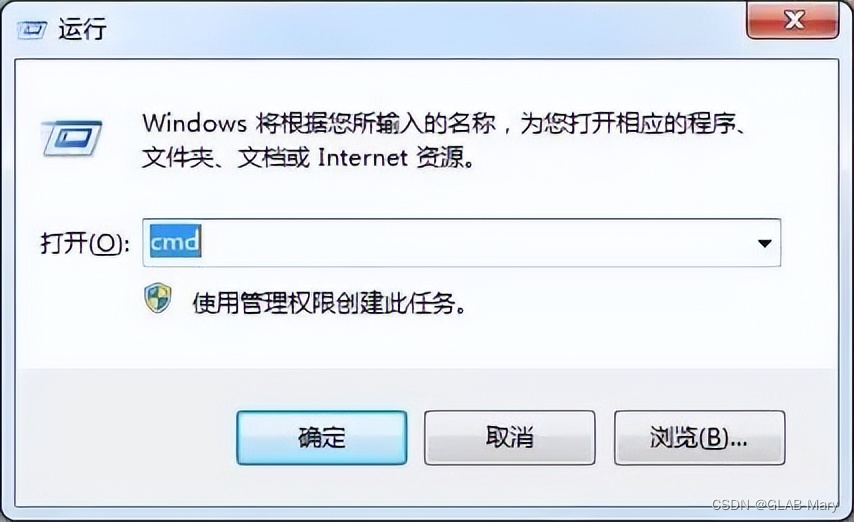

要变通解决此问题,应避免直接使用“设置”按钮设置

OUT1 频率。您需要使用“导入”按钮准确设置 Si5332 OUT1 时钟频率。

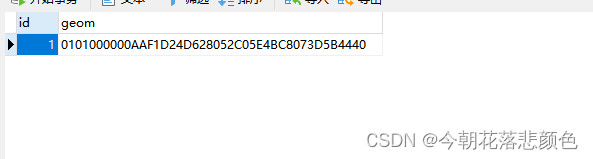

导入函数 txt 文件可以使用 ClockBuilder Pro 软件导出。附上示例 si5332 项目和 si5332-project.txt 文件以供参考。