MOS的电压关系

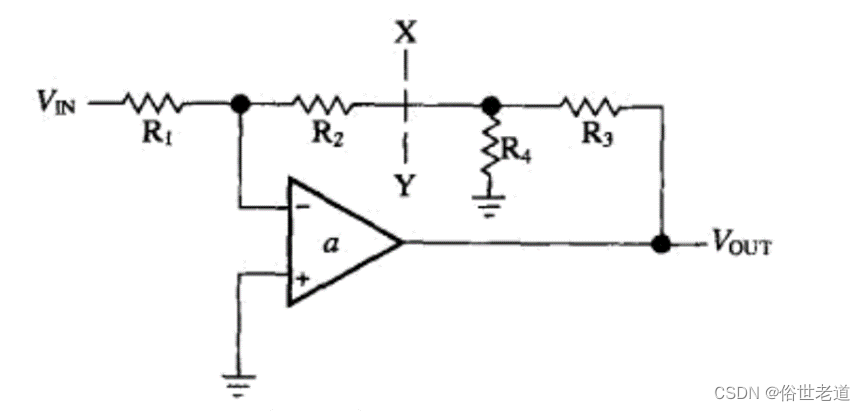

在运放设计静态工作电压时要利用vod来确定,已知MOS的VTH,工作在饱和区,再假设管子的Vdsat,根据下式就能由G求S或由S求G:

上述关系可以用来确定电路的所有电压工作点,因为一旦Vod确定,就能由G求S或由S求G。个人理解电路节点电压应该都是由Vod和VG来确定,管子的VD并不直接靠自己的参数确定而是连接在其上方N管的源端或者连接在其下方P管的源来被确定,毕竟谁的漏端又不是别人的源端呢。

在运放设计考虑某点的电压变化范围时,管子饱和的条件,用于判断管子容易进线性的程度和漏端的摆幅限制:

也就说对于NMOS,漏越高越容易饱和,所以漏只有下限就是不能比栅端低于一个VTH;对于PMOS,漏越低越容易饱和,所以漏只有上限不能比栅高多于一个|VTH|。

举例

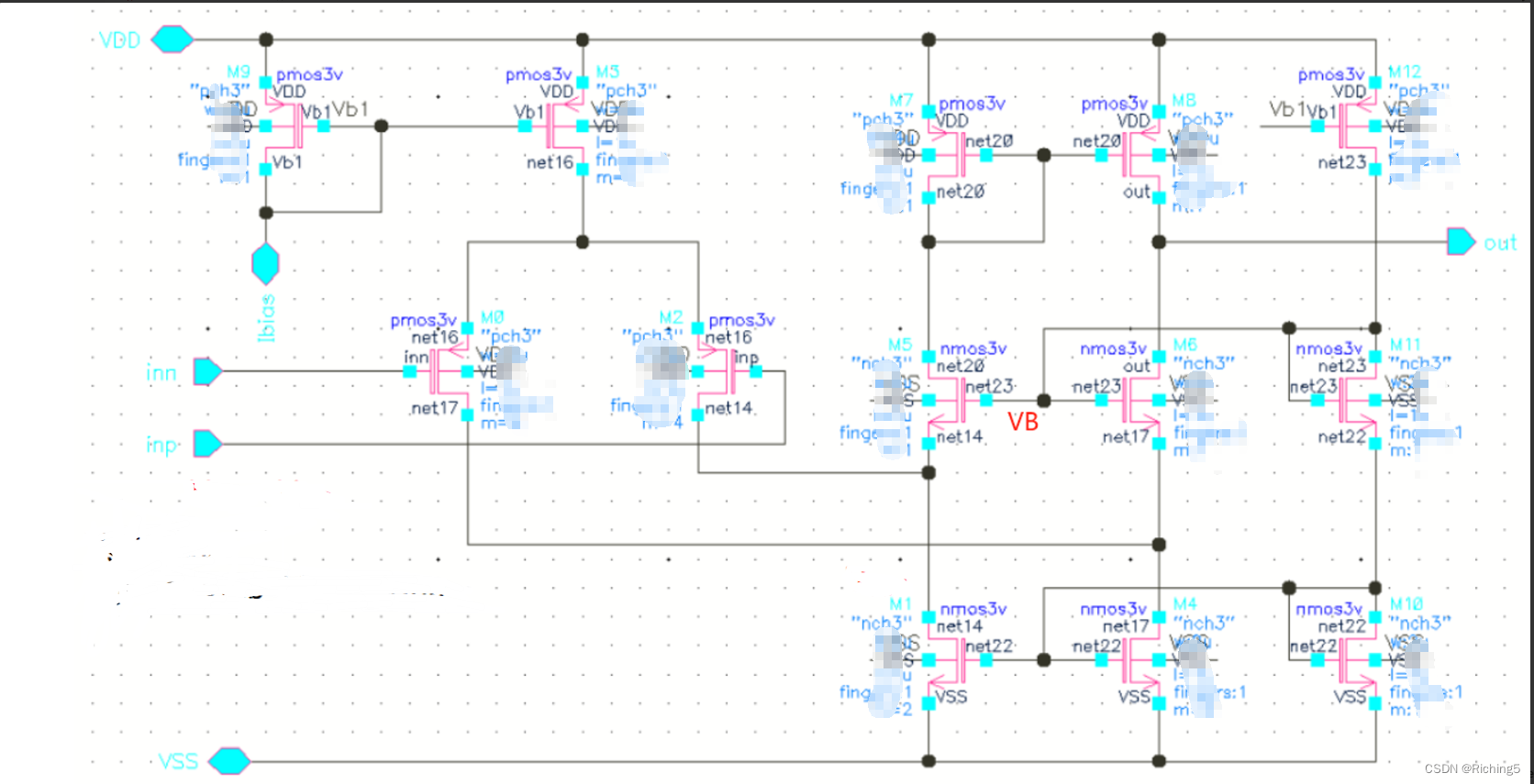

利用上述关系求解共模输入范围

共模输入范围下限:当输入共模逐渐下降时,如果其他地方不改变,输入对管的漏端电压是由共栅管的栅极决定而固定,当输入共模下降过多时会使输入对管进入线性区。考虑输入对管要饱和,所以要关注输入对管D端的电压情况,这里存在两种情况:从共栅管来考虑VD=VB-Vod5-VTN,所以vincm>VD0-|VTP|=VB-Vod5-VTN-|VTP|;从N电流镜考虑,VD0>Vod1,所以vincm>VD0-|VTP|=Vod1-|VTP|。

共模输入范围的上限:当输入共模逐渐上升时,如果其他地方不改变,输入对管的源端电压是根据输入对管的Vod来变化,所以也逐渐上升随着源端电压上升,M3会进入线性区,所以共模输入范围的上限是考虑M3饱和,vincm<VDD-Vod3-Vod0-|VTP|。