系列文章

数值(整数,实数,字符串)与数据类型(wire、reg、mem、parameter)

运算符

数据流建模

行为级建模

结构化建模

组合电路的设计和时序电路的设计

有限状态机的定义和分类

期末复习——数字逻辑电路分为哪两类?它们各自的特点是什么?

期末复习——VerilogHDL描述数字逻辑电路的建模方式有哪三种?它们的特点是?

期末复习——解释下列名词(FPGA、ASIC、IP、RTL、EDA、HDL、FSM)

期末复习——简要说明仿真时阻塞赋值和非阻塞赋值的区别。always语句和initial语句的关键区别是什么?能否相互嵌套?

期末复习——设计带进位输入和输出的8位全加器,包括测试模块

期末复习——举重比赛有三名裁判,当运动员将杠铃举起后,须有两名或两名以上裁判认可,方可判定试举成功,若用A、B、C分别代表三名裁判的意见输入,同意为1,否定为0;F为裁判结果输出

期末复习——设计一个带异步复位端且高电平有效的32分频电路

期末复习——设计带异步清零且高电平有效的4位循环移位寄存器

下面用Moore状态机实现。即此态由现态和输入决定,输出仅由现态决定。

s0:0

s1:1

s2:11

s3:110

s4:1101

s5:11011

总共有六种状态。

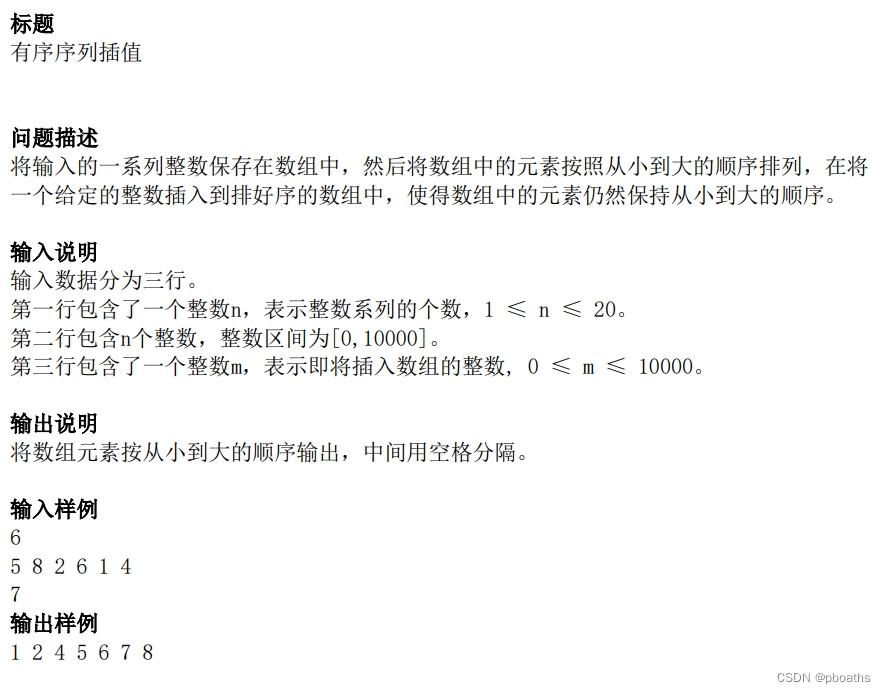

module moore(clk,reset,din,dout);

input clk,reset,din;

output reg dout;

//状态编码

reg[2:0] ps,ns;

parameter s0=3'b000,s1=3'b001,s2=3'b010,s3=3'b011,s4=3'b100;

//状态寄存器模块

always @(posedge clk)

begin

if (clr == 0) ps<=s0;

else ps<=ns;

end

//次态模块

always @(*)

begin

case(ps)

p0: if(din==1) ns=s1;

else ns=s0;

p1: if(din==1) ns=s2;

else ns=s0;

p2: if(din==0) ns=s3;

else ns=s2;

p3: if(din==1) ns=s4;

else ns=s0;

p4: if(din==1) ns=s5;

else ns=s0;

p5: if(din==1) ns=s1;

else ns=s0;

default: ns=s0;

endcase

end

//输出模块

always @(*)

begin

if(ps==s5) dout=1;

else dout=0;

end

endmodule