一、概述

Verilog 是一种用于数字逻辑电路设计的硬件描述语言,可以用来进行数字电路的仿真验证、时序分析、逻辑综合。

既是一种 行为级(可用于电路的功能描述) 描述语言又是一种 结构性(可用于元器件及其之间的连接) 描述语言。

二、Verilog模块基本概念

模块(block)是Verilog的基本单位,除了编译指令,其他的所有的设计代码都必须放在一个或多个模块中。

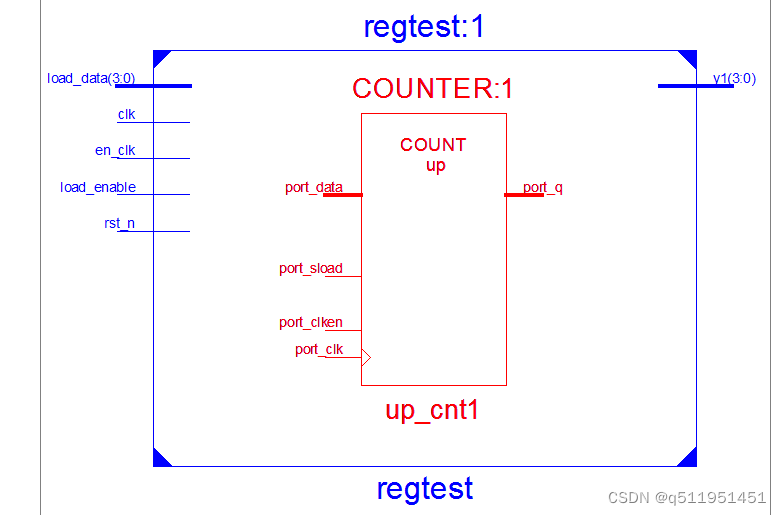

一个模块内部可以使用其他模块,称为实例。上层模块可以引用底层任意层次模块的变量,模块内部可以包含若干个 “块”。

三、Verilog模块总结

Verilog中的标示符可以是任意一组字母、数字、$符号和下划线符号的组合,但标示符的第一个字符必须是字母或者下划线。标示符区分大小写Verilog程序是有模块组成的,每个模块嵌套在module和endmodule声明语句中。模块是可以进行层次嵌套的每个

Verilog源文件中只准有一个顶层模块,其他为子模块每个模块要进行端口定义,并说明输入输出端口,然后对模块的功能进行行为逻辑描述

程序书写格式自由,一行可以写几个语句,一个语句可以分几行写

除了endmodule语句,begin…end语句,fork…join语句外,每个语句和数据定义的最后必须有分号

可用

/*...*/和//...对程序的任何部分做注释 ,加上必要的注释,以增强程序的可度性和可维护性。

四、Verilog用于模块的测试

检查程序的功能是否正确要求:

需要有测试激励信号输入到被测模块

需要记录被测模块的输出信号

需要把用功能和行为描述的Verilog模块转换为门级电路互连的电路结构(综合)

需要对已经转换为门级电路结构的逻辑进行测试(门级电路仿真)

需要对布局布线后的电路结构进行测试 (布局布线后仿真)

何为仿真?为何要仿真?

仿真是对电路模块进行动态的全面测试,通过观测被测试模块的输出信号是否符合要求可以调试和验证逻辑系统的设计和结构是否准确,并发现问题及时修改。

仿真可以在几个层面上进行?每个层面的仿真有什么意义?

仿真有:前(RTL)仿真,逻辑网表仿真,门级仿真和布线后仿真;

前仿真:前(RTL)仿真,逻辑网表仿真,门级仿真;可以调试和验证逻辑系统的设计和结构准确与否,并发现问题及时修改。

布线后仿真:分析设计模块运行是否正常;

模块的结构

Verilog 的基本设计单元是"模块(block)"

verilog 模块的结构由在module和endmodule关键字之间的4个主要部分组成:

module block1(a,b,c,d); //端口定义

input a,b,c;

output d; //I/O声明

wire x; //信号类型声明

assign d = a | x;

assign x = (b &~c); //功能描述

endmodule

五、逻辑功能的定义

在Verilog中有3种方法可以描述电路的逻辑功能:

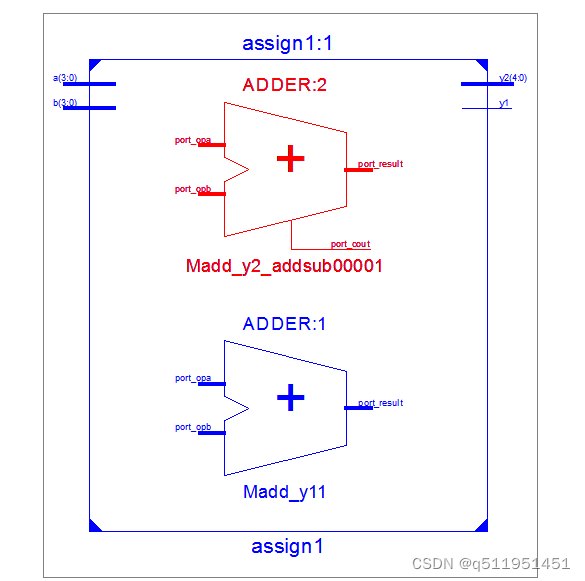

1. 用assign语句(连续赋值语句,常用于描述组合逻辑)

assign x = (b &~c);

2.用元件例化(instance 门元件例化)

and(门元件关键字) u_and3(例化原件名)(f,a,b,c);

注1:元件例化即是调用Verilog提供的元件;

注2:元件例化包括门元件例化和模块元件例化;

注3:每个实例元件的名字必须唯一,以避免与其他调用元件的实例相混淆;

注4:例化元件名也可以省略。

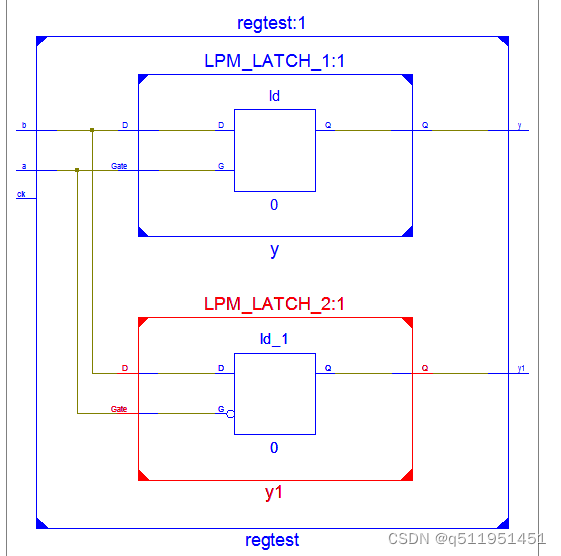

3.用"always"块语句

always @(posedge clk) //当时钟上升沿到来时执行一遍块内语句

begin

if(load)

out = data; //同步预置数据

else

out = data + cin +1; //加1计数

end

注1:”always“块语句常用于描述时序逻辑,也可描述组合逻辑;

注2:”always“块可用多种手段来表达逻辑关系,如用if…else语句或case语句;

注3:”always“块语句与assign语句是并发执行的,assign语句一定要放在”always“块语句之外。

模块结构模板:

module <顶层模块名> (<输入输出端口列表>);

output 输出端口列表;

input 输入端口列表;

//更推荐

module <顶层模块名> (

output 输出端口列表,

input 输入端口列表

);

//1.使用assign语句定义逻辑功能

wire 结果信号名;

assign <结果信号名> =表达式;

//2.使用always块定义逻辑功能

always@(<敏感信号表

begin

//过程赋值语句

//if语句

//case语句

//while,repeat,for循环

//task,function调用

end

//3.文件例化

<module_name > <instance_name>(<port_list>);//模块元件例化

<gate_type_keyword > <instance_name>(<port_list>);//门元件例化

endmodule

六、标示符

任何用Verilog语言描述的东西都可以通过其名字来识别,这个名字被称为标示符;

如源文件名,模块名,端口名,变量名,常量名,实例名等

标示符可由字母,数字,$和下划线组成,但第一个字符必须是字母或下划线,不能是$和数字

在Verilog中标示符是区分大小写的,且不能与关键字同名。

![[<span style='color:red;'>Verilog</span>] <span style='color:red;'>Verilog</span> <span style='color:red;'>基本</span>格式和<span style='color:red;'>语法</span>](https://img-blog.csdnimg.cn/direct/2310f282f3e14ab9823d51eba1b8cab8.png)