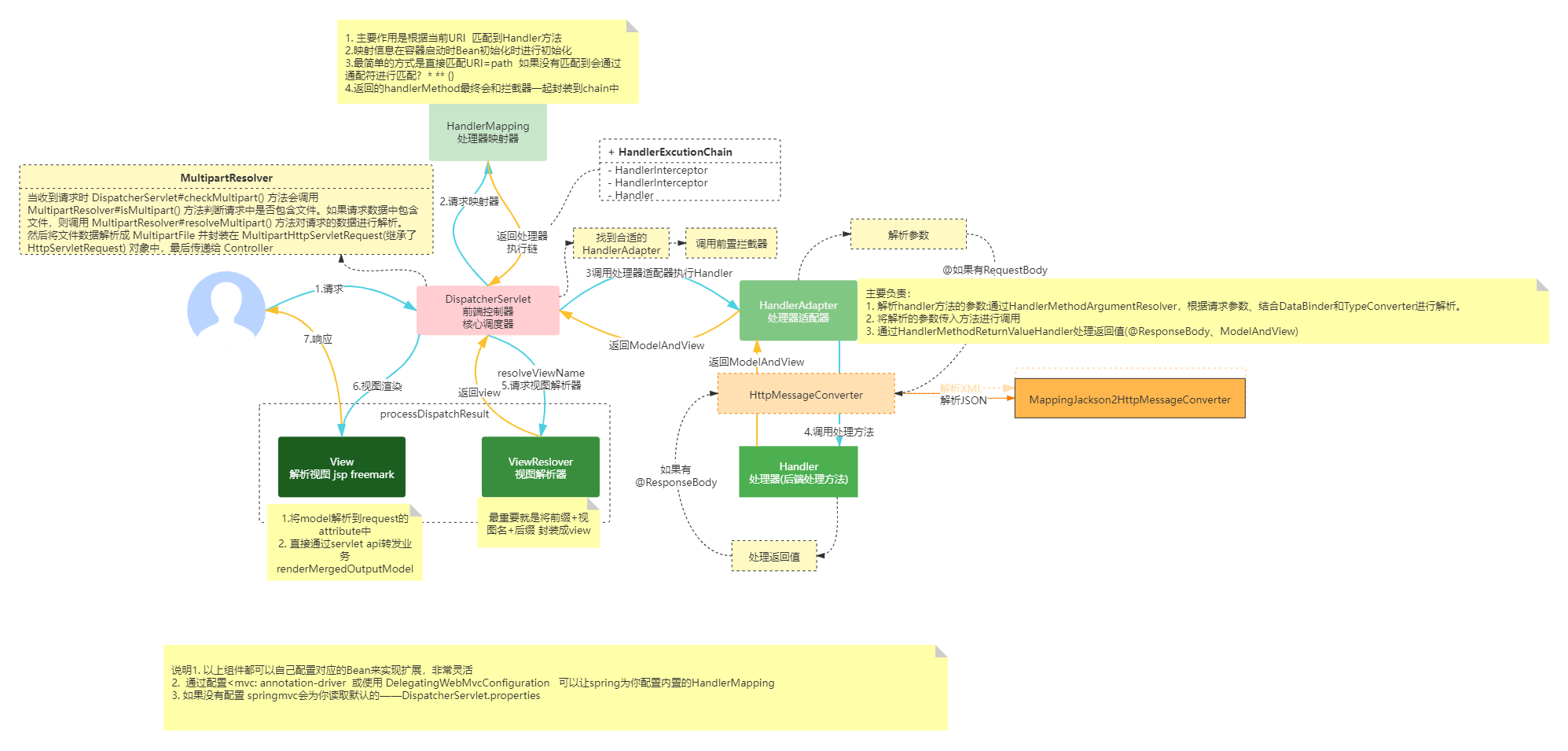

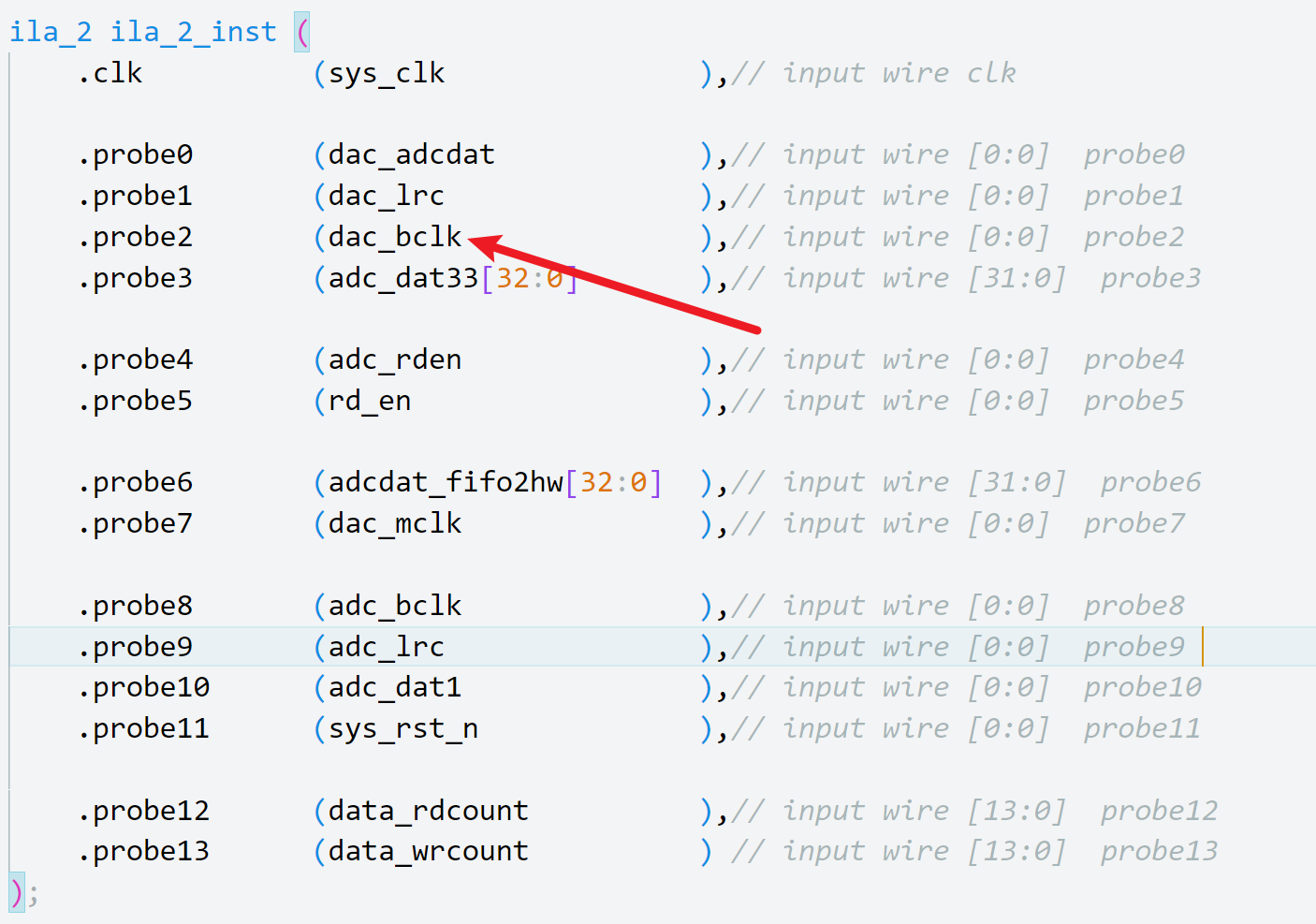

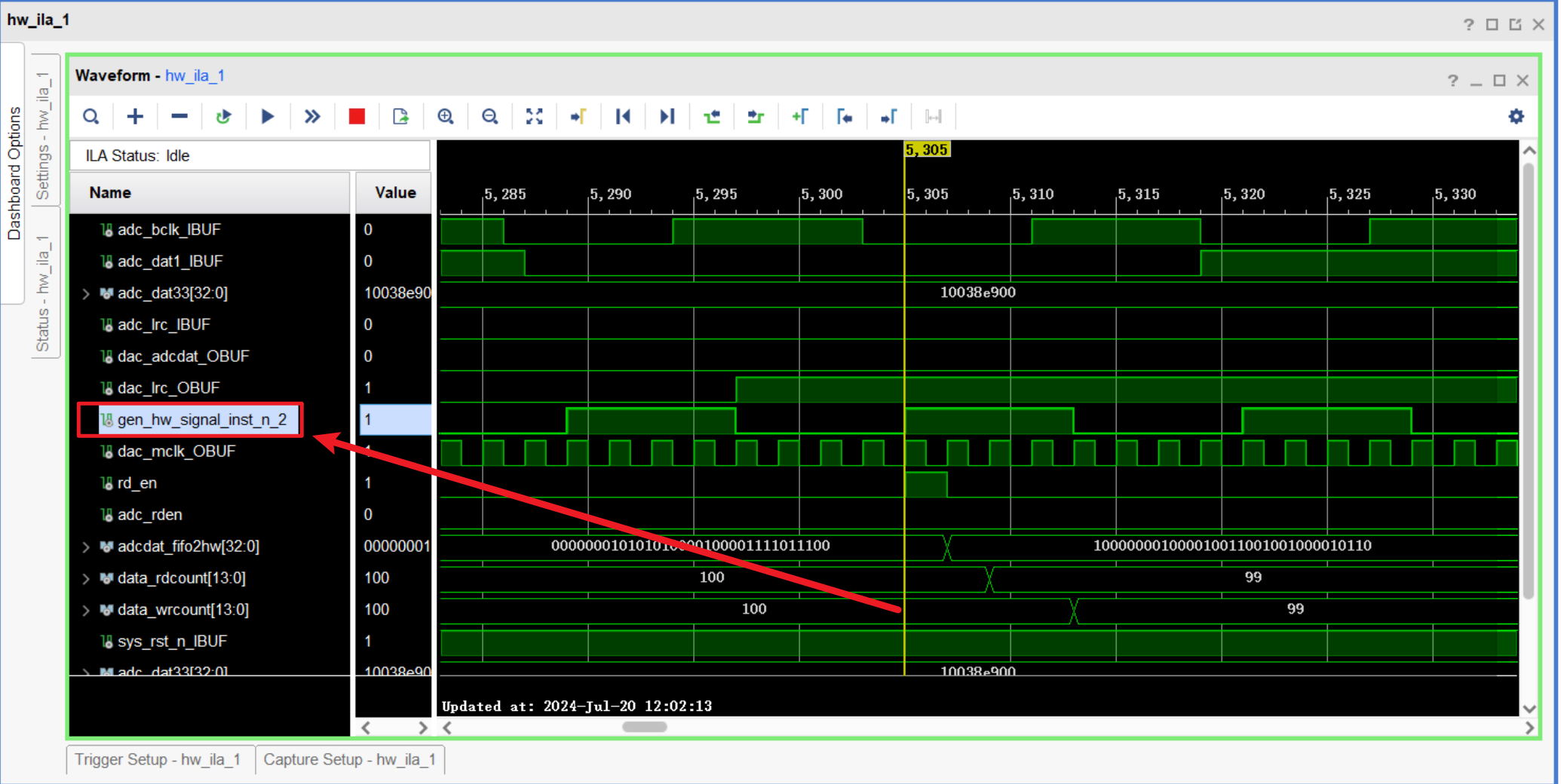

1. 在代码里面定义的ILA的变量名称与波形抓取界面的不一致

- 问题描述

:::

2. 直接从其他的播放声音的平台放音乐没问题,但是从AU里面生成的2kHz的正弦波放不出声音

- 好像和ILA的例化信号有关,例化ILA信号的驱动时钟信号频率没有内部的其他信号的频率高

- 我把ila例化模块去掉后,AU播放的2kHz的正弦波也能正常播放

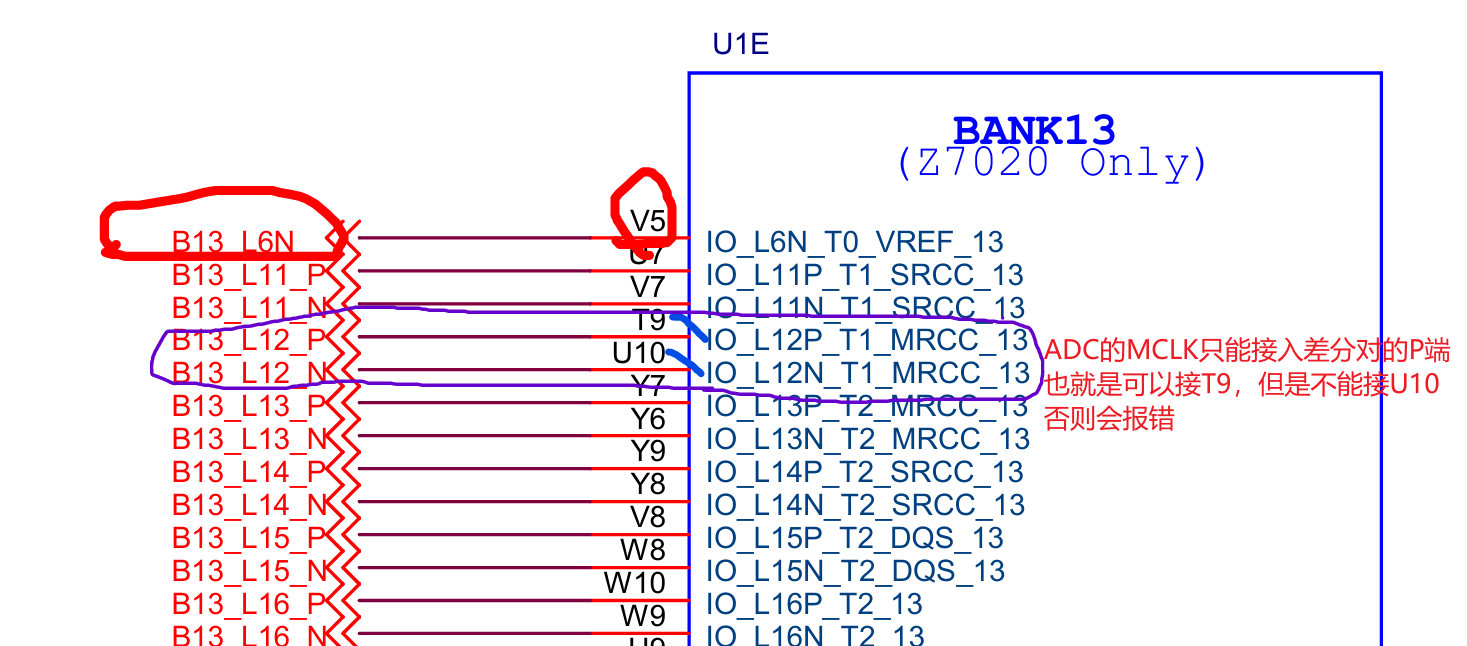

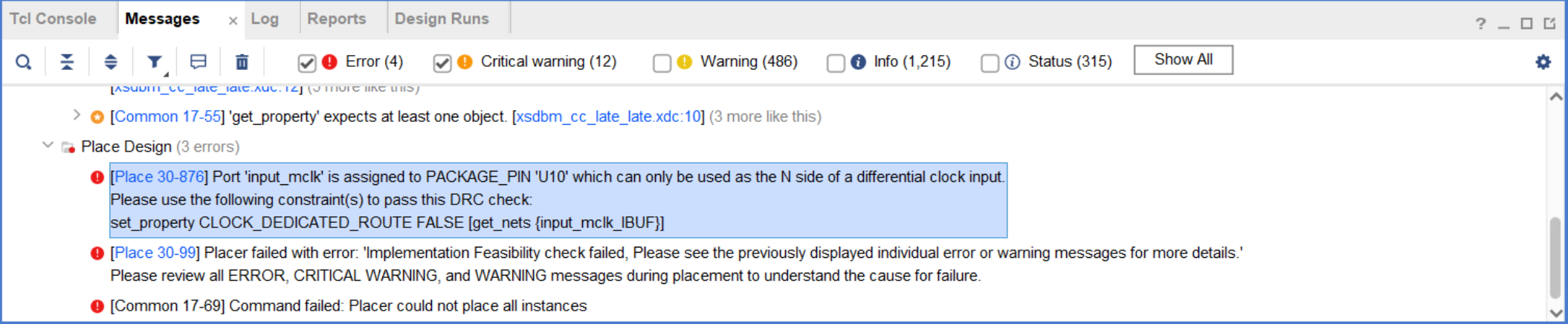

3. input_mclk(从音频ADC引入FPGA的引脚)只能绑定时钟专用引脚的同向端(P端),不能使用反向端(N端),否则会报错,不知道为什么

:::

修改到T9就正常了

对于输入FPGA的时钟信号,要从FPGA的时钟资源分配的引脚传入FPGA

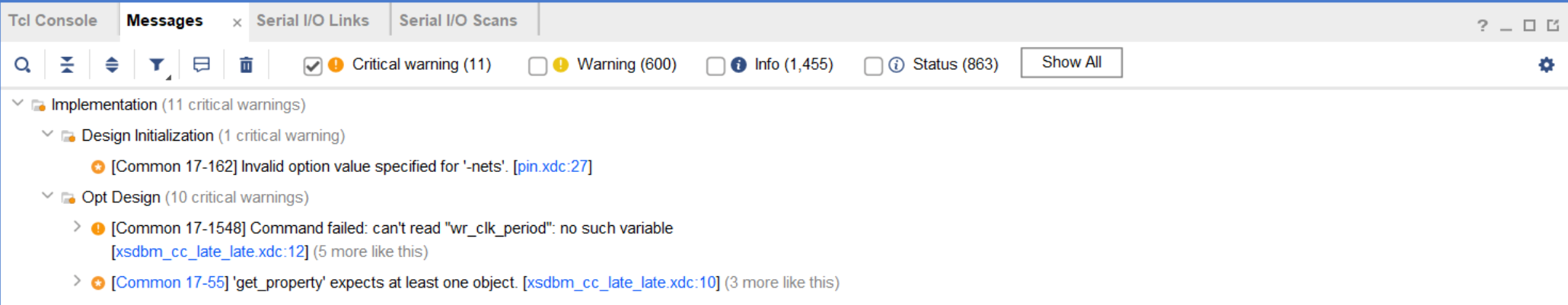

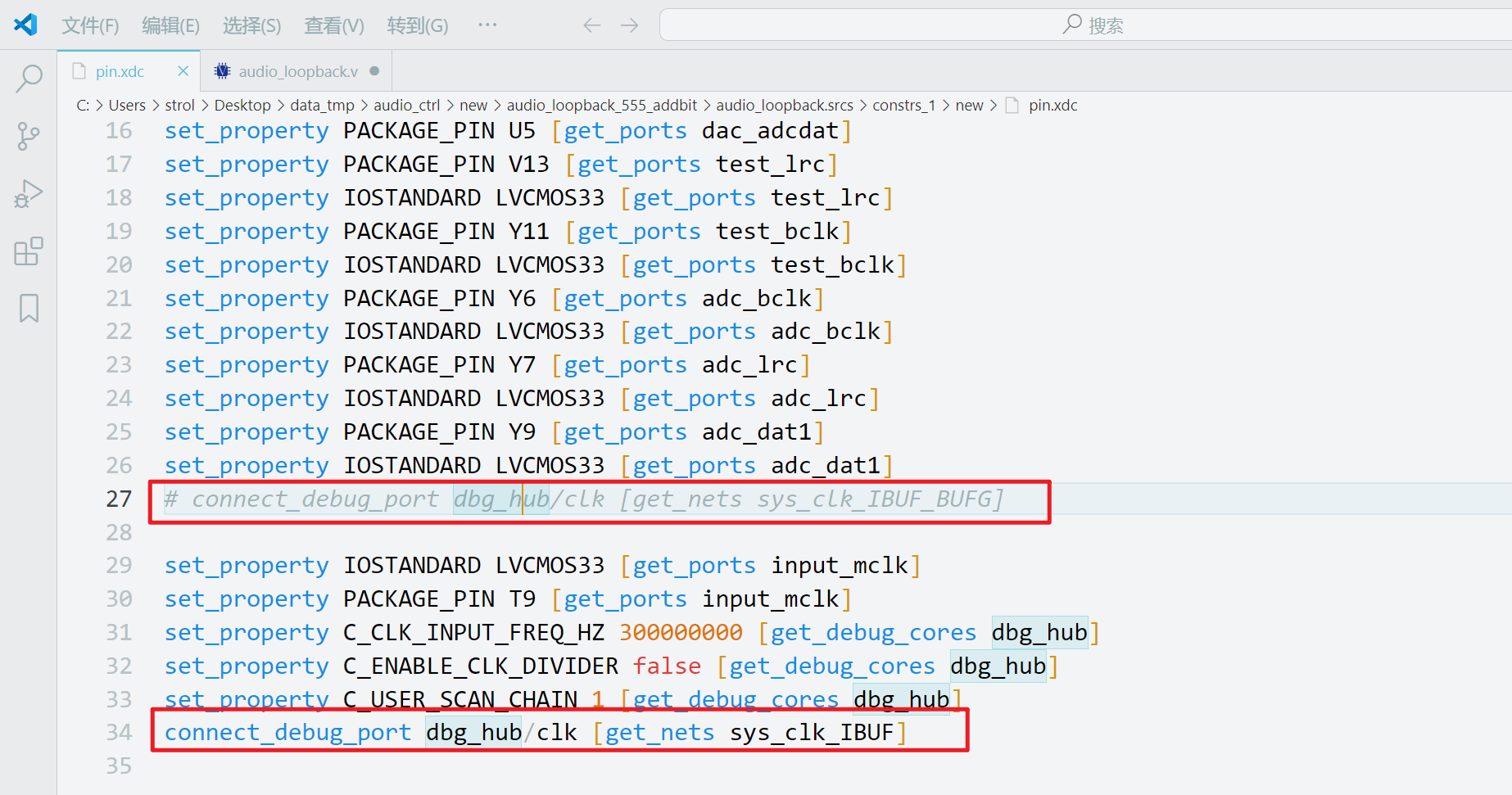

4. Invalid option value specified for ‘-nets‘

出现这种问题的原因是ILA更新了,但是约束没有自动更新,导致找不着dbg_hub的时钟,而这种时钟名是软件生成的,每次都不一样,可以在XDC文件中注释或删除掉dbg_hub的相约束。

然后implement下打开IO,再然后取消一个IO的锁定并重新勾上之后按CTRL+S保存,这时会生成新的约束,如下图,然后重新编译工程~

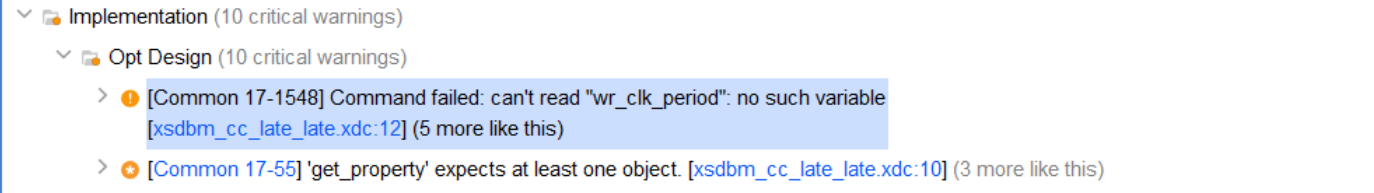

5. [Common 17-1548] Command failed: can’t read “wr_clk_period”: no such variable

- 出现原因:因为Ila中检测的某些信号,时钟频率可能高于ila的clk,只有使用ila或system ila选择native时才可能会出现这种错误,

-

- 解决方法:在.xdc中添加

create_clock -period 16 -name clk -add [get_ports clk_0],其中,clk_0是外部时钟,clk是ila的时钟。16ns是ila检测信号中最高时钟频率的周期数,即ila的时钟接连到检测信号中最高的时钟频率。

- 解决方法:在.xdc中添加