1:信号需要数模转换吗,需要加数模转换高速接口,或者外接配套器件?

2:芯片的输入,输出是什么?逻辑如何处理,对应业务功能有哪些?

3:明确业务功能,梳理出要处理的数据,信息!

4:绘制方案流程图,书写方案文档,详细的设计开发文档;

5:结合4,反复绘制迭代微架构图,反复优化方案文档,明确关键信号的打拍节点,复杂的逻辑分到不同的周期,,每一个时钟周期做了什么!!,结合工作频率,梳理关键的组合逻辑级数。

微架构图中,明确表示出信号处理,是组合逻辑,还是流水线结构,又或者是状态机实现?还是通用的算法硬件逻辑实现?有没有跨时钟部分,如何处理?

详细梳理出实现的过程;

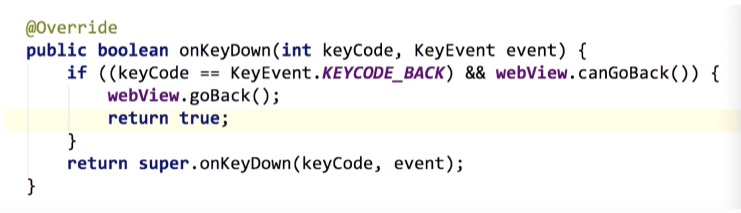

6:编码过程,结合微架构图等,对功能模块编码实现,注意使用良好易读的编码风格;

7:编码完成后,代码编译,语法检查,使用vcs,lint,cdc 等确保代码基本无问题;

8:初版代码整合,开发设计人员,编写简单的testbench 进行初步自测;无误后交付验证人员;

——————————

8-1:进行各种质量活动,优化代码质量,确认关键跨时钟是否正确?复杂逻辑状态机场景是否考虑全面?fifo等流控,反压路径得传输时延和fifo深度是否相匹配?时钟域划分是否合理,等等;

后端结合初版代码,简单的综合,布局布线,对于占用较大的tcam,ram,寄存器堆等占用面积资源较大的部分初步摆放,发现其他逻辑部分的时序问题!!!

9:验证,后端提出的问题,迭代,修改代码,,可能是功能的修改,也可能是时序的修改;

时序优化主要方法:

对于建立时间违例的解决办法:

1) 降低时钟频率,即增大时钟周期

2) 再时钟路径上加缓冲器(buffer) ,让时钟晚到来。

3) 更换具有更小器件延迟的触发器。

4) 组合逻辑优化或插入流水线,缩短关键路径。

对于保持时间违例的解决办法:

1) 在数据路径上插 buffer

2) 更换具有更大器件延迟的触发器

3) 优化时钟路径,让时钟更早到来。

*可以看出,保持时间和建立时间基本是相反的。但是保持时间与时钟周期无关

10:接下来,代码基本没问题了,验证也初步验证过了,时序也ok了,

开始FPGA原型验证,开始加速器验证;

验证人员的验证还是拉波形什么的在软件层级模拟硬件逻辑,不够完整,这就需要FPGA和加速器了,这里会吧软件人员制作的芯片驱动软件加载到对应的FPGA和加速器工具上,系统性的验证FPGA的功能;

11:这里其实和10 几乎是同步进行,甚至在 6~8阶段也会做,那就是前端的代码质量检查,代码优化,如无复位寄存器修改,代码门控信号添加,DFT添加测试逻辑等等;

12:后端进行各种检查,形式验证,逻辑验证等等;;;

经过测试没问题,就流片了!~~~~~~~~~~~